Werbung

Neben der Vorstellung der ersten EPYC-Prozessoren mit 3D V-Cache stellt AMD heute mit der Instinct MI200 die nächste Generation des dedizierten GPU-Beschleunigers für das Rechenzentrum vor. Vor genau einem Jahr wurde die Instinct MI100 auf Basis der CDNA-Architektur vorgestellt. Analog zu RDNA (Radeon DNA) ist die CDNA-Architektur (Compute DNA) explizit für den Einsatz im Rechenzentrum ausgelegt und nicht mehr nur ein Ableger mit einigen wenigen Anpassungen.

Mit der CDNA-2-Architektur, vor allem aber der Fertigung und dem Packaging der Instinct MI200 schaltet AMD nun in den nächsten Gang und möchte bei den GPU-Beschleunigern zum Angriff blasen. Genauer gesagt handelt es sich nicht um ein einzelnes Modell, sondern gleich um eine ganze Serie an Beschleunigern, die unterschiedlich aufgebaut und ausgelegt sind.

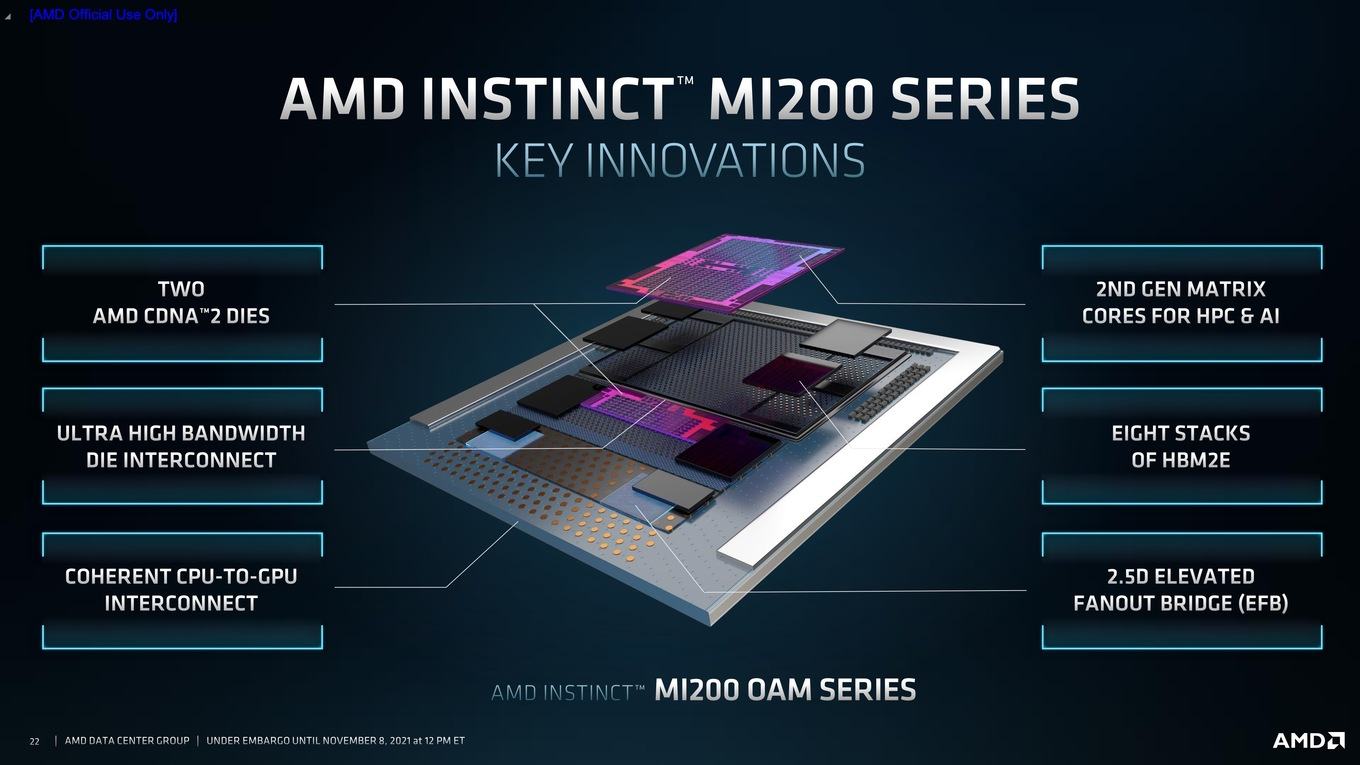

Für das Spitzenmodell kommen bis zu 58 Milliarden Transistoren zum Einsatz, die auf zwei Chips aufgeteilt in 6 nm gefertigt werden. 220 Compute Units, 880 sogenannte Matrix Cores und bis zu 128 GB HBM2E mit einer Speicherbandbreite von 3,2 TB/s sind nur die wichtigsten technischen Daten.

Um seine HPC-Ambitionen hier mehr und mehr zu unterstreichen, bietet AMD die Instinct-MI200-Serie erstmals neben einer PCI-Express-Variante als OCP Accelerator Module (OAM) an. Später soll es eine Instinct MI210 als PCI-Express-Variante geben.

Aus technischer Sicht das Highlight soll das Packaging mittels 2.5D Elevated Fanout Bridge (EFB) sein. Damit umschreibt AMD die Tatsache, dass für das Spitzenmodell eben zwei Chips zusammengefasst werden – bei den GPUs bisher ein Novum, bei den Prozessoren macht uns AMD dies bereits seit einigen Jahren vor.

Aber kommen wir zu den technischen Daten der Instinct-MI200-Serie:

| Instinct MI100 | Instinct MI250 | Instinct MI250X | A100 80GB SXM | |

| Architektur | CDNA | CDNA 2 | CDNA 2 | Ampere |

| Fertigung | 7 nm | 6 nm | 6 nm | 7 nm |

| Transistoren | - | 58 Milliarden | 58 Milliarden | 54 Milliarden |

| Chipgröße | - | - | - | 826 mm² |

| FP64-Einheiten | 7.680 | 13.312 | 14.080 | 3.456 |

| FP32-Einheiten | 15.360 | 13.312 | 14.080 | 6.912 |

| Matrix / Tensor Cores | - | 832 | 880 | 432 |

| FP64-Rechenleistung (TFLOPS) | 11,5 | 45,3 | 47,9 | 9,7 |

| Peak FP64-Rechenleistung (TFLOPS) | 11,5 | 90,5 | 95,7 | 19,5 |

| FP32-Rechenleistung (TFLOPS) | 23,1 | 45,3 | 47,9 | 19,5 |

| Peak FP32-Rechenleistung (TFLOPS) | 23,1 | 90,5 | 95,7 | 156 |

| FP16-Rechenleistung (TFLOPS) | 184,6 | 362,1 | 383 | 312 / 624 |

| Bfloat16-Rechenleistung (TFLOPS) | 92,3 | 362,1 | 383 | 312 / 624 |

| Speicher | HBM2 | HBM2E | HBM2E | HBM2 |

| Speicherkapazität | 32 GB | 128 GB | 128 GB | 80 GB |

| Speicherinterface | 4.096 Bit | 8.192 Bit | 8.192 Bit | 5.120 Bit |

| Speicherbandbreite | 1,23 TB/s | 3,2 TB/s | 3,2 TB/s | 2 TB/s |

| TDP | 300 W | 500 / 560 W | 500 / 560 W | 400 / 500 W |

| PCIe | 4.0 | 4.0 | 4.0 | 4.0 |

| Interconnect | Infinity Fabric 3x 267 GB/s | Infinity Fabric 6 Links | Infinity Fabric 8 Links | NVLink 600 GB/s |

Die Instinct MI250 und MI250X verwenden beide die volle Ausbaustufe über zwei GPUs, die sogenannten Graphics Compute Dies (GCD) mit jeweils 29 Milliarden Transistoren. Bei der Instinct MI250 sind pro Chip 104 Compute Units (CUs) aktiv (insgesamt 208), bei der Instinct MI250X sind es jeweils 110 CUs (ingesamt also 220). Der Takt der GPUs soll bei 1.700 MHz liegen.

Pro CU in der CDNA-2-Architektur vorhanden sind vier Matrix Cores und 64 Shadereinheiten (4x 16-wide SIMD). Jeder Graphics Compute Die (GCP) verfügt theoretisch über 112 physikalisch vorhandene CUs, von denen aber nur maximal 110 bei der Instinct MI250X aktiv sind.

Die eigentlichen CUs sind Derivate der vorherigen GCN-Architektur. Sie können Wavefronts mit bis zu 64 Working Units ausführen. Die Register und die gesamte Pipeline sind für Scalar-, Vektor- und Matrix-Daten optimiert. Für Matrix-Berechnungen ist eine dedizierter Datenpfad vorhanden, so dass hier auf die Eigenheiten der schwach besetzten Matrizen und die Wiederverwendung bestimmter Daten besser eingegangen wird.

Die CDNA-2-Architektur ist auf höhere Genauigkeit ausgelegt. Die Vektor-Pipeline der neuem Instinct-Karten hingegen dahingehend, dass FP32- und FP64-Berechnungen gleich schnell abgearbeitet werden können – wie in der Tabelle aufgezeigt.

Diese und noch zahlreiche weitere Optimierungen zeigen sich im Durchsatz für die Datenformate:

| MI100 FLOPS/Takt/CU | MI250X FLOPS/Takt/CU | MI100 (TF)OPS) Peak | MI250X (TF)OPS) Peak | |

| Matrix FP64 | 64 | 256 | 11,5 | 95,7 |

| Vektor FP64 | 64 | 128 | 11,5 | 47,9 |

| Matrix FP32 | 256 | 256 | 46,1 | 95,7 |

| Packed FP32 | 128 | 256 | 23,1 | 95,7 |

| Vektor FP32 | 128 | 128 | 23,1 | 47,9 |

| Matrix FP16 | 1.024 | 1.024 | 194,6 | 383 |

| Matrix BF16 | 512 | 1.024 | 92,3 | 383 |

| Matrix INT8 | 1.024 | 1.024 | 92,3 | 383 |

Vor allem die für den HPC-Bereich wichtige FP64-Rechenleistung kann AMD im Vergleich zum Vorgänger mehr als verachtfachen. Für die anderen Datenformate bewegt man sich im Bereich von Faktor zwei bis vier. Gegenüber der Konkurrenz fällt die Leistung ebenfalls um das vierfache höher für FP64 aus, während NVIDIA FP32, FP16 und kleinere Datenformate noch recht gut über die Tensor Cores abarbeiten und somit kompensieren kann.

Die Matrix Cores der CDNA-2-Architektur sind ein wichtiger Bestandteil, um die Leistung der Karten derart in die Höhe zu schrauben. Die Matrix-Einheiten sind als 16x16x4- and 4x4x4-Multiplikations-Blöcke ausgelegt. Die FP64-Matrix-Multiply-Instruktionen haben gegenüber den Vektor-Instruktionen den doppelten Durchsatz und sind somit mit dafür verantwortlich, dass die Instinct-Karten auf diese Rechenleistung kommen. Die Matrix-Einheiten helfen aber auch für Berechnungen in BF16.

Packed FP32 ist ein neues Datenformat der CDNA-2-Architektur. Hier werden zwei Vektor-Instruktionen mit FP32 als Operant für FMA, FASS und FMUL zusammengelegt. Packed FP32 sorgt also für den doppelten Durchsatz für Vektor-FP32-Berechnungen.

Die Rechenleistung kommt allerdings nicht ohne jegliche Nachteile. So bringen es die Instinct MI250 und MI250X auf eine TDP von 500 W, wenn sie per Luft gekühlt werden. Es können aber 560 W konfiguriert werden, wenn eine Wasserkühlung zum Einsatz kommt. Allerdings lässt selbst NVIDIA für die A100-Tensor-GPU eine maximale TDP von bis zu 500 W zu.

Ein Chiplet-Design nun auch für GPU-Beschleuniger

Mit der Instinct-MI200-Serie betritt AMD Neuland für die Fertigung solcher GPU-Beschleuniger. Einerseits werden die Graphics Compute Dies (GCP) in 6 nm bei TSMC gefertigt und bisher laufen GPUs allesamt in 7 oder 8 nm bei TSMC und Samsung vom Band, andererseits werden hier zwei GCPs zusammengeführt, was ebenfalls ein Novum in diesem Segment darstellt.

AMD verwendet dafür ein zusammen mit TSMC entwickeltes Verfahren namens 2.5D Elevated Fanout Bridge (EFB).

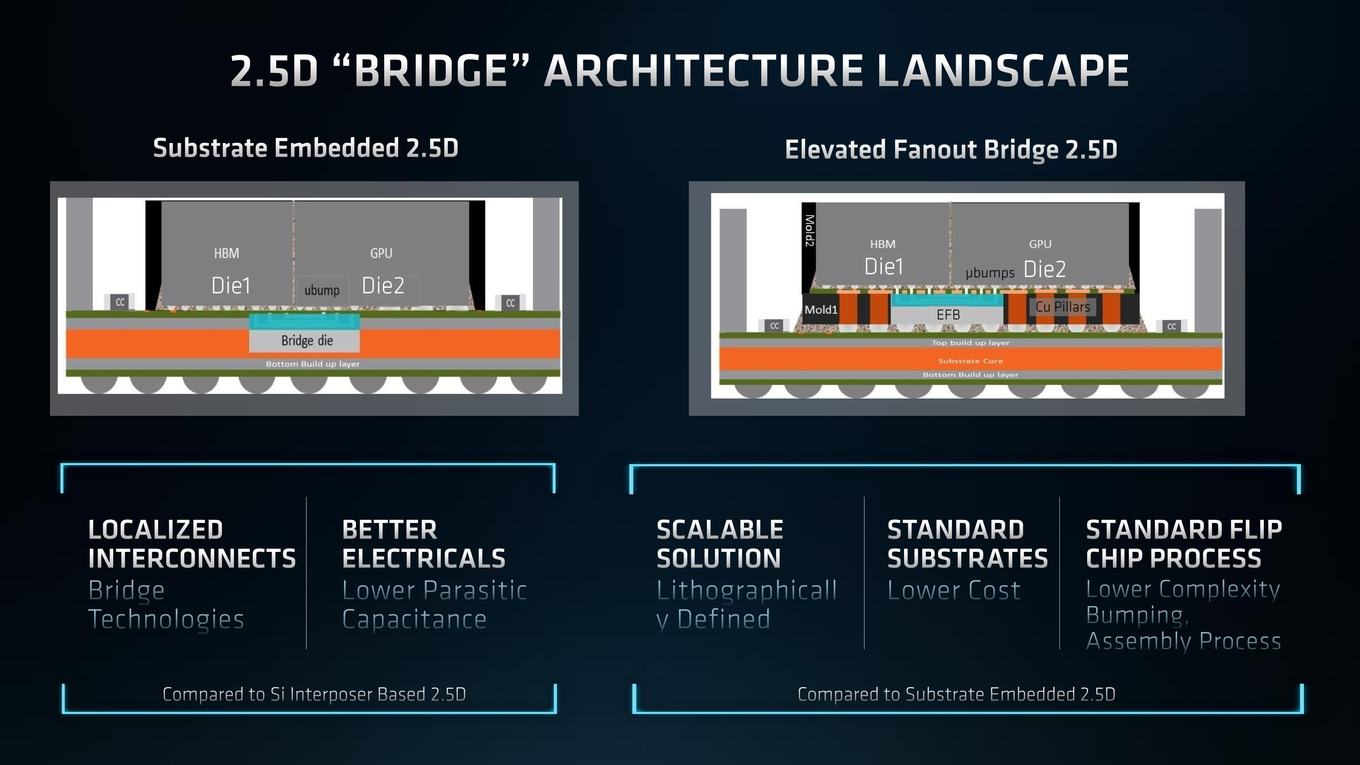

Bisher kommt für die Anbindung von HBM meist ein Silizium-Interposer zum Einsatz, der in den Substratkörper eingearbeitet wird und der zwei Chips, die verbunden werden sollen, miteinander kontaktiert. Diese Methode hat durchaus ihre Vorteile, aber auch einige Nachteile, die vor allem in der Skalierung und den Kosten zu finden sind.

Eine Elevated Fanout Bridge (EFB) verwendet weiterhin ein Standard-Substrat auf dem die Chips sitzen, welches vor allem schnell und günstig herzustellen ist. Über Bumps wird einerseits der Kontakt zwischen den Chips und dem Substrat hergestellt (für nicht direkte Verbindungen zwischen den Chips), andererseits auf gleiche Art und Weise aber auch zur EFB. Diese wiederum sitzt zwischen Kupferverbindungen der Chips zum Substrat und stellt ihrerseits über Bumps die Verbindungen zwischen den Chips her.

Vorteile der Elevated Fanout Bridge sind neben der Verwendung eines einfachen Silizium-Interposer die bessere Skalierbarkeit in der Lithografie und die Tatsache, dass die Chips im klassischen Flip-Chip-Verfahren auf dem Package untergebracht werden können.

Per Elevated Fanout Bridge angebunden sind zunächst einmal die acht HBM2E-Chips der Instinct MI250 und MI250X. Diese acht Chips werden jeweils über ein 1.024 Bit breites Speicherinterface angebunden und kommen somit zusammengenommen auf 8.192 Bit. Der mit 1.600 MHz betriebene HBM2E kommt somit auf eine Speicherbandbreite von 3,276 TB/s.

Ob auch die Verbindung zwischen den Chips per EFB hergestellt wird, ist uns nicht bekannt. Natürlich spielt aber auch die Bandbreite, bzw. die Anbindung zwischen den Chips eine wichtige Rolle. Hier kommt der Infinity Fabric zum Einsatz. Zwischen den zwei GCDs können bidirektional 400 GB/s übertragen werden.

Es gibt außerdem externe Links für den Infinity Fabric, die somit mit weiteren GPUs kommunizieren können. Pro GPU sind dies derer acht und somit 800 GB/s. Zudem gibt es ein kohärentes Host-Interface, welches zwischen kompatiblen Instinct-Beschleunigern und den neuen EPYC-Prozessoren als Infinity Fabric mit 16 Links agiert, aber auch auf eine einfache PCI-Express-Verbindung mit 16 Lanes zurückfallen kann.

Die AMD Instinct MI250 und MI205X sollen in Kürze in den ersten Systemen zum Einsatz kommen. Die PCI-Express-Variante soll etwas später folgen.