Werbung

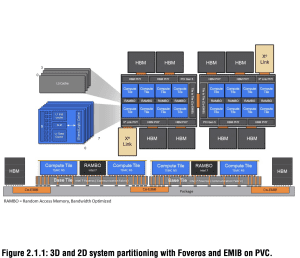

Der HPC-Beschleuniger Ponte Vecchio (PVC) ist ohne Frage eines der komplexesten Halbleiter-Gebilde, welches in den vergangenen Jahren entwickelt wurde. Insgesamt 47 aktive Tiles werden mittels Co-EMIB und Foveros in einem Package miteinander verbunden und verwenden dabei fünf unterschiedliche Prozess-Technologien.

Viele Details zu Ponte Vecchio waren schon im Vorfeld bekannt. Auf der ISSCC 2022 sprach Intel aber nun über zahlreiche interessante Details, wie ein solcher Chip überhaupt zu fertigen ist bzw. wie das Package aufgebaut ist.

In der bisher präsentierten Ausbaustufe von Ponte Vecchio kommen 16 Compute-Tiles zum Einsatz, die bei TSMC in N5 gefertigt werden. Die acht Speicher-Tiles, (RAMBO) sind SRAM-Chips, die bei Intel in Intel 7 (10 nm) gefertigt werden. Hinzu kommen noch acht HBM2E-Chips (externer Anbieter), zwei große Foveros Base-Tiles setzt man ebenfalls auf Intel 7. Die zwei Xe-Link-Tiles lässt Intel wiederum bei TSMC in N7 fertigen.

| Anzahl | Fertigung | |

| Compute-Tile | 16 | TSMC N5 |

| RAMBO-Cache | 8 | Intel 7 |

| Foveros-Base-Tiles | 2 | Intel 7 |

| Xe-Link-Tile | 2 | TSMC N7 |

| HBM2E | 8 | - |

| EMIB-Dies | 11 | - |

| Gesamt | 47 | |

| zusätzliche thermische Tiles | 16 | |

| Insgesamt | 63 |

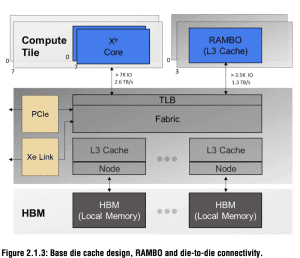

Über den Aufbau der Compute-Tiles haben wir bereits im Sommer 2021 berichtet. Neu sind einige Informationen zum RAMBO-Cache. Dieser SRAM besteht aus vier Bänken zu jeweils 3,75 MB und kommt somit auf 15 MB per Tile. Bei vier RAMBO-Tiles auf zwei Base-Tiles kommen wir hier also auf 120 MB an zusätzlichem Cache. Dieser ist mit 1,3 TB/s je Chip an den Fabric angebunden. Ein kurzer Verweis zur Anbindung der Compute-Tiles: Diese findet über jeweils 2,6 TB/s über den Fabric statt.

Der Base-Tile kommt auf eine Fläche von 646 mm² und stellt die Infrastruktur für PvC bereit. Dies beinhaltet auch die Speichercontroller, die Fully Integrated Voltage Regulators (FIVR), das dazugehörige Power Management und das 16 Lanes umfassende PCIe 5.0 bzw. CXL Host-Interface. Der Base-Tile besteht aus 17 Layern und wird in Intel 7 gefertigt.

Die 47 aktiven Tiles kommen auf eine gemeinsame Chipfläche von 2.330 mm². Mitsamt der thermischen Tiles sind es 3.100 mm². Das gesamte Package kommt auf 77,5 x 62,5 mm (4.844 mm²). Als OAM-Modul wird Ponte Vecchio über 4.468 Pins mit dem restlichen System verbunden.

Die Compute- und RAMBO-Tiles werden Face-to-Face auf dem Base-Tile platziert. Dazu werden Micro Bumps mit einem Abstand von nur 36 ?m verwendet. Für die Verbindung der beiden Base-Tiles und die HBM2E-Chips kommt Co-EMIB mit einem Bump-Abstand von 55 µm zum Einsatz. Die Versorgung der Compute- und RAMBO-Tiles durch den Base-Tile erfolgt mittels Power TSVs in verschiedenen Array-Konfigurationen mit dicken Metallschichten zur Verteilung.

Ein weiterer Bestandteil des Base-Tile sind jeweils 144 MB an L3-Cache sowie ein Memory Fabric (MF) mit einer komplexen geometrischen Topologie und einer Bandbreite von 4.096 Bytes pro Taktzyklus. Die Speicherbänke befinden sich direkt unterhalt der Compute-Tiles und stellen eine Erweiterung der L1- und L2-Caches dar. Sie kommen bidirektional auf jeweils auf 64 Bytes pro Takt.

Für die Verbindung zwischen den Compute- und RAMBO-Tiles mit dem Base-Tile wird der Foveros Die Interconnect (FDI) verwendet. Jeder FDI-Link ist in acht Gruppen aufgeteilt. Jede Gruppe besteht wiederum aus 800 Lanes für die Compute-Tiles. Die Energieeffizienz des FDI liegt bei 0,2 pJ/B. Ein einzelner Link kommt somit auf 2,8 GT/s.

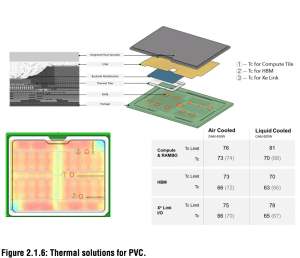

Bisher hat Intel noch wenige Worte zum Stromverbrauch von Ponte Vecchio verloren. Die FIVR sind pro Base-Tile auf 300 W ausgelegt. Bei 2x 300 W entspricht dies auch den 600 W auf die Intel das gesamte Package auslegt. Dicke Interconnect-Schichten in den Base- sowie Compute-Tiles dienen als laterale Heatspreader. Die Compute-Tiles sind mit 160 µm relativ dick. Dies hat aber auch seine Gründe, denn Intel liegt diese so aus, damit ausreichend thermische Masse für kurze Boost-Modi vorhanden ist.

Zu den 47 funktionalen Dies (siehe Tabelle) gesellen sich zudem noch 16 zusätzliche thermische Tiles die in Bereichen sitzen, in denen die Base-Tiles keinerlei Kontakt zur oberen Ebene haben. Die thermischen Tiles sollen die Abwärme aufnehmen und an den darüberliegenden Heatspreader weitergeben. Sogenannte Backside Metallization (BSM) zusammen mit einem Thermal Interface Material (TIM) wie man es auch von den Prozessoren kennt, wird auf die oberste Ebene aufgebracht. Das TIM soll sämtliche Höhenunterschiede ausgleichen. BSM wird zudem auf den HBM2E-Chips und den Xe-Link-Tiles angewendet.

Die Kühlung von Ponte Vecchio ist nicht ohne Hürden. Luftgekühlt sieht Intel eine TDP von 450 W vor, wassergekühlt sollen es 600 W sein. Die einzelnen Komponenten sind dabei für bestimmte Temperaturbereiche bzw. Maximaltemperaturen vorgesehen. Intel spricht von Tc- und Tc-Max-Temperaturen zwischen 63 und 81 °C – normale Temperaturen von Hardware in diesem Segment.

Noch haben wir Ponte Vecchio nicht in Aktion gesehen. Der Aurora-Supercomputer wird die erste Plattform für den HPC-Beschleuniger sein. Er wird aber auch in OEM-Systemen angeboten werden.