Werbung

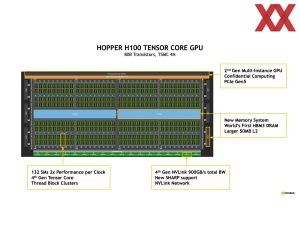

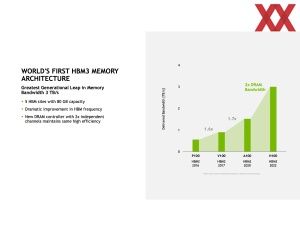

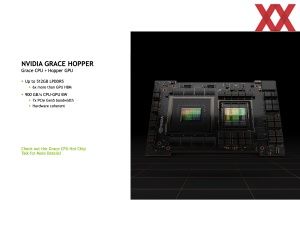

Zur GPU Technology Conference im Frühjahr stellte NVIDIA die GH100-GPU auf Basis der Hopper-Architektur, bzw. den H100-Beschleuniger vor. Zur Hotchips 34 sprach NVIDIA über die Herausforderungen eines solches Designs und wie eine GPU mit 16.896 FP32-Recheneinheiten, 528 Tensor Cores, 50 MB an L2-Cache und 80 GB an HBM3 auszulasten ist – ganz zu schweigen davon, mehrere hundert oder gar tausend GPUs zusammenarbeiten zu lassen.

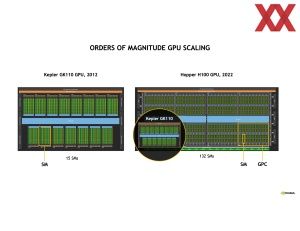

Die GH100-GPU ist in 4 nm gefertigt dennoch 814 mm² groß und besitzt 80 Milliarden Transistoren. Schaut man zehn Jahre zurück, hatte NVIDIA damals die GK110-GPU für beispielsweise die GeForce GTX Titan im Angebot. Das, was heute ein GPC (Graphics Processing Cluster) der Hopper-Architektur ist, kann in etwa mit dem verglichen werden, das früher als GK110 eine komplette GPU darstellte. Von diesen GPCs besitzt die GH100-GPU allerdings gleich acht.

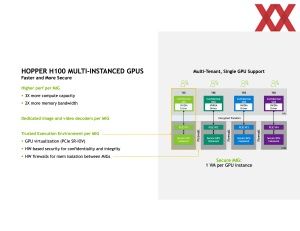

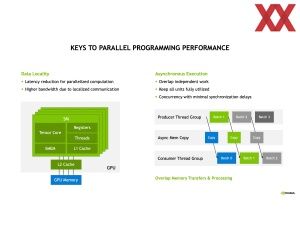

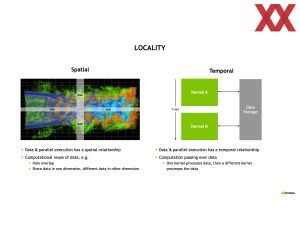

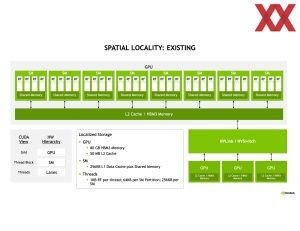

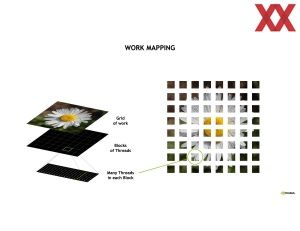

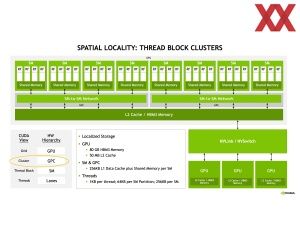

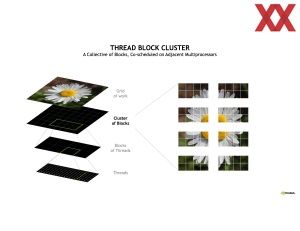

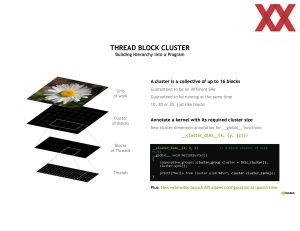

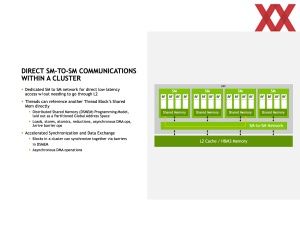

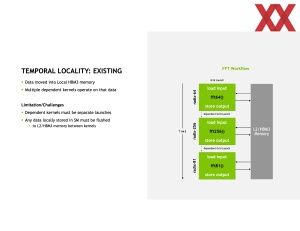

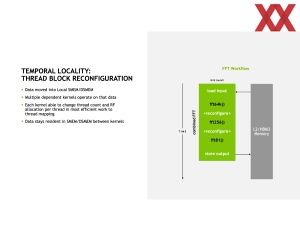

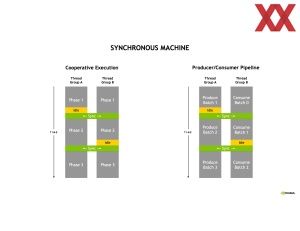

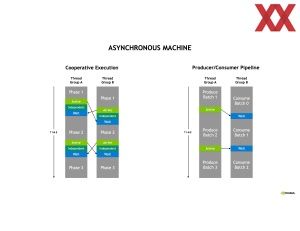

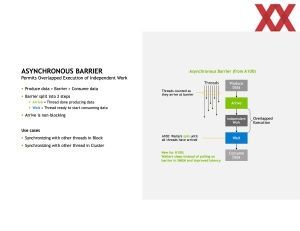

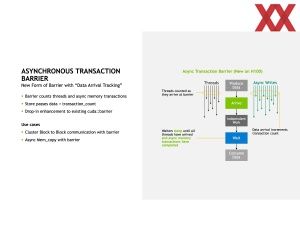

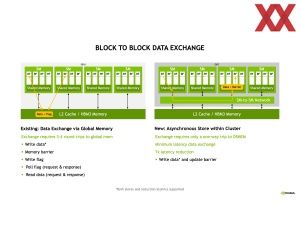

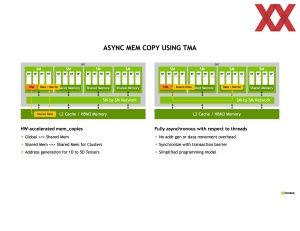

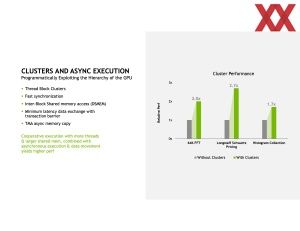

Um eine derart große GPU effizient nutzen zu können, muss diese für die Anwendungen in mehrere Bereiche aufgeteilt werden. Letztendlich ermöglicht diese Technik es, auch die GPU in virtuelle Instanzen aufzuteilen – ähnlich wie man dies mit der Multi-Instance GPU (MIG) bereits für den Vorgänger vorstellte. Über ein Clustering und den asynchronen Betrieb im Workflow kann die Effizienz, bzw. die Auslastung des H100-Beschleunigers teilweise deutlich verbessert werden. NVIDIA spricht hier von Faktor 1,7 bis 2,7.

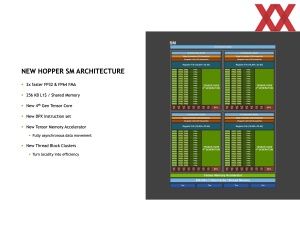

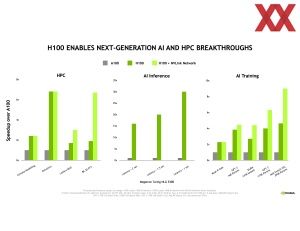

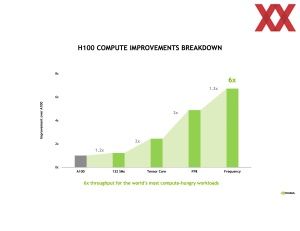

Vergleicht man den H100-Beschleuniger mit seinem Vorgänger A100, fällt sicherlich schnell auf, dass NVIDIA hier die Architektur auf 132 SMs aufgebohrt hat, wir aber von 20 % mehr Funktionseinheiten sprechen. Zugleich soll die Leistung in verschiedenen Anwendungen um den Faktor sechs und mehr steigen.

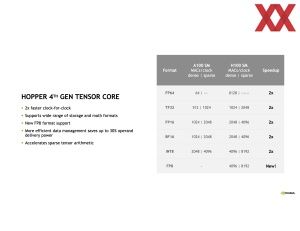

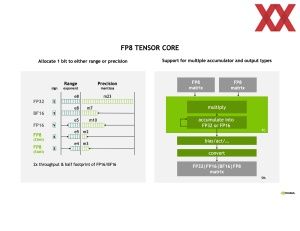

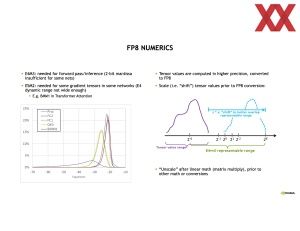

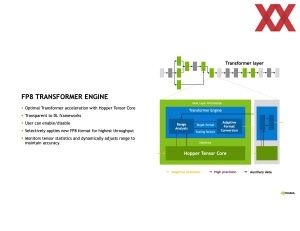

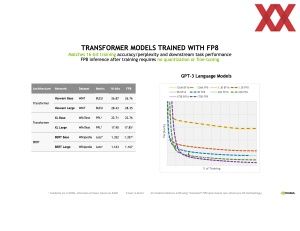

Auf der Hotchips schlüsselte NVIDIA nun genauer auf, wie die gesamte Leistungssteigerung erreicht worden ist. Die Rohleistung steigt um 20 %, weil eben 20 % mehr Funktionseinheiten zum Einsatz kommen. Die Tensor Cores der vierten Generation sind durch die Unterstützung weiterer Datenformate – unter anderem durch FP8 – deutlich schneller geworden und sollen durch ein intelligenteres Datenmanagement um 30 % effizienter sein. Die Tensor Cores sollen alleine doppelt so schnell sein, wie ihre Vorgänger der Ampere-Architektur. Eine weitere Verdopplung wird durch den Einsatz von FP8 ermöglicht. Schlussendlich kommt noch ein Taktplus von 30 % hinzu, so dass ohne jegliche Optimierung der Anwendungen selbst eine Leistungssteigerung um den Faktor sechs ermöglicht wird.

Einen direkten Vergleich der Leistung zwischen dem H100-Beschleuniger sowie AMDs Instinct MI250X gibt es noch nicht. Außerdem wäre eine Gegenüberstellung mit dem Ponte-Vecchio-Beschleuniger von Intel interessant. Diese drei werden für 2023 die Gegenspieler im HPC- und AI-Datacenter-Segment sein.