Werbung

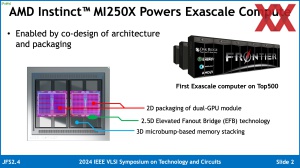

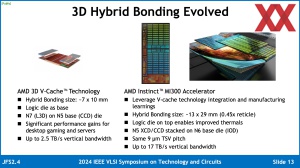

Bereits im Dezember des vergangenen Jahres präsentierte AMD die ersten beiden Ableger der Instinct-MI300-Serie: Die Instinct MI300X und die Instinct MI300A. Auch zum "3.5D"-Package und dem Layout mit Interposer, IOD sowie XCD und CCD gab man damals bereits einige Details bekannt. Auf dem VLSI Symposium 2024 sprach AMD nun in weiteren Details darüber, denn, was auf den ersten Blick nach einem einfachen modularen Design aussieht, hat bei genauerer Betrachtung so einige Tücken.

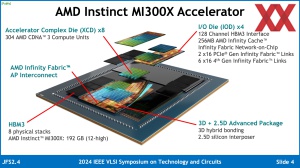

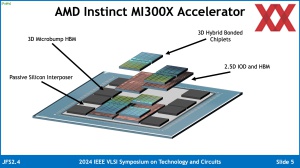

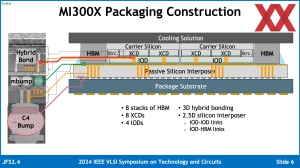

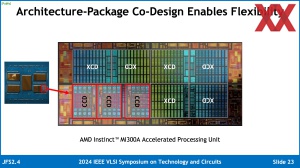

Das Substrat (welches hier ein organisches Package ist) stellt die unterste Ebene des Chips dar. Darauf sitzt der passive Silicon Interposer als Chip on Wafer on Substrate (TSMC CoWoS). Auf dem Silicon Interposer befinden sich dann die IODs, auf denen sich wiederum die XCDs und CCDs positioniert werden – daneben wiederum die HBM3-Speicherchips. Dummy-Chips neben den XCDs und CCDs füllen die Lücken, ein sogenanntes Carrier Silicon bringt die Chips auf die gleiche Höhe wie die HBM3-Speicherchips und alles wird mit einem Heatspreader abgedeckt.

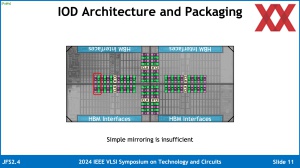

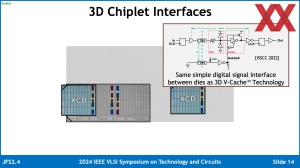

Soweit der grundsätzliche Aufbau. Der Vorteil eines Chiplet-Designs soll es sein, dass man möglichst viele Chips mehrfach einsetzt, um die Kosten zu reduzieren. Zugleich soll das gesamte Package wie ein großer Chip funktionieren. Die Kommunikation der Chiplets untereinander ist entscheidend und dies beginnt bereits bei den IODs. Diese sind rechteckig und je nach physikalischer Länge der Kontaktfläche (horizontaler oder vertikaler Cut) mit 3 TB/s und 2,4 TB/s untereinander angebunden.

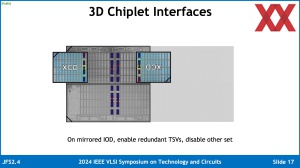

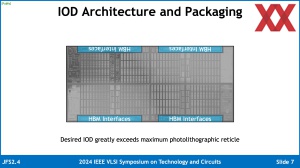

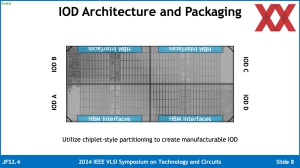

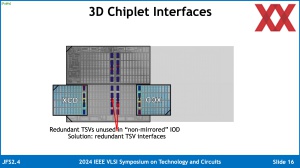

AMD fertigt die XDCs und CCDs mit als GPU- und CPU-Chiplets in einer Ausführung und platziert diese auf den IODs. Von diesen gibt es zwei verschiedene, ein IOD A und eine bespiegelte Variante IOD B. Eine einfache Spiegelung reicht an den USR-PHYs (AMD Ultra-Short Reach) als Schnittstelle zwischen den IODs allerdings nicht aus, da sich hier sonst Transceiver und Receiver gegenüberstünden. AMD muss die Transceiver- und Receiver-Bereiche tauschen und das auf den beiden Seiten für die USR-PHYs. Dies stellt jedoch keine komplexe Änderung am Design dar und somit konnte AMD die zwei IODs aus einem Design recht schnell und einfach in zwei Tape-Outs ummünzen. IOD A und die gespiegelte, sowie leicht modifizierte Variante IOD B werden um IOD C (IOD A um 180 ° gedreht) sowie IOD D (IOD B um 180 ° gedreht) ergänzt und schon hat man die vier IODs, die zueinander ausgerichtet miteinander kommunizieren können.

Redundante TSVs

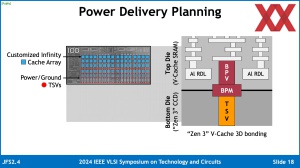

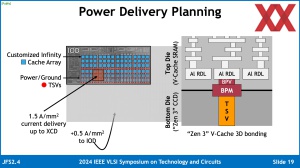

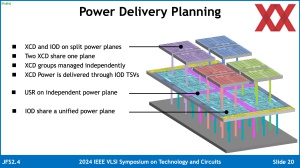

Nicht die Datenleitungen zu den XDCs und CCDs werden über die IODs realisiert, sondern auch die Strom- und Spannungsversorgung. Dies muss im Design des IOD A und IOD B bereits berücksichtig werden. Eine weitere Ebene an Komplexität kommt hinzu, wenn man sich vor Augen führt, dass AMD die XDCs und CCDs ebenfalls in normaler und 180 ° gedrehter Ausführung auf den IODs platziert.

Jeder IOD sieht daher in der Mitte zwei schmale Streifen mit 3D Bond Pads vor, die für die XCDs und CCDs in normaler und rotierter Ausrichtung vorgesehen sind. Allerdings muss man eben auch hier unterscheiden, ob nun drei CCDs oder zwei XDCs auf dem IOD platziert sind, denn die Pads müssen universell erreichbar sein, bzw. AMD hat im Design bereits vorgesehen, dass es redundante TSV-Bereiche gibt, die nicht immer genutzt werden.

Wichtig ist weiterhin eine entsprechende Auslegung des Power Grids, damit die darunterliegenden Metallschichten weiterhin für eine gleichmäßige Spannungsversorgung sorgen können. Zwischen dem Cache-Array im IOD befinden sich zahlreiche TSVs, um elektrische Leistung und Ground vom Interposer in den IOD zu führen. Laut AMD sprechen wir hier von 0,5 A/mm² vom Interposer in die IODs und diese wiederum müssen 1,5 A/mm² in die XDCs liefern können.

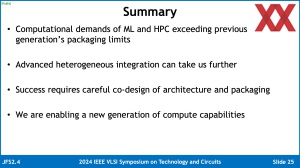

Wenn man sich die Komplexität des Packaging der Instinct-MI300-Familie vor Augen führt, dann muss man sich an dieser Stelle schon fragen, ob AMD hier den richtigen Weg eingeschlagen hat. Auch wenn AMDs Instinct MI300X in den vergangenen Wochen mehr Aufmerksam bekommen hat und besser verfügbar ist, so zeigt sich noch nicht, dass NVIDIAs Dominanz damit gebrochen werden kann.