Werbung

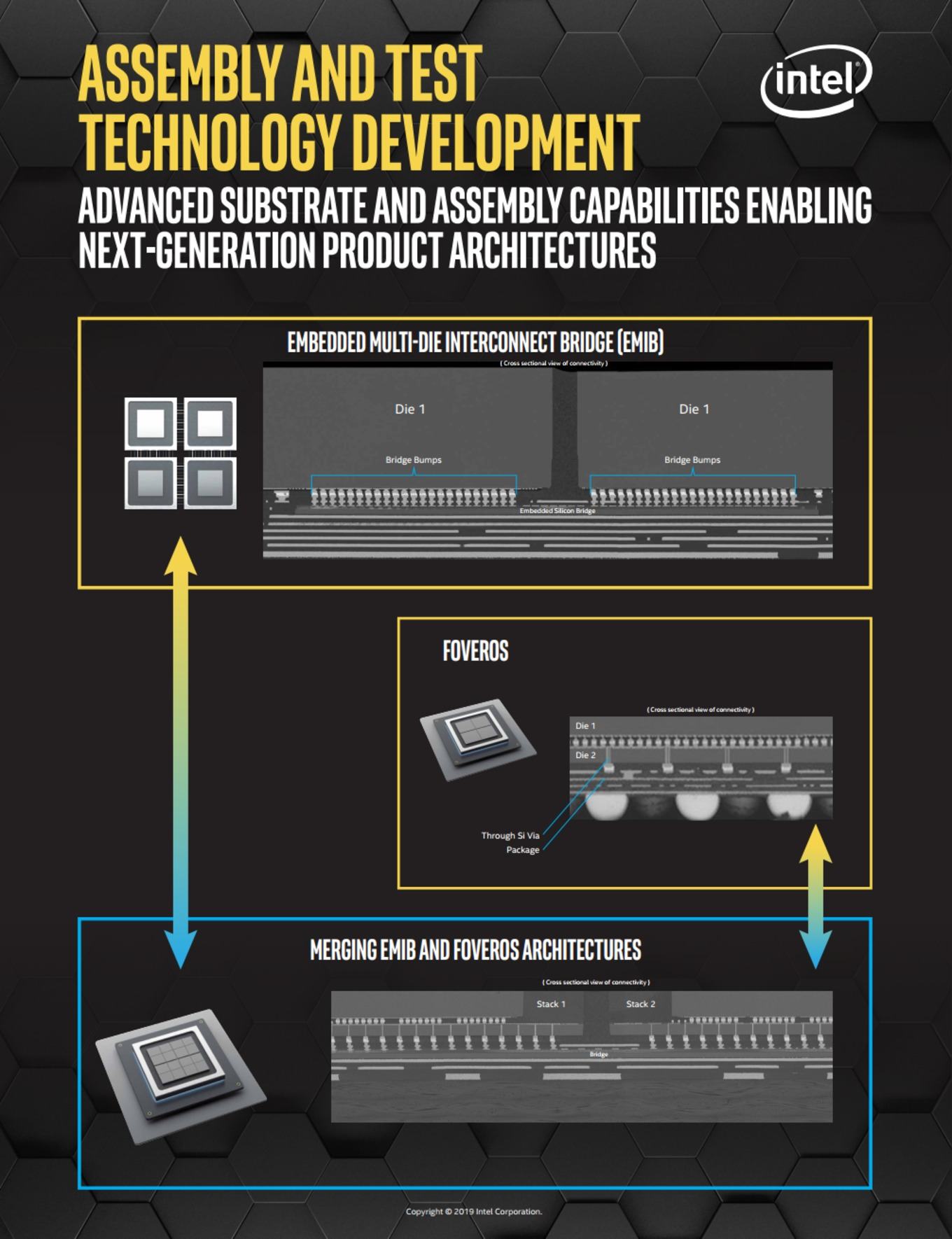

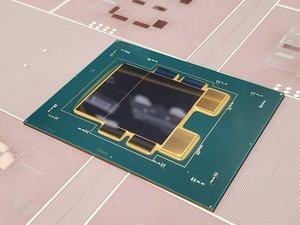

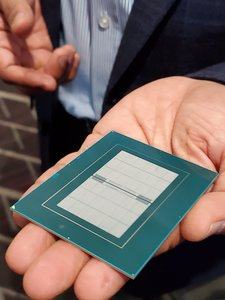

Auf der SemiCon West hat Intel über neue Packaging-Technologien gesprochen. Zuletzt machte der Chipgigant mit der Nennung einiger neuer Daten zu FOVEROS auf sich aufmerksam. Co-EMIB soll die beiden bestehenden Packaging-Technologien für Intel zusammenführen. Während EMIB (Embedded Multi Die Interconnect Bridge) bereits bei den Kaby-Lake-G-Prozessoren sowie den Stratix-10-FPGAs zum Einsatz kommt, wird FOVEROS bisher nur bei den noch nicht verfügbaren Lakefield-Prozessoren verwendet.

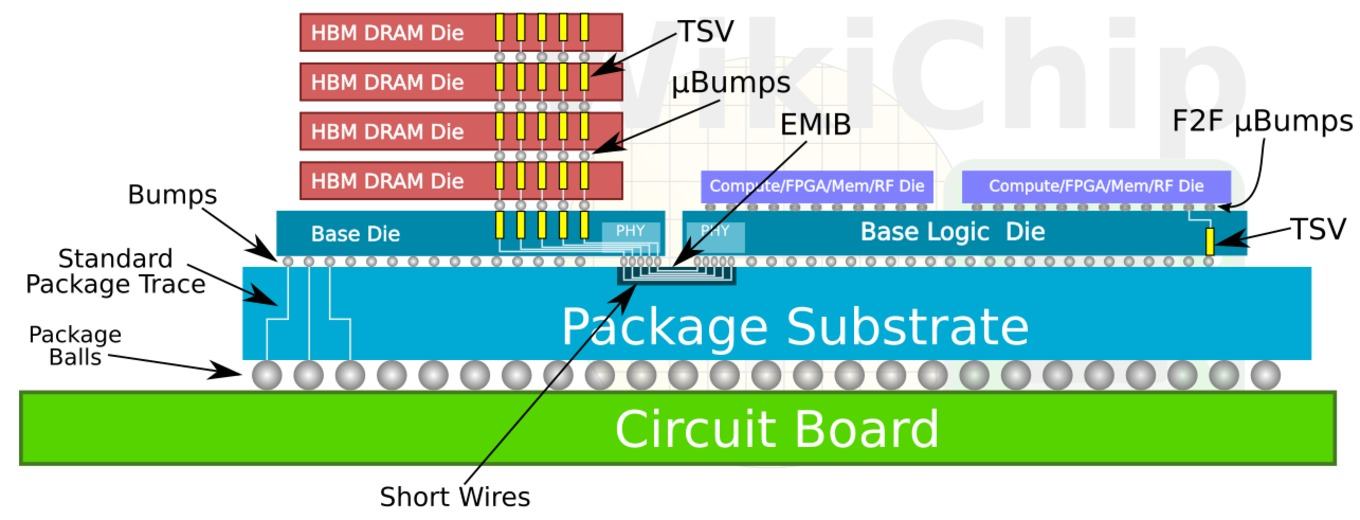

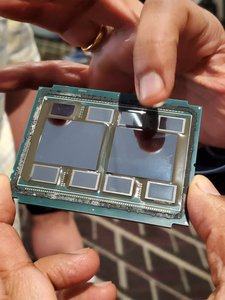

In Co-EMIB wird der EMIB-Part im Substrat verwendet, auf dem dann die einzelnen Dies sitzen. Per FOVEROS werden dann auf bzw. in diesen Chips verschiedene Layer realisiert. Denkbar ist HBM-Speicher auf einem Base-Die oder verschiedene Transceiver und andere IP über einem Compute-Die. Co-EMIB versetzt Intel die Lage, nicht nur flexible Designs zu erstellen, sondern diese auch extrem komplex zu gestalten. So sind riesige Packages mit 36 einzelnen Chiplets denkbar.

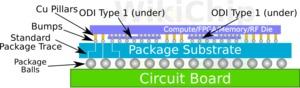

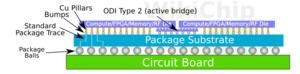

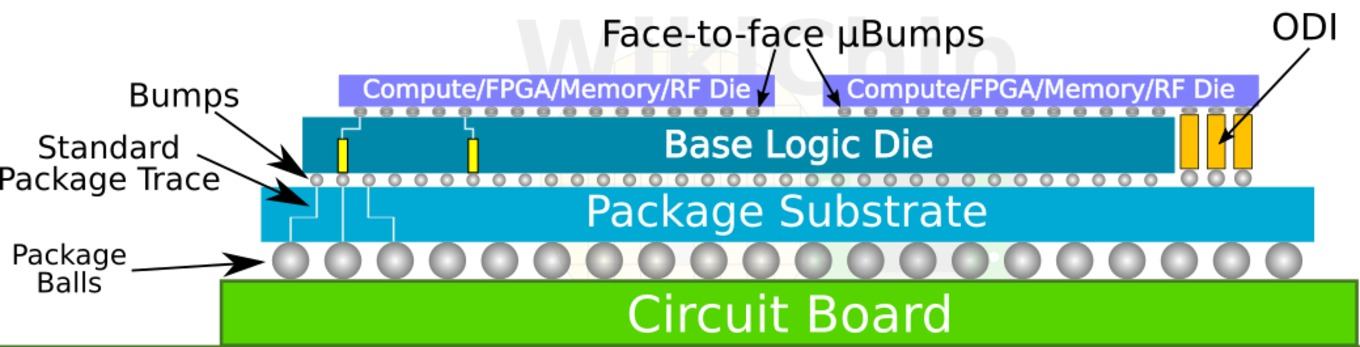

Eine Erweiterung der bisherigen Interconnect-Technologien ist der Omni-Directional Interconnect (ODI). Dabei handelt es sich um Halbleiter-Brücken, die zwischen oder unter den Dies eingesetzt werden können. Es gibt einen ODI Typ 1, der unter einem Die eingesetzt werden kann. Typ 2 von ODI stellt eine aktive Brücke zwischen zwei Dies dar. Die Bridge selbst kann dabei unter dem Die herausstehen. Eine dritte Variante ist eine Erweiterung von Typ 2, wobei die Datenverbindungen an einem Chip vorbei an einen mittels FOVEROS realisierten Layer geführt werden. Die Brücke wird hier sozusagen um 90 ° gedreht und befindet sich nicht mehr in horizontaler Lage, sondern wird hochkant aufgestellt.

Im Unterschied zu EMIB werden die Datenverbindungen nicht ein Package-Substrat geführt, sondern befinden sich in der Brücke selbst. Wikichip hat hier ein paar sehr schicke schematische Darstellungen, die den Unterschied verdeutlichen.

Als Nachfolger des aktuellen Advanced Interface Bus (AIB) vorgesehen ist MDIO (Management Data Input/Output). MDIO soll im Vergleich zu AIB deutlich effizienter sein, dabei aber die doppelte Datenrate ermöglichen. Für Intel wird MDIO in zukünftigen Chiplet-Designs eine wichtige Rolle spielen.

Derzeit macht es vor allem den Eindruck, als arbeite Intel mit Hochdruck an den Packaging-Technologien, um damit wiederum zukünftige CPU-, SoC- und FPGA/ASIC-Designs realisieren zu können. EMIB war hier nur der erste Schritt, FOVEROS findet in Kürze Verwendung und Co-EMIB ist dabei nur ein weiterer Schritt.

Solch komplexe und riesigen Packages, wie die nun von Intel gezeigten, werden aber sicherlich zunächst einmal nur für Spezialbeschleuniger eine Rolle spielen. Im Desktop-Bereich werden EMIB und FOVEROS zunächst einmal getrennt voneinander verwendet werden. Der Omni-Directional Interconnect ist die wortwörtliche Brückentechnologie zwischen EMIB und FOVEROS. MDIO spielt erst für zukünftige Designs eine Rolle.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen