Werbung

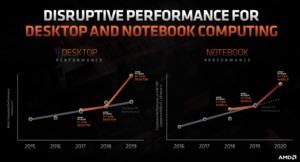

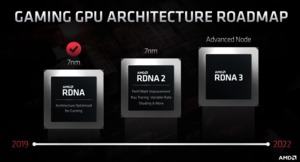

AMDs CEO Dr. Lisa Su sprach zu Beginn des Financial Analyst Day 2020 über die Pläne für die kommenden 20 Monate. Auf der Roadmap der Prozessoren befinden sich die Zen-3 und Zen-4-Architektur. Die ersten Prozessoren auf Basis der Zen-3-Architektur werden noch in diesem Jahr erwartet. Zen 4 wird dann vermutlich 2022 ein Thema sein. Auch auf Seiten der GPU-Architektur spricht AMD über die nähere Zukunft. RDNA 2 wird ebenfalls noch in diesem Jahr den Weg in die ersten GPUs finden. RDNA 3 spielt dann erst 2022 eine Rolle.

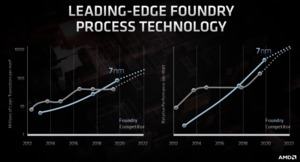

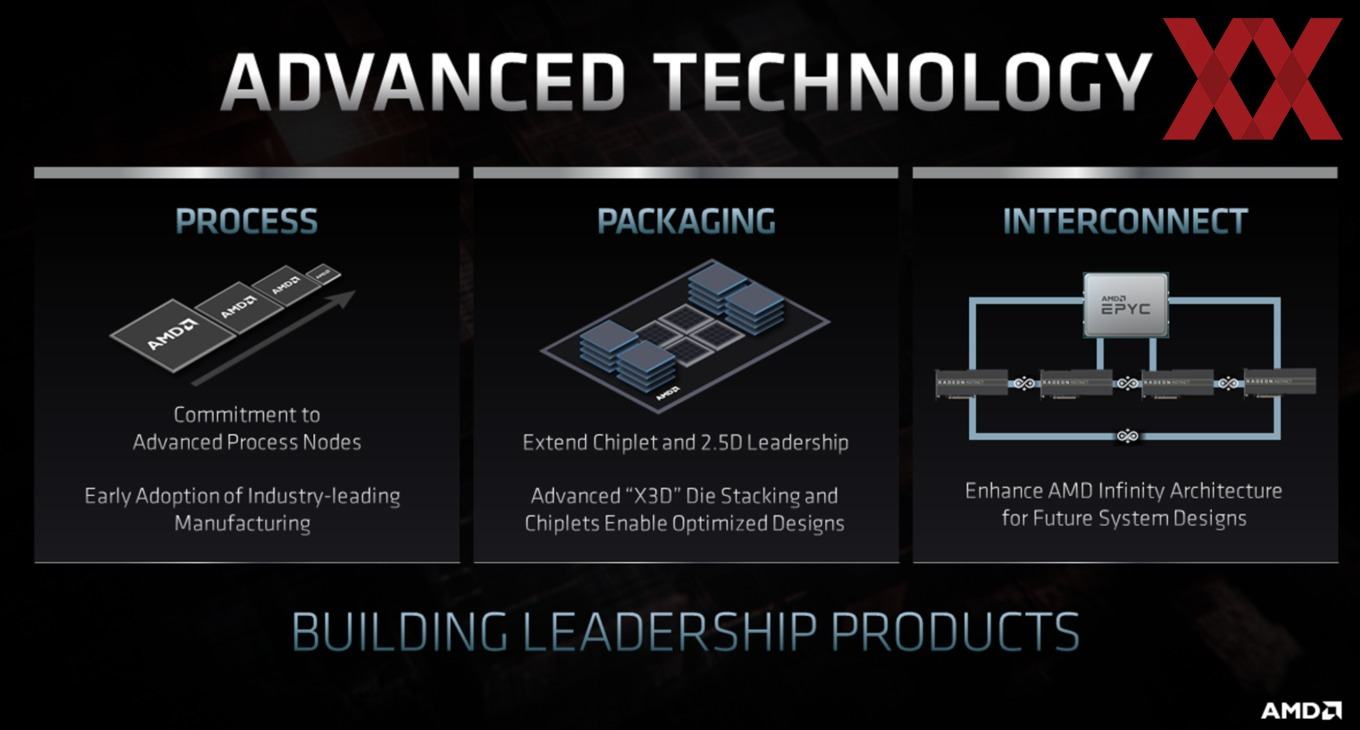

Doch die Produkte benötigen natürlich den technischen Hintergrund, sei es in der Fertigung, dem Packaging oder den weiteren Aspekten, die allesamt eine Rolle spielen. Derzeit lässt AMD seine CPU-Chiplets in 7 nm bei TMSC fertigen, genau wie die Navi-GPUs. Hier wird es mit Zen 3 und RDNA 2 sicherlich Verbesserungen geben, ob dies gleich den Schritt zu 5 nm bedeutet, lässt sich allerdings nur schwer beurteilen. Vermutlich wird AMD zunächst eine verbesserte Fertigung in 7 nm in Anspruch nehmen. Für Prozessoren auf Basis der Zen-4-Architektur hat AMD nun den Einsatz von 5 nm in der Fertigung bestätigt.

| Fertigung | Produkte | Erscheinungsjahr | |

| RDNA 2 | 7 nm | Navi 2X | Ende 2020 |

| RDNA 3 | "Advanced Node" | Navi 3X | 2022 |

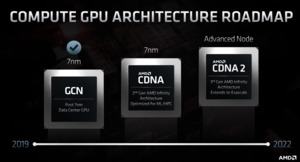

| CDNA | 7 nm | Radeon Instinct | Ende 2020 |

| CDNA 2 | "Advanced Node" | Radeon Instinct | 2022 |

| Zen 3 | 7 nm | Ryzen 4000-Serie EPYC Milan | Ende 2020 |

| Zen 4 | 5 nm | Ryzen 5000 Serie EPYC Genoa | 2022 |

AMD will die Kadenz, also die Abstände in denen neue CPU- und GPU-Architekturen so kurz halten, wie aktuell. Es ist also alle 12 oder 18 Monate eine neue Architektur zu diesen Bereichen zu erwarten.

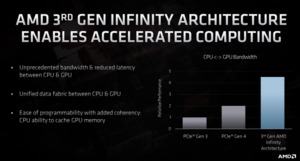

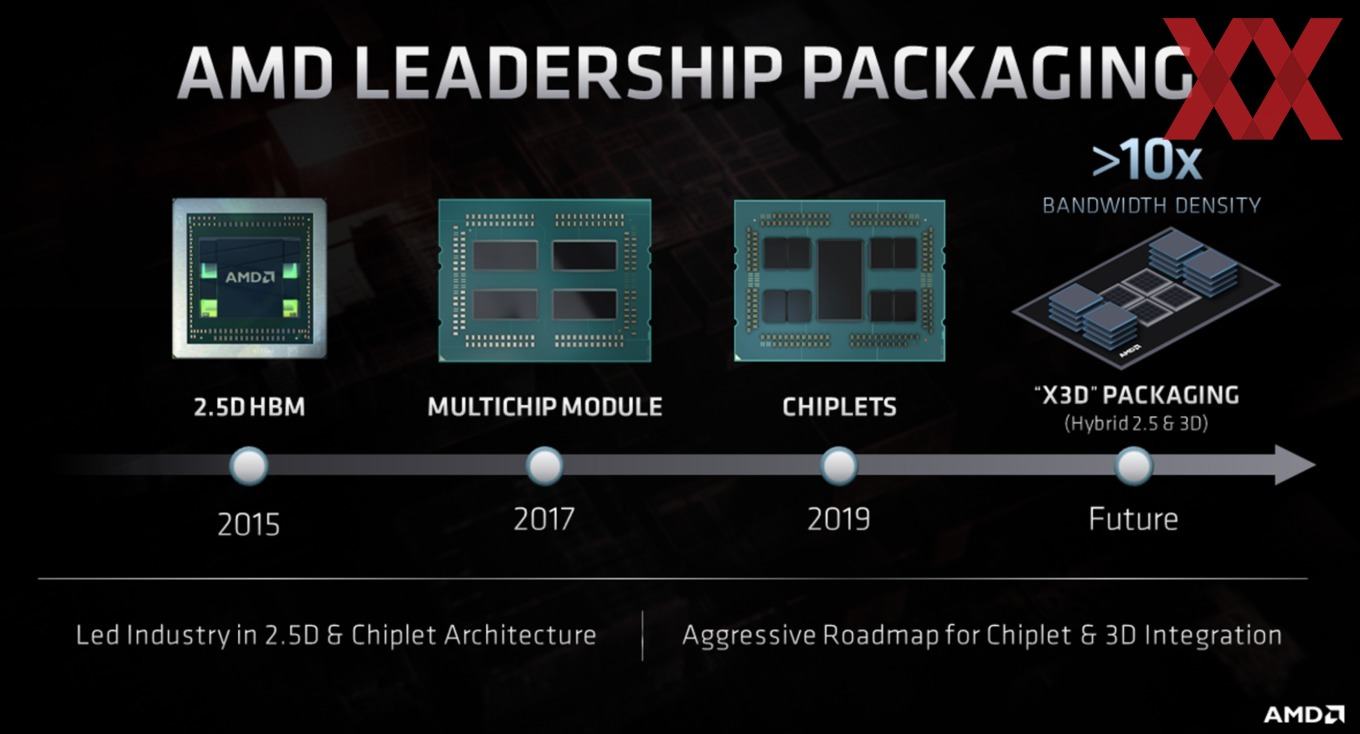

Zunächst noch ohne weitere Details spricht AMD über weitere Packaging-Lösungen. Diese sollen das Chiplet-Design weiterentwickeln und schließen auch ein X3D-Stacking mit ein. Was sich genau dahinter verbirgt, wird AMD im Verlaufe der Veranstaltung verraten. Verbesserungen wird es auch beim Interconnect sprich dem Infinity Fabric geben.

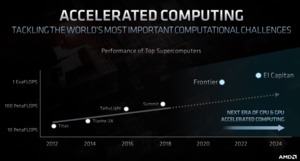

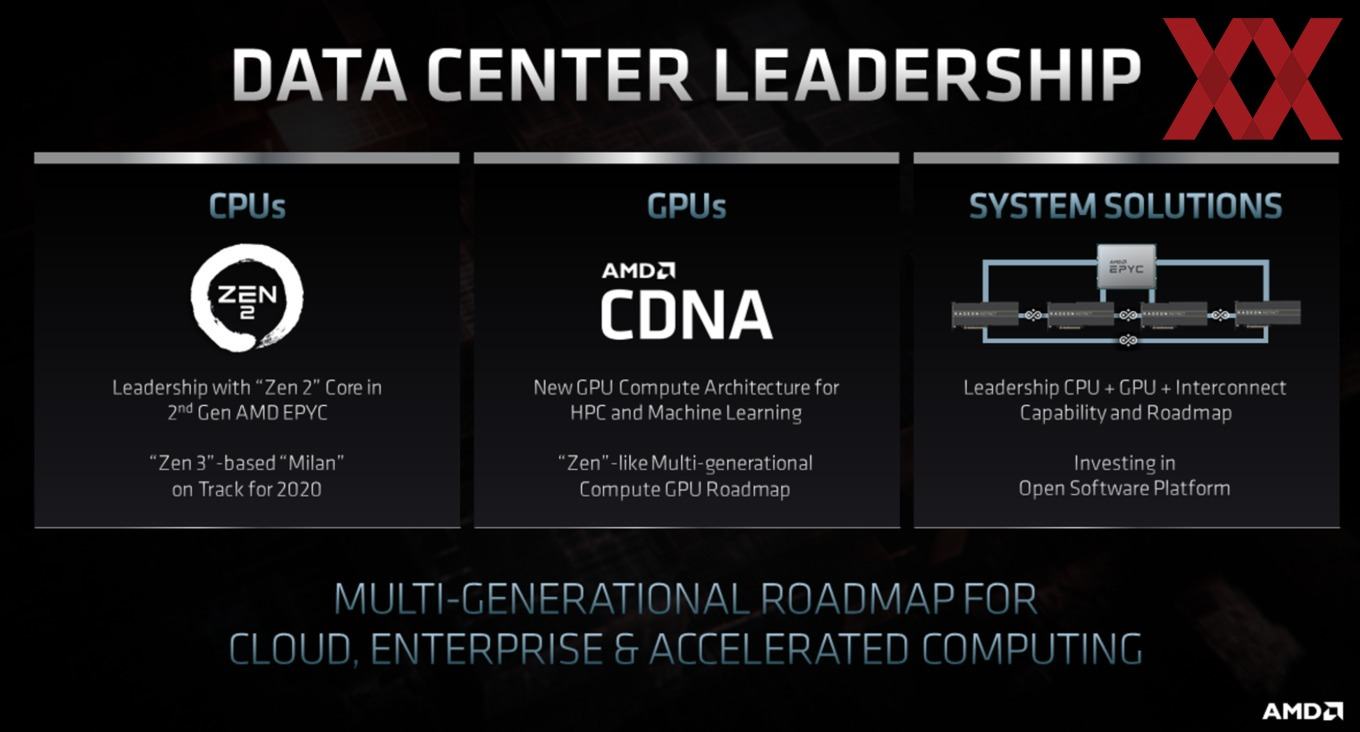

Im Datacenter-Segmemt bestätigt AMD das Erscheinen der EPYC-Prozessoren der dritten Generation alias Milan in diesem Jahr. Zudem wird es eine GPGPU-Architektur für Radeon Instinct geben, die auf den Namen CDNA (analog zur RDNA-Architektur bei den Radeon-Karten) oder hört.

Auf einer weiteren Folien könnte dann eine der neue Grafikkarten zu sehen sein, die 2020 auf den Markt kommen werden. Zu beachten gilt, dass es sich auch einfach nur um eine konzeptionelle Darstellung handeln könnte.

AMD will technologischer Vorreiter sein

AMD sieht sich in der Position nicht nur in der eigenen IP und Architektur führend zu sein, sondern auch vom technologischen Standpunkt aus.

Mark Papermaster, CTO von AMD, sprach noch einmal über die Details in den technologischen Bereichen, in denen AMD in den kommenden Jahren weiterhin führend sein will. Bereits angesprochen haben wir, dass Prozessoren auf Basis der Zen-4-Architektur in 5 nm gefertigt werden sollen.

Das Chipset-Design bei den Ryzen- und EPYC-Prozessoren ist sicherlich der wichtigste Bestandteil der aktuellen Produktstrategie X3D-Packaging ist ein Hybrid aus 2.5D und 3D-Chips, ähnlich wie Intel dies beispielsweise wie die Lakefield-Prozessoren vorsieht.

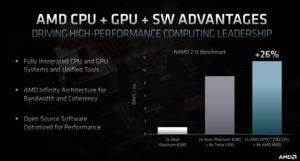

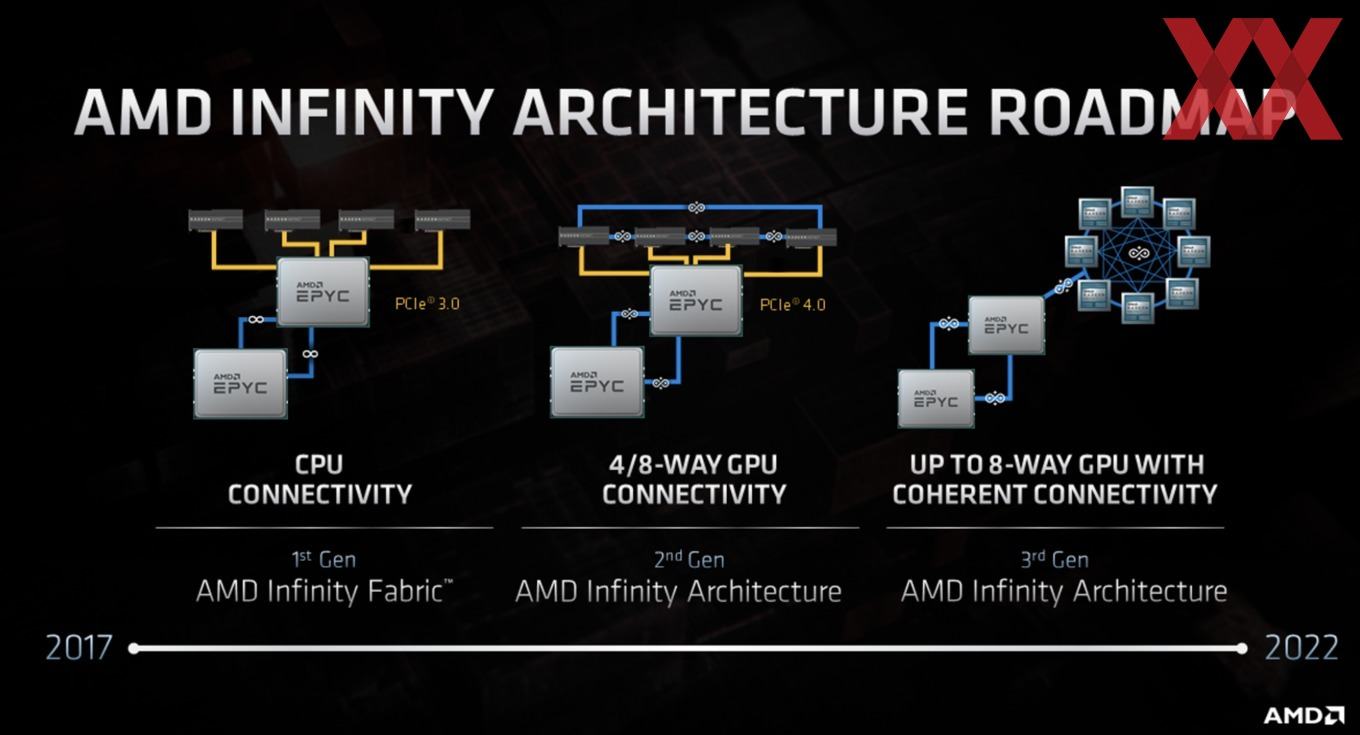

Rückgrat der AMD-Chips ist der Infinity Fabric und auch hier plant AMD in den kommenden Jahren weitere Verbesserungen. Demzufolge hat AMD eine Infinity Architecture Roadmap. Die erste Generation des Infinity Fabric sah eine CPU-CPU-Verbindung vor- GPGPU-Beschleuniger wurden per PCI-Express angebunden. Die zweite Generation des Infinity Fabric bietet die Möglichkeit, dass sich bis zu vier GPUs untereinander verbinden. Einen Infinity Fabric zwischen den GPUs und den EPYC-Prozessoren gibt es aber auch hier noch nicht. Erst mit der dritten Generation des Infinity Fabric wird es auch diese Möglichkeit geben. Hinzu kommt die Speicher- und Cache-Kohärenz.

Aktuell müssen die Applikationen noch genau wissen, in welchem Systemspeicher oder auf welchem GPU-Beschleuniger sich bestimmte Daten befinden. Bearbeiten mehrere GPUs grundsätzlich die gleichen Daten, müssen diese auch jeweils im Speicher liegen und sind somit mehrfach vorhanden. Eine Kohärenz würde es ermöglichen, dass die Daten nur noch im Systemspeicher liegen und von multiplen GPUs darauf zugegriffen wird oder aber mehrere GPUs sich Datensätze teilen, die nur einer GPU zugeordnet sind.

Während sich AMD für Prozessoren auf Basis der Zen-4-Architektur nun auf 5 nm festgelegt hat, sieht dies bei den GPU-Architekturen noch etwas anders aus. RDNA und RDNA 2 sind und werden in 7 nm gefertigt werden. Dies gilt auch für CDNA und CDNA 2. Für RDNA 3 und CDNA 3 spricht AMD von einem "Enhanced Node" für die Fertigung. Dies könnte eine verbesserte Fertigung in 7 nm bedeuten, aber auch eine in 5 nm – AMD legt die Karten hier noch nicht auf den Tisch.

RDNA 2 für Raytracing – CDNA für HPC und ML

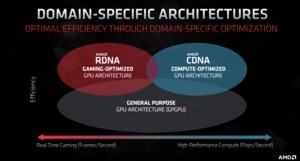

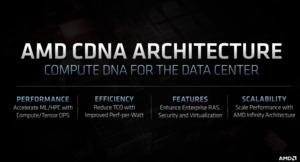

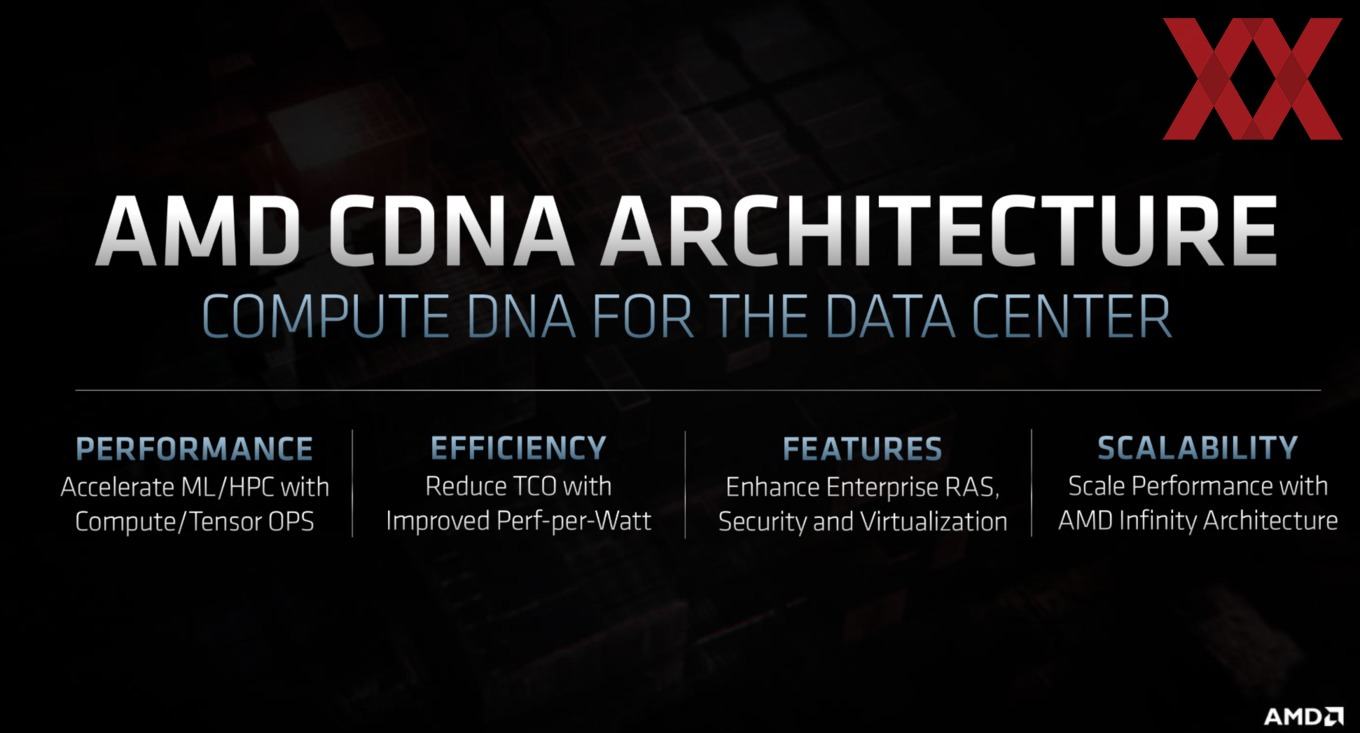

Bei den GPUs trennt AMD seine Strategie auf die zwei wichtigen Märkte auf. Es gibt nun eine RDNA-Roadmap für die Radeon-Produkte und eine CDNA-Roadmap für die Radeon-Instinct-Produkte.

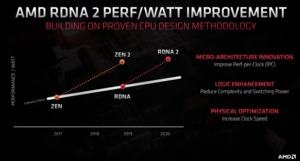

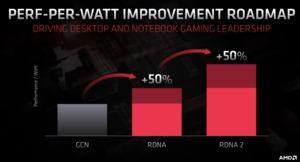

In diesem Jahr werden die ersten Grafikkarten auf Basis der RDNA-2-Architektur auf den Markt kommen. AMD spricht von später im Jahr 2020, also der zweiten Jahreshälfte. Diese werden Variable Rate Shading und Raytracing unterstützen. Zudem bietet die Architektur eine höhere IPC-Leistung, soll Logic-Verbesserungen enthalten, was die Effizienz steigert und wird höhere Taktraten ermöglichen. AMD plant eine um 50 % höhere Leistung gegenüber den Radeon-Karten auf Basis der RDNA-Architektur.

Die RDNA-2-Architektur wird Raytracing unterstützen und soll dabei vieles besser machen, als die Konkurrenz. So sieht AMD die bisherige Umsetzung der Raytracing-Effekte als zu langsam – es gibt schlichtweg zu wenige Spiele, die davon Verwendung machen. Zudem sei der Leistungsverlust durch die Anwendung der Raytracing-Effekte zu groß und stoße daher auf eine gewisse Ablehnung.

Mit der eigenen Umsetzung will man dies besser machen. Durch die Raytracing-Unterstützung in den Konsolen sollen mehr und mehr Spiele mit den Effekten erscheinen, wovon auch die PC-Spieler profitieren. Zudem sollen die Schnittstellen einfacher sein und den Entwicklern damit den Zugang erleichtern.

Die gezieltere Auslegung der CDNA-Architektur auf das Datacenter-Segment zeigt sich durch die Ausrichtung auf eine hohe HPC- und ML-Leistung. Während im HPC-Segment mit hohen Genauigkeiten gerechnet werden muss (FP32 oder FP64), reichen für das Machine Learning Datensätze mit geringerer Genauigkeit (FP16 oder INT8) aus. Beides mit einer Architektur zur adressieren ist nicht ganz einfach. AMD spricht auch von Tensor OPS – also Operationen mit geringer Genauigkeit. Ob es auch dedizierte Recheneinheiten geben wird, bei NVIDIA sind dies die Tensor Cores, bleibt abzuwarten.