Werbung

Bereits im Herbst 2019 kündigte TSMC an, dass man bereit dazu sei, die Massenfertigung in 5 nm aufzunehmen. Im Sommer sollten die ersten Chips vom Band laufen, aktuell dürften die ausgeweiteten Tests laufen. WikiChip hat einige technischen Daten zur 5-nm-Fertigung zusammengetragen. Dazu hat man die Informationen zahlreicher Konferenzen, unter anderem der Techcon 2019, dem IEEE IEDM und der ISSCC 2020 zusammengetragen.

TSMC kann über die vorherigen Fertigungsgrößen große Fortschritte verbuchen. Gerade die Fertigung in 7 nm läuft offenbar wie am Schnürchen und die Auftragsbücher sind prall gefüllt. Ähnliches deutet sich für die Fertigung in 5 nm an, denn Apple steht als einer der Großkunden bereits in den Startlöchern und soll hohe Kapazitäten gebucht haben. Dabei muss man sich vor Augen führen, dass TSMC erst vor zwei Jahren mit der Massenproduktion in 7 nm begonnen hat.

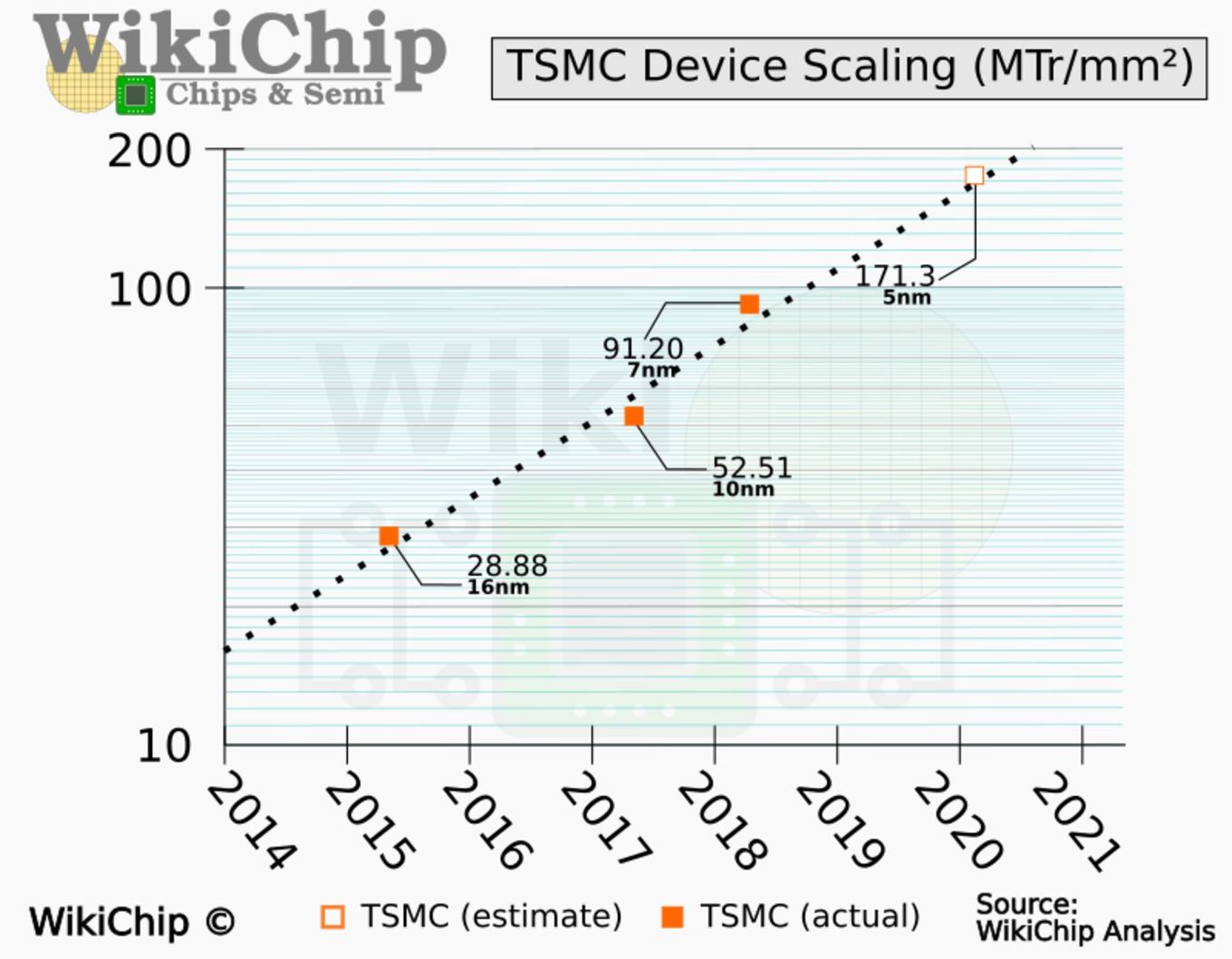

Eine Fertigungsgröße lässt sich an zahlreichen Größen festmachen. Am besten vergleichbar ist die Anzahl an Transistoren pro Quadratmillimeter. Die Packdichte bietet eine objektive Möglichkeit, die Fertigung verschiedener Hersteller in Relation zu setzen. So packt TSMC 28,88 MTr/mm² in 16 m, 52,51 MTr/mm² in 10 nm und 91,2 MTr/mm² in 7 nm. TSMC selbst spricht von einer um den Faktor 1,84 höhere Packdichte für die Fertigung in 5 nm. Damit würde man bei 167,8 MTr/mm². Der Analyse von WikiChip zufolge wird TSMC bei 171.3 MTr/mm² landen. Dies legt nahe, dass sich TSMC weiterhin auf einer nahezu linearen Steigerungskurve befindet.

Interessant ist ein Vergleich zu Intel. In 14nm++ soll Intel 37,22 MTr/mm² erreichen, in 10 nm etwa 100 MTr/mm². Samsung bewegt sich in 7 nm bei 85 bis 95 MTr/mm². Allerdings ist die Transistordichte davon abhängig, ob der Chip und die jeweilige Fertigung auf High-Performance oder Low-Power ausgelegt ist.

EUV spart Schichten ein

Ein Chip besteht nicht nur aus einer Schicht, die belichtet werden muss. Die bisherige Fertigung von TSMC basiert noch auf der DUV-Lithografie (Deep Ultra Vilolett) für die meisten Metallschichten. EUV kommt in wenigen Schichten nur in N7+ zum Einsatz. Mit der Fertigung in 5 nm (N5) wird vollständig auf die EUV-Lithografie (EUV) gesetzt. Der EUV können trotz des höheren Aufwands der Belichtung Metallschichten und Masken eingespart werden. So sind bestimmte Via- und Kontakt-Metalllayer nicht mehr notwendig.

Dadurch reduziert sich die Notwendigkeit an einer Mehrzahl an Masken. Was es mit den Masken auf sich hat, erklärte Intel kürzlich in einem interessanten Video. Diese Masken werden verwendet, um mittels einer Belichtung die Strukturen auf einen lichtempfindlichen Fotolack zu übertragen. Über chemische und physikalische Prozesse werden daraus die Transistoren und Schaltkreise entwickelt.

Ohne EUV würde die Fertigung in 5 nm etwa 115 Masken voraussetzen. Dank EUV sind es etwa 80 Masken. Die Fertigung in 7 nm mit DUV benötigt 87 Maske. Die Entwicklung und Fertigung der Masken ist extrem teuer und je mehr Masken zum Einsatz kommen, desto komplexer wird der gesamte Fertigungsprozess.

TSMC erwartet die Fertigung in 5 nm noch schneller hochfahren zu können, als dies bereits für 7 nm der Fall war – und die 7 nm laufen für TSMC schon extrem gut. Die Riscproduction wurde vor einem Jahr gestartet, insofern scheint TSMC schon belastbare Zahlen dazu zu haben. Mit der Fertigung in 5 nm setzt sich TSMC an die Spitze der Auftragsfertiger. Samsung wird erst später mit 5 nm starten und plant mit 3 nm einen nächsten großen Schritt. Zahlen zu Intels Fertigung in 7 nm gibt es aktuell nicht. Erst 2021 sollen die ersten GPUs in 7 nm bei Intel vom Band rollen.