Werbung

Gegenüber WikiChip hat Intel einige weitere Details zum Lakefield-Prozessor genannt, welcher der erste sein wird, der im 3D-Stacking das Foveros-Packaging in einen Prozessor bringt. Zuletzt tauchte ein niedrig aufgelöster Die-Shot des Compute-Dies auf und erste Benchmarks zeigen eine hohe Single-Threaded-Leistung.

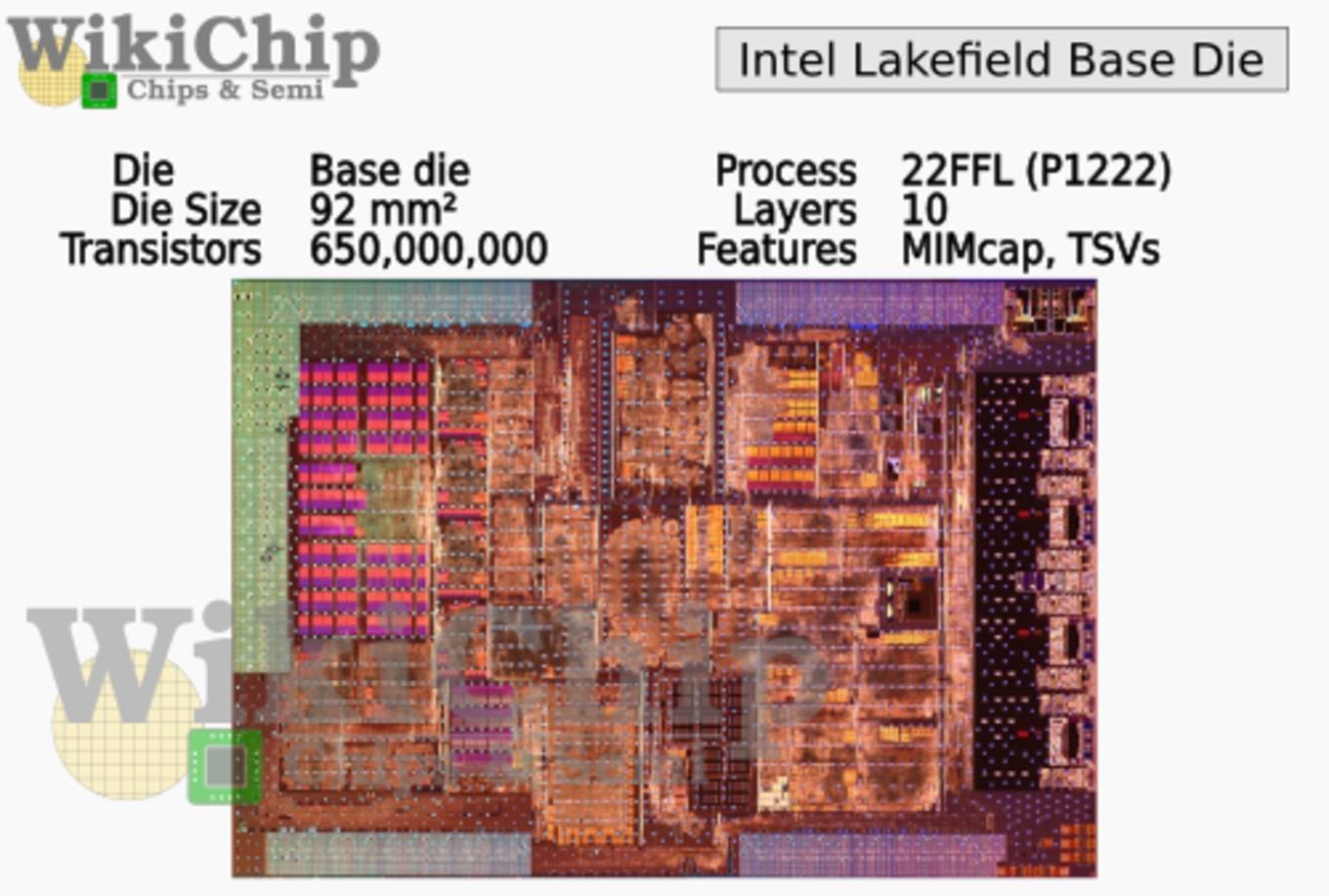

Bei WikiChip wird nun etwas ausführlicher über den Aufbau des Prozessors gesprochen. So wird der Base-Die in 22FFL gefertigt. Was zunächst nach einem eher betagten Fertigungsprozess klingt, zeigt sich bei genauerer Betrachtung als moderne Umsetzung. Der Base-Die muss vor allem auf eine möglichst geringe Leistungsnaufnahme optimiert sein und hier hat 22FFL mit den Erkenntnissen der mehrfach optimierten Fertigung in 14 nm seine Stärken. Der Base-Die beinhaltet Komponenten wie das USB-3-Interface, das Audio, SDIO, das PCI-Express-3.0-Interface sowie weitere I/O-Komponenten.

Der Base-Die hat eine Fläche von 92 mm², besteht aus zehn Metallschichten und muss neben einer geringen Leistungsaufnahme auch günstig zu fertigen sein. Dazu trägt auch das einfache Back End of Line (BEOL) bei, welches nur noch eine Belichtung pro Maske notwendig macht.

Der Base-Die ist im Grunde genommen ein aktiver Interposer. Er kommt trotz der vergleichsweise großen Fläche (verglichen zum Compute-Die) auf nur 650 Millionen Transistoren.

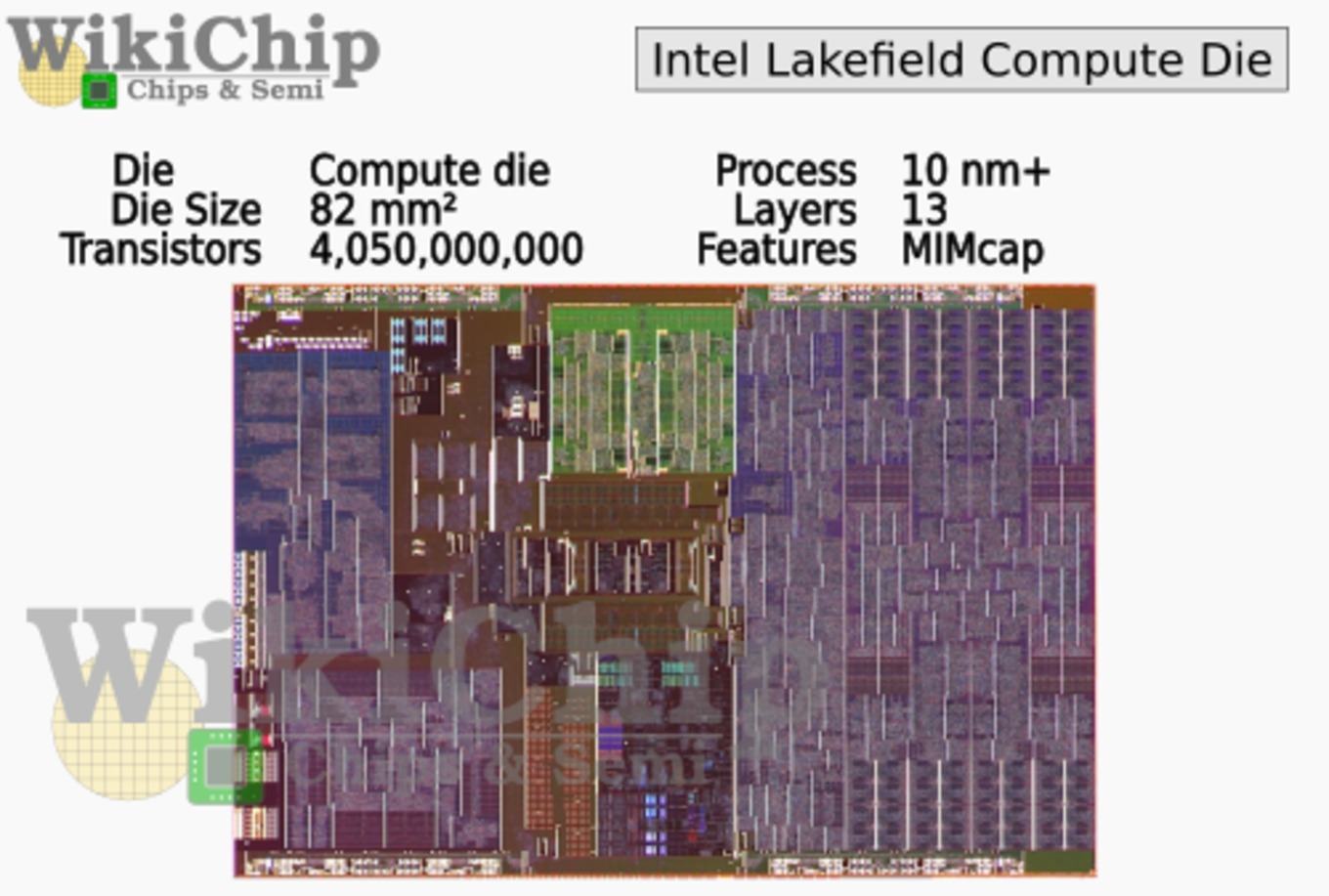

Der Compute-Die mit den vier Tremont-Kernen, dem Sunny-Cove-Kern sowie der Gen11-Grafikeinheit (plus die Gen11.5 Display-Engine und die Imaging Processing Unit (IPU) 5.5) sitzt über dem Base-Die und kommt auf eine Fläche von 82 mm². Hier verrät Intel auch erstmals die Anzahl der Transistoren. Knapp über 5 Milliarden sollen es sein. Der Compute-Die wird in 10 nm+ gefertigt. Dabei handelt es sich um die zweite Generation des 10-nm-Fertigungsprozesses von Intel, der auch für die Tiger-Lake-Prozessoren zum Einsatz kommen soll.

Auf dem Compute-Die setzt Intel auf einen Ring-Interconnect. Dieser bindet den System Agent mit den fünf Kernen und der GPU an. Die einzelnen Ring-Stops, so der Namen der Anknüpfungspunkte in einem Ring-Interconnect, sind der Sunny-Cove-Kern, die vier Tremont-Kerne, die GPU und die Uncore-Komponenten.

Der Compute-Die bietet wie gesagt eine Fläche von 82 mm². Rechts in lila ist die integrierte GPU zu erkennen, die auf der Gen11-Graphics basiert. Die GPU belegt bereits etwa 40 % der Chipfläche. Der mittig unterliegende Bereich stellt den Sunny-Cove-Kern dar, welcher der High-Performance-Kern im Lakefield-Prozessor ist. Im mittleren grünen Segment befinden sich die vier Atom-Kerne auf Basis der Tremont-Architektur. Das linke Drittel wird durch die zahlreichen Uncore-Komponenten belegt. Intel hat hier etwas Platz gespart, da man das Thunderbolt-3- und PCI-Express-3.0-Interface auf dem Base-Die untergebracht hat.

Mit dem Lakefield-Prozessor setzt Intel erstmals auf ein Hybrid-Design, bestehend aus einem großen Sunny-Cove-Kern und den vier Tremont-Kernen. Insgesamt stehen also fünf Kerne zur Verfügung. Das Hyperthreading ist sowohl auf dem Sunny-Cove-Kern als auch in den vier Tremont-Kernen nicht aktiv. Dem Sunny-Cove-Kern wurde zudem seine AVX512-Funktionalität genommen, um eine gewisse ISA-Kompatibilität zwischen den unterschiedlichen Kernen gewährleisten zu können.

Interessant sind auch die Leistungsdaten, die Intel nennt. So soll ein einzelner Tremont-Kerne in etwa 70 % des Leistungsniveaus des Sunny-Cove-Kerns erreichen. Hinsichtlich der Effizienz schlägt der Atom-Kern seinen großen Bruder. Für Multi-Threaded-Anwendungen soll daher das Quad-Core-Cluster, bestehend aus den vier Tremont-Kernen zum Einsatz kommen, während Single-Threaded-Anwendungen auf dem Sunny-Cove-Kern laufen. Das Zusammenspiel aus Hard- und Software muss also darauf ausgelegt sein, die Stärken des Lakefield-Prozessors jeweils ausnutzen zu können.

Von den insgesamt 82 mm² Chipfläche des Compute-Die belegt das Tremont-Cluster etwa 5,14 mm² – inklusive 1,5 MB an L2-Cache. Ein einzelner Tremont-Kern kommt auf 0,88 mm². Der einzelne Sunny-Cove-Kern hingegen bringt es auf 4,49 mm² – inklusive 512 kB an L2-Cache. Für Intel bietet sich daher in diesem Bereich eine interessante Mischung aus Leistung, Verbrauch und belegter Chipfläche. Der Sunny-Cove-Kern hat allerdings auch den Nachteil, dass beispielsweise die AVX512-Funktionseinheiten weiterhin vorhanden sind, aber nicht genutzt werden.

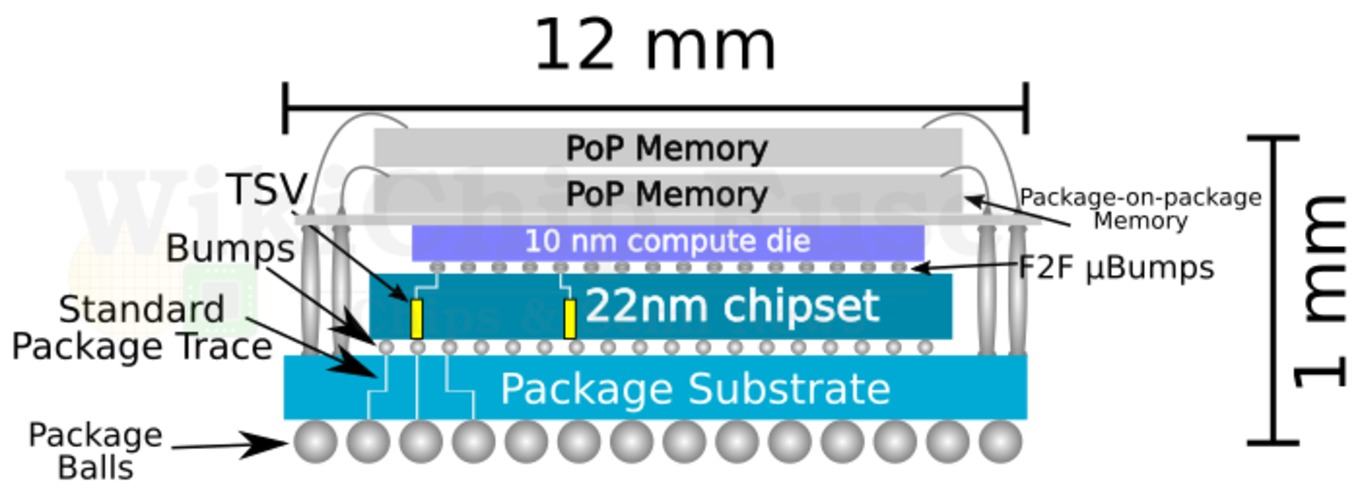

Die Kommunikation zwischen dem Base- und dem Compute-Die erfolgt über das Foveros Die Interface (FDI). Die FDI-I/O-Zellen sitzen direkt unterhalb der Micro-Bumps, um ESD- und weitere negative Effekte zu minimieren. Die Transceiver- und Receiver-Elemente befinden sich auf dem Base-Die. Die Datenrate pro Pin ist mit 500 MT/s nicht besonders hoch, allerdings spricht das FDI gleich 200 Kanäle an und erreicht damit eine Übertragungseffizienz von 0,2 pJ/Bit. Projektiert war der FDI mit 0,15 pJ/Bit, allerdings will Intel für zukünftige Produkte noch an Verbesserungen arbeiten. Zum Vergleich: Der CoWoS von TSMC kommt auf 0,56 pJ/Bit und AMDs Infinity Fabric auf 2 pJ/Bit (weniger ist besser).

Über dem Base- und dem Compute-Die sitzten in zwei Schichten noch zwei oder vier Stacks an LPDDR4-Speicher, die ebenfalls über TSVs mit dem Compute-Die verbunden sind. Es handelt sich dabei um sogenannten PoP (Package over Package).

Für Intel ist Lakefield mit dem Foveros-Packaging ein Test-Vehicle, an dem die neuen Technologien getestet werden können. Ein Prozessor wie Lakefield bietet sich mit seinen relativ kleinen Stückzahlen für einen solchen Zweck an. Das gesamte Package kommt auf 12 x 12 mm in Breite und Tiefe und eine Höhe von 1 mm.

2nd Gen Foveros für Ponte Vecchio HPC-Beschleuniger

Die ersten Geräte, die einen Lakefield-Prozessor verwenden werden, sind das Microsoft Surface Neo, das Samsung Galaxy Book S und das Lenovo ThinkPad X1 Fold. Allesamt sind diese Geräte jedoch noch nicht erschienen. Derzeit spricht Intel auch noch nicht über eine zweite Generation.

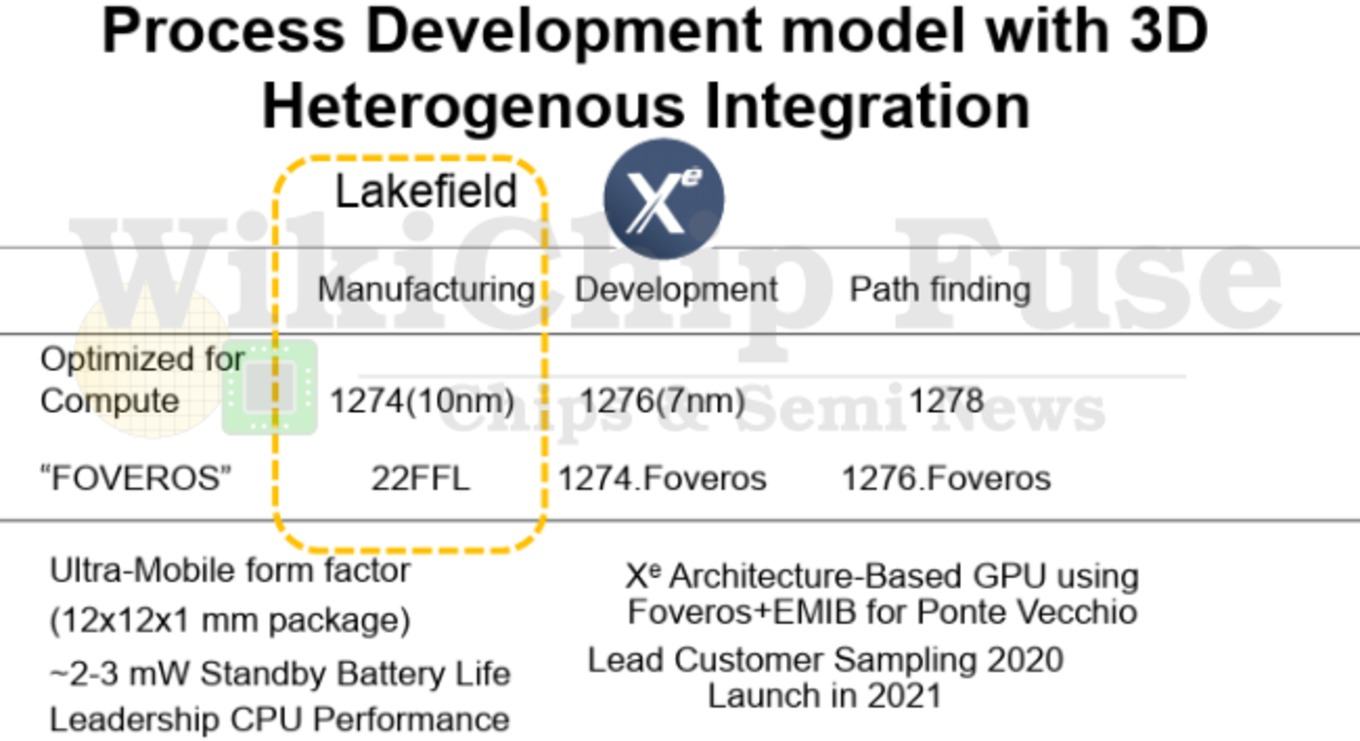

Allerdings wird es natürlich eine Weiterentwicklung der Foveros-Technil geben. In Co-EMIB wird Intel die bestehende Interconnect-Technologie mit Foveros zusammenbringen und kann das Design damit noch einmal deutlich flexibler gestalten. Der HPC-Beschleuniger Ponte Vecchio auf Basis der Xe-HPC-Architektur wird das erste Produkt sein, welches diese Weiterentwicklung verwenden wird.

Der Compute-Die wird dann in 7 nm (1276) gefertigt und der Base-Die soll in einer verbesserten 10-nm-Fertigung (1274.Foveros) hergestellt werden. Das Sampling soll bereits Mitte 2020 erfolgen, das fertige Produkt wird 2021 auf den Markt kommen. Auch für den weiteren Weg hat Intel bereits Pläne und spricht von einer Fertigung in 1278 (5 nm?) für den Compute-Die und 1276.Foveros. Hier spielt Intel die Entkopplung der Fertigungstechnologien für solche Chip aus, die man auf dem Architecture Day 2018 ausgerufen hat.

Auf wikichip.org finden sich noch zahlreiche weitere derartige Analysen.