Werbung

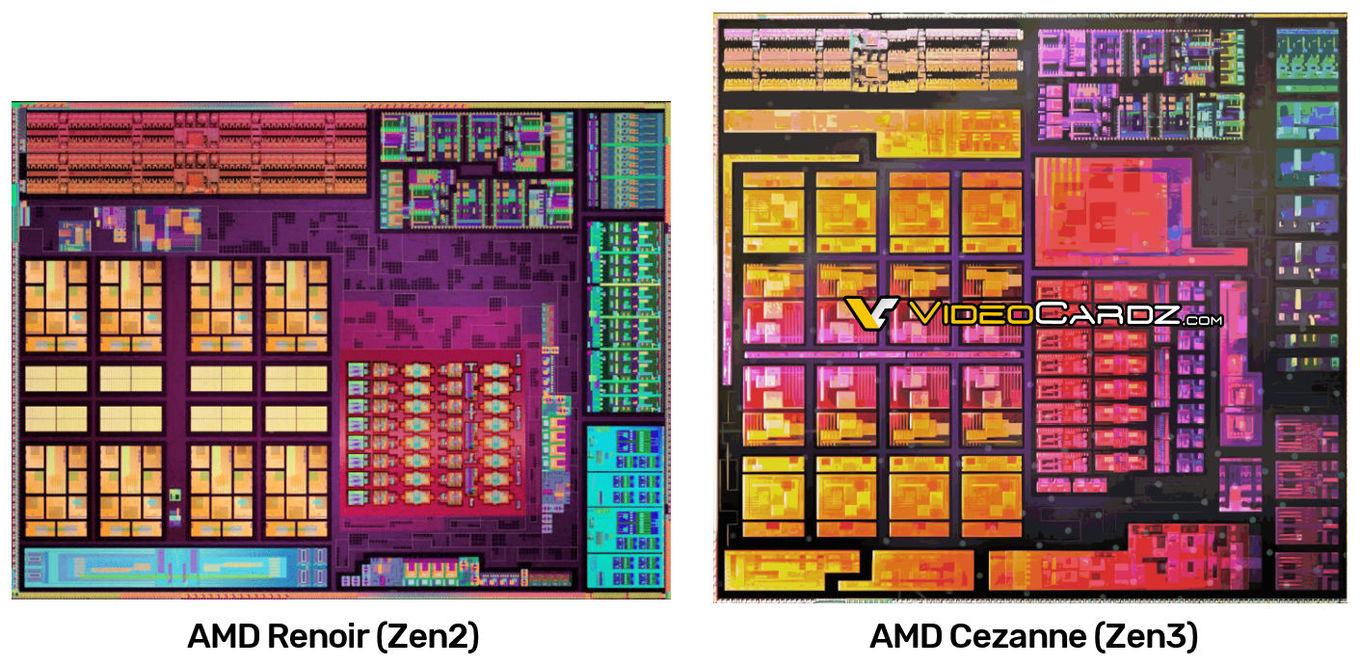

Das Auftauchen eines schematischen Blockdiagramms eines Ryzen-5000-Prozessors auf Basis des Cezanne-Designs erlaubt offenbar einige weitere Rückschlüsse auf die Prozessoren. Videocardz hat das Blockdiagramm dem aktuellen Renoir-Design gegenübergestellt.

Die Cezanne-Prozessoren sollen bis zu acht Zen-3-Kerne und acht Compute Units auf Basis der Vega-Architektur verwenden. Hinsichtlich der Kerne und CUs ist der Vollausbau damit identisch zu den Renoir-Prozessoren, die allerdings Zen-2-Kerne verwenden. Im Blockdiagramm sind größere Änderungen erkennbar, die sich nicht allesamt mit dem Zen-3-Design und größeren Caches erklären lassen.

| L2- / L3-Cache | Die-Size (SoC/CCD) | Transistordichte | |

| Renoir | 4 MB / 8 MB | 156 mm² | 62,82 MTr/mm² |

| Matisse | 4 MB / 32 MB | 74 mm² | 52,70 MTr/mm² |

| Cezanne | 4 MB / 16 MB | ? | ? |

| Vermeer | 4 MB / 32 MB | 80,7 mm² | 51,43 MTr/mm² |

Der größte Unterschied zwischen dem Desktop-Design (Matisse) und dem Mobile-Design (Renoir) auf Basis der Zen-2-Architektur waren im halbierten L3-Cache zu finden. Ein Renoir-Prozessor besitzt schlussendlich 9,8 Milliarden Transistoren. Die Größe des Chips beläuft sich auf 156 mm². Allesamt werden die oben genannten Prozessoren bei TSMC in 7 nm gefertigt werden. AMD greift dabei auf ein Verfahren namens "Deep Ultraviolet (DUV) Photolithography" zurück – man kommt also noch ohne EUV-Belichtung (Extreme ultraviolet) aus.

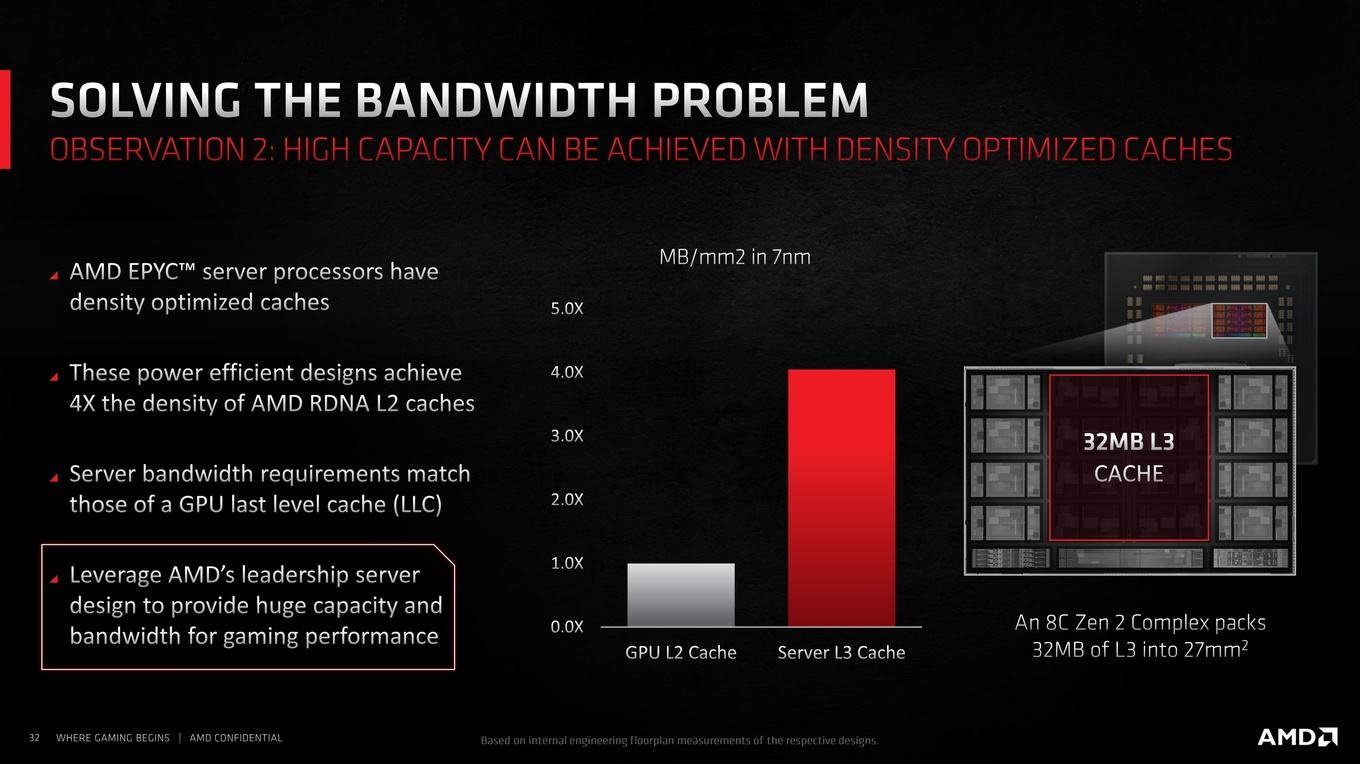

Für Cezanne wird der L3-Cache im Vergleich zu Renoir auf 16 MB verdoppelt, wird aber noch immer nur halb so groß wie beim aktuellen Desktop-Design (Vermeer) sein. Im Vergleich zwischen Matisse und Vermeer sieht man, dass der CCD von 74 auf 80,7 mm² angewachsen ist, was mit den Änderungen im Zen-3-Design zusammenhängt. Alleine die 32 MB an L3-Cache belegen 27 mm² an Platz. Entsprechend dürften es für 16 MB etwa 13,5 mm² sein.

Aktuell kennen wir noch keine Daten wie die Anzahl der Transistoren und die Größe der Cezanne-Prozessoren. Laut ersten Schätzungen anhand des Blockdiagramms dürfte Cezanne auf etwa 175 mm² kommen, was sicherlich in Teilen auch am größeren L3-Cache zu begründen ist.

Die Zen-3-Architektur und die damit verbundenen Änderungen in der Cache-Hierarchie haben offenbar Auswirkungen auf das gesamte Design und die Größe des Chips. Es dürfte jedoch noch weitere Faktoren geben. So limitierte AMD die Renoir-Prozessoren auf PCI-Express 3.0 und den mobilen Varianten stehen außerdem nur acht anstatt der sonst frei verfügbaren 20 Lanes zur Verfügung. Begründet wird dies mit dem geringeren Stromverbrauch, was natürlich im mobilen Segment von besonderer Bedeutung ist.

Ob die Cezanne-Prozessoren PCI-Express 4.0 unterstützen werden, ist nicht bekannt. Es dürfte wieder eine 16+4+4-Konfiguration für die Lanes geben, ob AMD diese für die mobilen Varianten wieder auf acht für die Anbindung einer dedizierten GPU beschränkt, ist ebenso unbekannt. Die Desktop-Varianten von Cezanne werden sicherlich wieder mehr PCI-Express-Lanes als die mobile Variante bieten.

Am 11. Januar wird AMD eine Keynote zur CES 2021 veranstalten. Dort wird die Vorstellung der Cezanne-Prozessoren und der dazugehörigen Notebooks erwartet. Diese sollen dann mit den mobilen Ampere-GPUs von NVIDIA kombiniert werden. Ab wann die entsprechenden Notebooks verfügbar sein werden, steht jedoch noch in den Sternen. Es deutet sich jedoch an, dass wir bei den mobilen Ryzen-Prozessoren eine angespannte Liefersituation sehen werden, die sich zusammen mit den ebenfalls knappen Ampere-GPUs auf den gesamten Notebook-Markt auswirken werden. Teilweise werden die Notebooks daher weiterhin mit Ryzen-4000- und Core-10000-Prozessoren – also der bisherigen Generation – bestückt werden.