Werbung

Im Rahmen des Technology Symposium hat der Auftragsfertiger TSMC über den aktuellen Stand der Technik informiert. Das Portfolio an Fertigungstechnologien wird grob in die Fertigung in 7 nm (N7), 5 nm (N5) und 3 nm (N3) aufgeteilt. Inzwischen bezeichnet TSMC die Fertigung in 7 nm als ausgereift und seit etwa 2018 wurden bereits über eine Milliarde Chips in dieser Strukturgröße gefertigt und ausgeliefert.

2020 machte die N7-Fertigung etwa 50 % des Volumen aus. Zirka 40 % fielen auf 16 nm und größer, während die Fertigung in 5 nm nur einen kleinen Teil des Gesamtvolumens ausmachte, wenngleich man hier mit Apple einen Großkunden hat, den man mit entsprechenden Chips beliefert. Für 2021 ändert sich im Gesamtvolumen der Fertigung in 7 und 16 nm wenig, dafür wird das Volumen für Wafer in 5 nm deutlich hochgefahren, womit auch die Gesamtkapazität steigt. Den Ausstoß an Wafern konnte TSMC in den vergangenen Jahren bereits deutlich steigern. Von 2018 ausgehend verdoppelte sich 2019 das Volumen bei den 300-mm-Wafern, 2020 betrug es Faktor 3,5 gegenüber 2018 und in diesem Jahr will man viermal mehr Wafer ausliefern als vor drei Jahren.

Diese Faktoren sollen sich 1:1 auf die Fertigung in 5 nm übertragen lassen, hier ging es allerdings erst 2020 los. 2023 will TSMC dementsprechend viermal mehr Wafer als 2020 ausliefern, die in 5 nm belichtet sind.

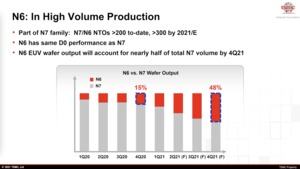

Langsam aber sicher soll die Fertigung in 6 nm (N6) die Fertigung in 7 nm ablösen. TSMC setzt hier für mehr und mehr Layer die Belichtung mittels EUV ein. Große Sprünge im Hinblick auf die Leistungsaufnahme, Packdichte und/oder Leistung gibt es zwar nicht, für TSMC und die Kunden bieten solche Weiterentwicklungen aber vor allem größere Volumina durch den Reifeprozess in der Entwicklung.

Für das vierte Quartal 2020 betrug der Anteil der N6-Fertigung im Vergleich zu N7 etwa 15 %. Ein Jahr später, also für das Q4 2021, soll bereits die Hälfte in N6 stattfinden.

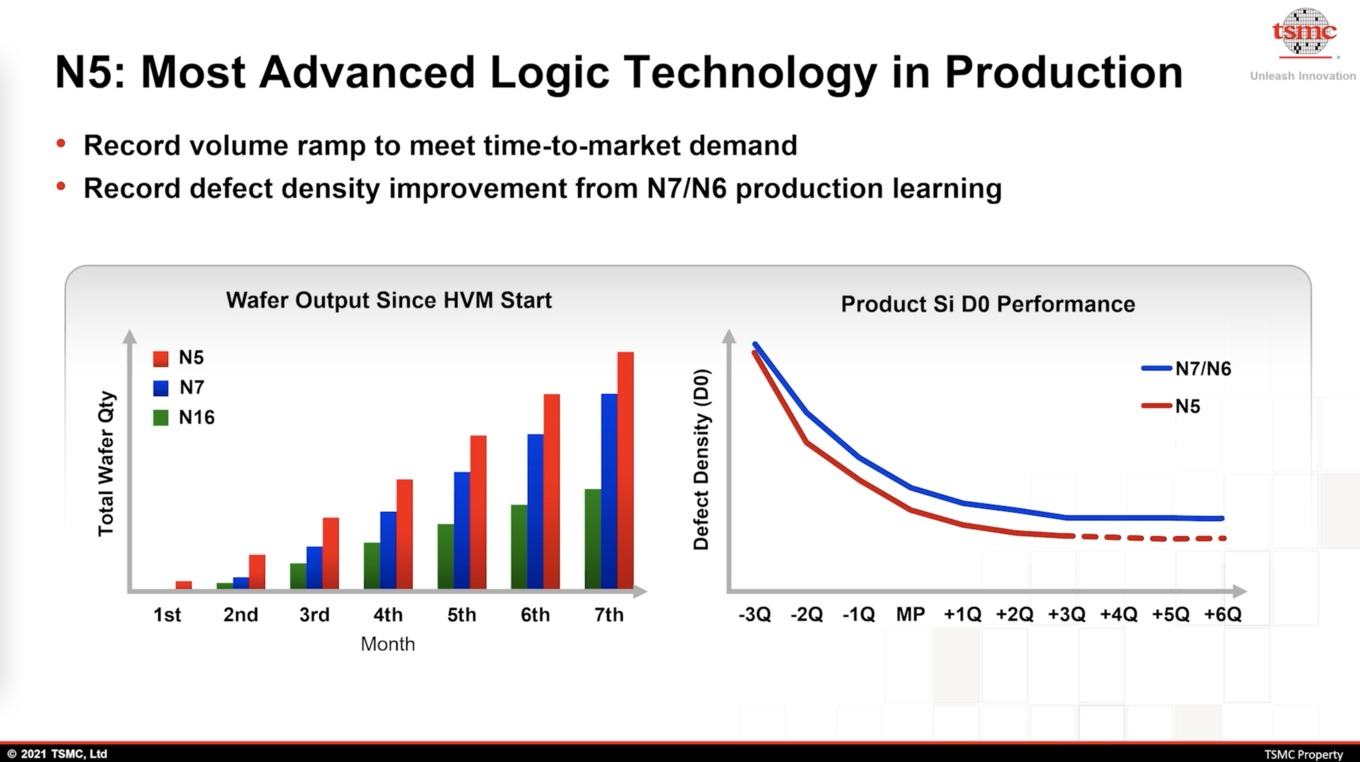

N5 läuft besser als alles andere zuvor

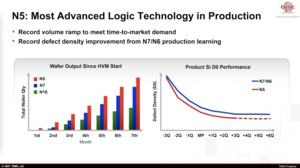

Die Fertigung in 5 nm wird über die kommenden Jahre das Volumengeschäft bei TSMC sein. Bereits jetzt erreicht man bessere Defektraten, als dies bei jeder anderen Strukturgröße bisher der Fall war. Die Ausbeute ist also bereits zu einem recht frühen Zeitpunkt sehr hoch.

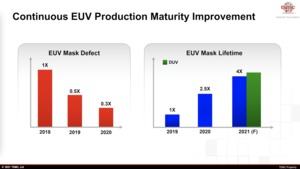

Besonders stolz ist man außerdem auf die Effizient, die man hier erreicht. Obwohl nur rund 50 % der EUV-Maschinen bei TSMC stehen, versorgt man damit 65 % des Marktes an mittels EUV belichteten Chips. Hinzu kommt, dass man nicht nur bei den DUV-Masken (Deep Ultraviolet) eine lange Lebensdauer erreicht, sondern diese Erfahrungen nun auch für die EUV-Masken (Extreme Ultraviolet) umsetzen kann, was die Effektivität (Umrüstzeiten der Belichtungsmaschinen) weiter erhöht.

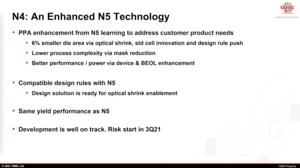

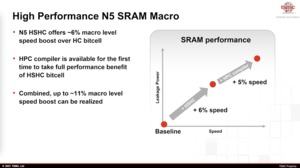

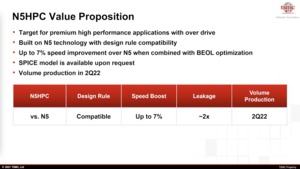

Für die nähere Zukunft sieht TSMC die Fertigung in 4 nm (N4) vor, die allerdings ähnlich wie die N6-Fertigung keine großen Schritte im Hinblick auf die Leistung und/oder Leistungsaufnahme macht, sondern nur einen optischer Shrink im Bereich von 6 % darstellt. Im dritten Quartal 2021 soll die erste Risk-Produktion in N4 starten.

N3 ab 2022 verfügbar

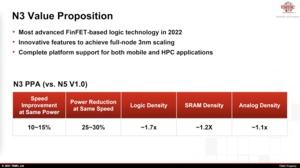

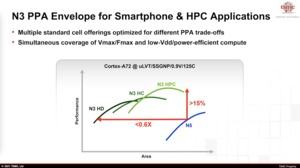

Für die Fertigung in 3 nm sieht TSMC den Start in 2022 vor. Größere Volumen werden allerdings erst für Ende 2022 erwartet. Im Vergleich zur N5-Fertigung soll die Leistung der Chips bei gleicher Leistungsaufnahme um 10 bis 15 % steigen. Auf der anderen Seite kann bei gleicher Leistung die Leistungsaufnahme um 25 bis 30 % gesenkt werden. Die Transistordichte steigt im Logikbereich um den Faktor 1,7 an, beim SRAM soll es Faktor 1,2 sein.

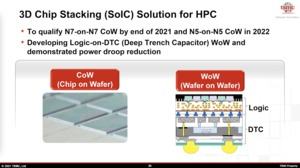

Das TSMC Technology Symposium läuft über mehrere Tage, bzw. mehrere Sessions und sicherlich wird TSMC zum Packaging noch einige Details veröffentlichen. Aber dazu dann mehr in einer gesonderten Meldung.