Werbung

Auf der Future Sumnmits 2022 sprach der CEO des Imec (Interuniversity Microelectronics Centre) Luc Van den hove über die Herausforderungen und möglichen Lösungen der Fertigung für Strukturbreiten von 1 nm und weniger – allgemein als Ångström-Ära bezeichnet. Dieser Begriff wird nicht nur von Intel in Form der Bezeichnungen Intel 20A und Intel 18A verwendet, sondern dürfte in den kommenden Jahren von vielen Herstellern für die entsprechenden Prozessgrößen verwendet werden.

Neue Materialien, fortschrittliche Belichtungstechnik und die Entwicklung neuer Fertigungstechniken für immer kleinere Strukturen und eine höhe Integrationsdichte sollen die Richtigkeit von Moore's Law fortführen. Das imec ist eines der größten Forschungszentren im Bereich der Halbleiterindustrie. Einige der Erkenntnisse und Beschreibungen neuer Techniken decken sich mit dem, das wir bisher von Intel, ASML, TSMC, Samsung und Co. gehört haben.

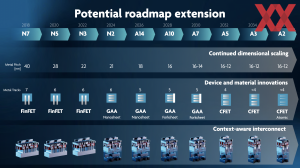

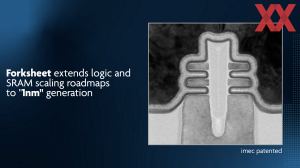

Zunächst einmal wurde im Vortrag die Entwicklung neuer Fertigungstechniken beschrieben. Der FinFET hat uns über Jahre gute Dienste geleistet, ab einer Fertigung von 2 bis 3 nm wird er aus technischer Sicht jedoch keinerlei Zukunft mehr haben. An seine Stelle treten Gate-All-Around-Fets (GAA), die von Samsung bereits in diesem Jahr in die Massenproduktion gehen sollen. Ab Intel 20A will der Chipriese seine eigene Fertigung auf die hier als RibbonFET bezeichneten neuen Transistortypen umstellen. Mehrere Transistoren neben- und übereinander zu stapeln, ist ein Weg, sie direkt ineinander übergehen zu lassen, ein weiterer. Beim Forksheet-Design liegen p- und n-Kanal-Transistor nebeneinander, nur noch durch eine dünne Wand voneinander getrennt. Dies reduziert die Leiterebenen, die notwendig sind, um die Transistoren zu verschalten. Die kleineren Strukturen sind in der Fertigung allerdings eine Herausforderung.

Für 2028 bis 2030 projiziert Imec den Einsatz der Forksheet-Transistoren. Hier sind wir bereits in der Ångström-Ära angekommen. Ein Ångström entspricht dem zehnmillionsten Teil eines Millimeters – also 0,1 nm.

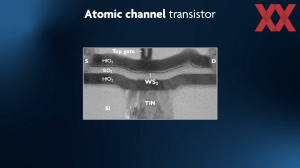

Ab 2032 sollen dann Combined Fets (CFet) zum Einsatz kommen. Bei diesen wird der Forksheet-Design in der vertikalen Ebene gestapelt. Für alles, das danach kommt, wird aktuell bereits ein riesiger Forschungsaufwand betrieben, denn es müssen neue Materialien gefunden werden, um Strukturen mit einer Dicke von nur wenigen Atomen realisieren zu können. Ruthenium und Wolfram-Sulfid (WS2) sollen geringere Leckströme ermöglichen, bzw. sind dann hoffentlich in der Lage als Isolator eingesetzt zu werden.

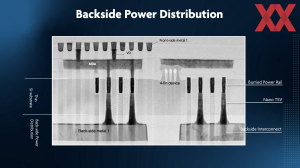

An dieser Stelle wird es darauf ankommen, wie die Hersteller den Aufbau der Chips umstellen. Aktuell wird der Wafer von einer Seite belichtet. Künftig werden Stromversorgung und Datenleitungen von zwei Seiten aufgebaut. Erst werden die Transistoren und dazugehörigen Datenleitungen gefertigt, dann der Wafer abgeschliffen und eine Durchkontaktierung hergestellt, damit die Spannungsversorgung aufgebaut werden kann. Die Komplexität in der Fertigung steigt also deutlich. Intel nennt dies PowerVia. TSMC, Samsung und andere Hersteller haben eigene Begriffe für dieses Design.

Einerseits können die Transistoren damit enger zusammengepackt werden, was die Dichte erhöht. Auf der anderen Seite können Signalintegrität und die einfachere Struktur im Aufbau so gewährleistet werden.

3D-Chips und riesige Belichtungsmaschinen

Ein nächster Schritt, der bereits heute teilweise angewendet wird, ist das Stapeln der verschiedenen Designs. AMD setzt bereits einen SRAM-Chip auf seine Kerne. Intel verbaut für Ponte Vecchio einen Base Tile mit I/O- und Cache-Komponenten. Diese Methodik wird immer weiter ausgeweitet werden.

Eine weitere wichtige Rolle kommt den Herstellern der Belichtungstechnik zu. ASML kommt hier als Branchenprimus eine wichtige Rolle zu. High-NA-EUV soll mit einer numerischen Apertur (NA) den Metal Pitch, also den Abstand zwischen den kleinstmöglichen Leitern, auf bis zu 12 nm schrumpfen können.

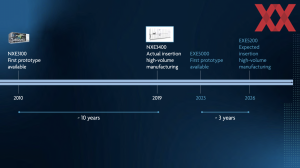

Die ersten High-NA-EUV-Maschinen sollen 2023 fertig auf- und eingestellt sein. Ab 2026 soll dann die Massenfertigung erster Prozesse beginnen. ASML soll bereits an der nächsten Generation arbeiten, denn auch die Entwicklung solcher Maschinen dauert mindestens ein Jahrzehnt.