Werbung

Auf dem Technology Symposium 2022 sprach TSMC über seine Pläne hinsichtlich der kommenden Fertigungsschritte. Während der Fokus in den kommenden Jahren auf auf Fertigung in diversen N3-Varianten liegen wird, steht mit N2 der Wechsel von den FinFETs auf GAA-Transistoren an.

Mit N2 wird TSMC aber noch nicht direkt auf die Backside Power Delivery (BPD), sprich die Strom- und Spannungsversorgung durch die Rückseite des Wafers, umsteigen. Im Rahmen der Vorstellung der nächsten Fertigungsschritte bei Intel sind wir auf die Methodik der Backside Power Delivery bzw. Backside Power Rails genauer eingegangen. Intel nennt dies PowerVias. Während Intel die PowerVias mit dem Einsatz von Intel 20A vorsieht und zugleich von den FinFETs auf GAA bzw. RibbonFETs wechselt, will TSMC die neuen Techniken stufenweise einführen. N2 wird demnach zunächst mit einer klassischen Versorgung umgesetzt - dies berichten die Kollegen von Anandtech.

Bisher hat sich TSMC noch nicht weiter zum N2-Prozess geäußert. Die Projektionen der Optimierungsschritte darf man aber durchaus als konservativ bezeichnen. Für N2 will TSMC im Vergleich zu N3E die Leistungsaufnahme um 25 bis 30 % reduzieren. Die Performance soll um 15 bis 26 % steigen. Zugleich peilt TSMC eine Packdichte der Transistoren um den Faktor 1,1 an.

Die moderaten Steigerungen könnten mit der fehlenden BPD zu tun haben. TSMC wird aber sicherlich auch wieder mehreren Varianten von N2 anbieten – dann auch eine mit BPD, die dann in einigen Bereichen sicherlich auch noch einen weiteren Sprung machen wird.

Intel wählt einen anderen Weg. Theoretisch ist von Intel 3 zu Intel 20A ebenfalls der Wechsel der Transistor- und Versorgungs-Technologie vorgesehen – von FinFET zu RibbonFET sowie der Einsatz von PowerVias.

Intel führt dazu eine interne Test-Fertigung ein, die das Risiko reduzieren soll, aber eben nur intern zur Verfügung steht und vermutlich nicht einmal von Intel selbst genutzt wird. Auch hier teilt man das Risiko also auf.

Samsung startet GAA-Fertigung

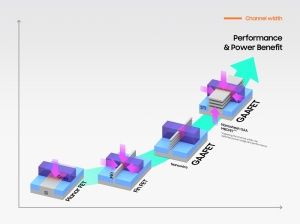

Laut eines Berichts aus Südkorea startet Samsung am 30. Juni die Fertigung in 3 nm mit GAA-Transistoren. Dabei dürfte es sich um 3GAE (3 nm Gate-All-Around Early) handeln, während 3GAP (3 nm Gate-All-Around Plus) kurz darauf folgen soll. Den Startschuss auf den 30. Juni zu legen versetzt Samsung in die Lage sagen zu können, dass die Fertigung noch im zweiten Quartal bzw. ersten Halbjahr 2022 angelaufen sei.

Ebenfalls aus Südkorea stammen Berichte nach denen ASICs für Bitcoin-Miner die ersten Chips sein werden, die in 3GAE gefertigt werden. Aufgrund der geringen Komplexität und Stückzahlen bieten sich solche Chips auch tatsächlich an, für eine frühe Phase der Fertigung genutzt zu werden. Ob die ersten Kunden tatsächlich aus dem Geschäftsfeld des Bitcoin-Mining stammen, wird zunächst ein Geheimnis bleiben, denkbar wäre es aber.

Update:

Wie erwartet hat Samsung heute den Start der Massenproduktion des 3-nm-Prozesses mit GAA-Transistoren angekündigt. Gegenüber einem nicht näher spezifizierten 5-nm-Prozess will Samsung eine um 45 % reduzierte Leistungsaufnahme oder eine um 23 % höhere Leistung erreichen. Zugleich kann Samsung die Transistoren um 16 % dichter packen.

Die ersten Chips aus diesem Prozess sollen für "High Performance, Low Power Computing" gedacht sein. Samsung plant aber bereits die Fertigung von mobilen Prozessoren.