Werbung

Vor der eigentlichen Präsentation auf der Hotchips 34 hat Intel bereits eine Vorschau auf eben diese gegeben und dabei einige Details zur Fertigung von Meteor Lake verraten, die bisher noch nicht bekannt waren. Mit Meteor Lake wechselt Intel für den Desktop- und Mobile-Bereich auf eine deintegrierte Struktur – sprich es kommt kein einzelner Chip mehr zum Einsatz, sondern mehrere Chiplets.

Damit einher geht eine breit aufgestellte Chiplet-Fertigung bei mehreren Herstellern, was vor einigen Jahren für Intel noch undenkbar gewesen wäre. Allerdings gab es in den vergangenen Wochen Gerüchte, dass es aufgrund eines Wechsels in der Fertigung bei TSMC zu Verzögerungen kommen werde. Diesen widerspricht Intel nun vehement und will Meteor Lake wie geplant 2023 auf den Markt bringen. Die Fertigung der einzelnen Chiplets soll in den zuvor geplanten Nodes stattfinden.

Basierend aus Quellen aus der Industrie ist damit nun klar, wie Meteor Lake aufgebaut sein wird:

- Compute-Tile (mit den CPU-Kernen:): Intel 4

- GPU-Tile: TSMC N5

- SoC-Tile: TSMC N6

- I/O-Tile: TSMCN6

- Base-Tile (mit Foveros-Interconnect): Intel 22FFL

In seiner Vorschau zeigt Intel zudem einen Floor-, bzw. Package-Plan, welcher die einzelnen Chiplets in ihrer Größe und Seitenverhältnissen zeigt. Es handelt sich um Meteor Lake-P, also die Desktop-Variante. In dieser Konfiguration kommen acht Performance- und acht Efficiency-Kerne zum Einsatz.

Das desintegrierte Chip-Design mit den Chiplets macht Intel in zweierlei Hinsicht flexibel. Einerseits kann man über die Anzahl und die Zusammenstellung der Chiplets festlegen, wie der Prozessor letztendlich aussehen soll. Über eine gewisse Streuung der Fertigung zwischen Intel und TSMC sollen Risiken in der Fertigung minimiert werden.

Neben Meteor Lake werden Arrow Lake und Lunar Lake auf diese Strategie setzen. Daneben setzt Intel für die Xeon-Prozessoren auf Basis von Sapphire Rapids auf mehrere Chips und auch die FPGAs binden mehrere Chiplets mittels EMIB, bzw. Foveros an. Der GPU-Beschleuniger Ponte Vecchio wird in den kommenden Monaten für das Packaging die Vorreiterrolle übernehmen.

In einem nächsten Schritt sollen die Plattformen dann für Universal Chiplet Interconnect Express oder kurz UCIe vorbereitet sein, sodass auch externe Chiplets angebunden werden können, bzw. die Vielfalt an Möglichkeiten und Kombinationen noch einmal deutlich zunimmt.

Weitere Details werden zu Präsentation von Intel auf der Hotchips 34 erwartet, die morgen stattfinden wird. Wir werden diese Meldung dann entsprechend ergänzen.

Update: Weitere Details

Nach der Vorschau zur Hotchips hat Intel auf dem eigentlichen Vortrag zu Meteor Lake und dessen Nachfolgern noch einige weitere interessante Details veröffentlicht. So wissen wir, dass Intel auf vier aktive Komponenten setzt (Compute File, GPU-Tile, SoC-Tile und I/O-Tile) die es je nach Anforderungsprofil für die Hardware, also ob es sich um einen Prozessor für den ultramobilen Bereich oder den Desktop handelt, anpassen kann. Diese Variabilität hat Intel aber noch einmal genauer ausgeführt.

So sieht man für Meteor Lake beispielsweise einen Compute-Tile mit den eigentlichen CPU-Kernen vor, der über sechs P-Cores und 2x 4 E-Cores verfügt. Für dien ultramobilen Bereich wird es aber auch eine Variante mit zwei P-Cores und ebenfalls 2x 4 E-Cores geben. Das Design ermöglicht es Intel dann aber auch in der weiteren Entwicklung nur einen Teil der Kerne in eine neue Generation zu überführen – beispielsweise nur die E-Cores. Es ist aber auch denkbar, dass man nur die Cache-Hierarchie verändert und beispielsweise den L2- und/oder den L3-Cache vergrößert. Der gesamte Compute-Tile kann natürlich in eine neue Fertigung überführt werden. Alleine im Bereich des Compute-Tile gibt es also bereits viele Variationsmöglichkeiten.

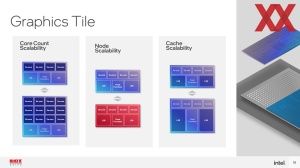

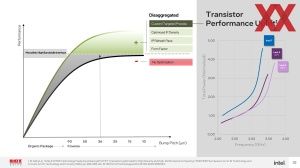

Aber dies gilt natürlich auch für den GPU-Tile, den Intel bis auf absehbare Zeit extern fertigen wird. Über die Anzahl der Xe-Cores wird die Leistung der integrierten Grafikeinheit definiert. Auch hier ist es denkbar, dass nur die Caches angepasst werden. Natürlich aber kann ich der GPU-Tile von N5 für Meteor Lake in N4 oder N3 überführt werden, falls dies erforderlich wird.

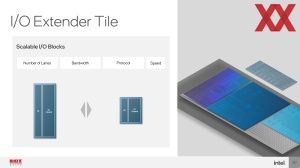

Im SoC-Tile befinden sich Funktionseinheiten wie die Media- und Display-Engine. Aber auch einige der I/O-Funktionen und die Speichercontroller sind hier zu finden. Natürlich kann Intel auch in diesem IP-Blöcken kleinere Veränderungen vornehmen. Letztendlich gilt dies natürlich auch für den I/O-Tile, der vor allem für das Angebot ist an PCI-Express-Lanes verantwortlich sein wird.

Unter diesen vier Chiplets befindet sich der Base-Tile, der die D2D-Interfaces (Die-to-Die) herstellt und auch über eine gewisse Kapazität verfügt, welche für die Strom- und Spannungsversorgung wichtig ist.

Temperaturen und Takt sollen kein Problem sein

Laut Intel befinden sich die ersten Meteor-Lake-Chips bereits in den Laboren und werden getestet. Dies bedeutet aber nicht viel, denn zuletzt hatte Intel vor allem damit zu kämpfen, die Chips nach der Pre-Silicon-Phase und initialen Fertigung durch die Post-Silicon-Phase zu bringen. Die Verzögerungen bei Sapphire Rapids sind vor allem damit zu begründen.

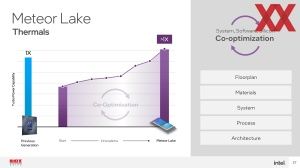

In seinem Vortrag versicherte Intel, dass die Temperaturen für Meteor Lake keine Probleme darstellen werden. Zwar habe man zum Start der Entwicklung des desintegrierten Designs noch nicht die Turbo-Eigenschaften erreichen können, wie dies mit Alder Lake der Fall ist, inzwischen aber sei man durch Optimierungen im Design an einem Punkt angekommen, an dem die thermischen Eigenschaften vergleichbar sind.

Was das Taktverhalten anbetrifft macht man sich den Base-Tile zu Nutze. In allen Fertigungsprozessen nutzt man gewisse kapazitiven Eigenschaften der Materialien, um einen gewissen Puffer aufzubauen, der dann die Transistoren antreibt. Dem Base-Tile kommt hier eine zentrale Rolle zu, denn aufgrund seines Aufbaus kann Intel hier große Kapazitäten vorhalten, die dann in den aktiven Tiles genutzt werden können.

Unter anderem durch den Einsatz des Base-Tile will Intel das Taktverhalten für den Compute-Tile deutlich verbessert haben. Mit der aktuellen Fertigung in Intel 7 vergleichen soll Intel 4 auch durch diese Maßnahme höhere Taktraten erlauben.

Einen kleinen Ausblick gab es auch, was auf Meteor Lake folgen wird bzw. welche Fertigungen hier zum Einsatz kommen werden. Bisher äußert sich Intel hier nur sehr vage. Meteor Lake setzt auf Intel 4 und TSMC N6/N4 sowie 22FFL. Für den Nachfolger setzt Intel auf die eigene Fertigung in Intel 20A, während die weiteren Tiles wieder von (vermutlich) TSMC kommen werden. Für Lunar Lake will sich Intel noch nicht festlegen, das Packaging wird hier allerdings auf eine verbesserte Version mit einem Bump Pitch von 25 µm wechseln.