Werbung

Im Nachgang der Vorstellung der Ryzen-7000-Prozessoren sind noch einige interessante Details bekannt geworden, die zum Markstart sicherlich wichtig sein werden. Dies betrifft vor allem die Zusammenarbeit zwischen Prozessor und DDR5-Speicher.

Die ausschließliche Unterstützung von DDR5 stellt einen großen Wechsel in der Plattform-Technik dar. Offiziell unterstützt werden DDR5-5200, was 400 MT/s mehr sind, als bei Intels Alder-Lake-Prozessoren. 5.200 MT/s werden offiziell aber nur erreicht, wenn Single-Rank- oder Dual-Rank-Module mit einem DIMM pro Speicherkanal eingesetzt werden. Kommen zwei Module pro Speicherkanal zum Einsatz, werden die Module nur noch als DDR5-3600 angesprochen.

| DIMM-Slots pro Speicherkanal | DIMMs pro Kanal | Ranks | Intel Alder Lake | AMD Ryzen 7000 |

| 1 SPC | 1 DPC | 1R | DDR5-4800 | DDR5-5200 |

| 1 SPC | 1 DPC | 2R | DDR5-4800 | DDR5-5200 |

| 2 SPC | 1 DPC | 1R | DDR5-4400 | - |

| 2 SPC | 1 DPC | 2R | DDR5-4400 | - |

| 2 SPC | 2 DPC | 1R | DDR5-4000 | DDR5-3600 |

| 2 SPC | 2 DPC | 2R | DDR5-3600 | DDR5-3600 |

DDR5-5200 werden durch die Ryzen-7000-Prozessoren nur erreicht, wenn ein Speichermodul pro Speicherkanal eingesetzt wird. Intel unterscheidet zwischen dem Ausbau an DIMM-Slots und der letztendlichen Bestückung und macht hier Zwischenschritte zu DDR5-4400 und DDR5-4000. AMD reduziert bei zwei DIMMs pro Speicherkanal gleich auf DDR5-3600. Wie sich der Speicher auf Mainboards verhält, die zwar vier DIMM-Slots besitzen, davon aber letztendlich nur die Hälfte bestückt sind, ist nicht bekannt.

Zum Speicher gehört bei den Ryzen-Prozessoren außerdem die Frage nach dem Takt des Infinity Fabric. Dieser soll nicht mehr ganz so entscheidend sein, wie bei den bisherigen Generationen. Standardmäßig liegt der Takt bei 1.733 MHz. Für DDR5-5200 liegen die Taktraten bei 1.733 (FCLK) : 2.600 (UCLK) : 2600 (MCLK) MHz. Der UCLK (Takt des Speichercontrollers) und MCLK (Speicher-Takt) sollten im Verhältnis 1:1 betrieben werden, um die ideale Leistung zu erreichen.

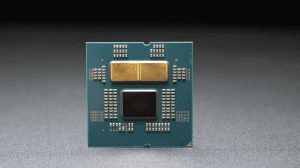

CCD und IOD werden minimal kleiner

Zudem sind nun die Größen des CCDs und IODs bekannt. Die CCDs werden in 5 nm bei TSMC gefertigt, der IOD in 6 nm.

| Fertigung | Die-Größe | Transistoren | Dichte | |

| Zen (Zeppelin) | 14 nm | 212 mm² | 4,8 Milliarden | 22,6 MTr/mm² |

| Zen+ (Zeppelin) | 12 nm | 212 mm² | 4,8 Milliarden | 22,6 MTr/mm² |

| CCD (Ryzen 3000) | 7 nm | 74 mm² | 3,9 Milliarden | 52,7 MTr/mm² |

| IOD (Ryzen 3000) | 12 nm | 125 mm² | 2,09 Milliarden | 16,7 MTr/mm² |

| CCD (Ryzen 5000) | 7 nm | 80,7 mm² | 4,15 Milliarden | 51,4 MTr/mm² |

| IOD (Ryzen 5000) | 12 nm | 125 mm² | 2,09 Milliarden | 16,7 MTr/mm² |

| CCD (Ryzen 7000) | 5 nm | 71 mm² | 6,57 Milliarden | 92,5 MTr/mm² |

| IOD (Ryzen 7000) | 6 nm | 122 mm² | - | - |

Der CCD schrumpft von 80,7 auf 71 mm². Der größere L2-Cache sowie die Änderungen an der Architektur sorgen hier sicherlich dafür, dass der Chip nicht viel an Größe verliert. Die Anzahl der Transistoren aber steigt von 4,15 auf 6,57 Milliarden und somit verdoppelt sich die Transistordichte fast.

Der IOD wird um nur wenige Quadratmillimeter kleiner. Hier dürfte die integrierte Grafikeinheit beispielsweise einen gewissen Einfluss haben. Die Anzahl der Transistoren kennen wir noch nicht.