Werbung

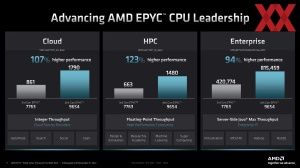

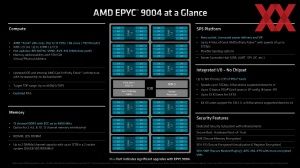

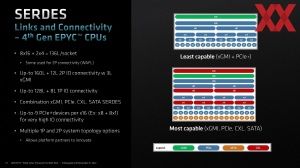

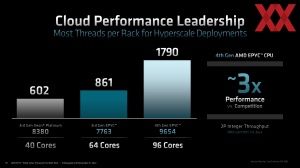

Unter dem Motto "together we advance_data centers" hat AMD die vierte Generation der EPYC-Generationen vorgestellt. Diese zeichnet sich vor allem durch den Einsatz von Zen-4-Kernen, der Unterstützung von DDR5, PCI-Express 5.0, CXL sowie das weitere I/O-Angebot aus. Nichts weniger als die absolute Vorherrschaft in allen Bereichen will AMD mit dieser vierten Generation geschaffen haben – Cloud, HPC, Enterprise und optimierte Versionen für diverse Workloads.

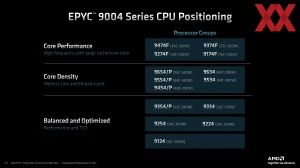

Heute vorgestellt werden aber nur die General-Purpose-Prozessoren auf Basis von Zen 4 – also das Brot-und-Butter-Geschäft für AMD. In Kürze folgen werden die Cloud-Native-Versionen alias Bergamo mit darauf angepassten Zen-4c-Kernen, Siena für Telekommunikation und Edge sowie für technische Spezialbereiche Genoa-X.

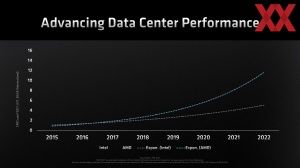

Darüber hinaus bestätigt AMD noch einmal: 2024 soll die fünfte Generation alias Turin folgen. An dieser Stelle verweist AMD auf den Umstand, dass man in den vergangenen Generationen verlässlich immer eine Weiterentwicklung liefern konnte, was Intel nicht in dieser Form gelungen ist. Dies will man auch in Zukunft fortsetzen.

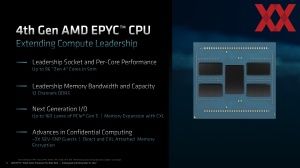

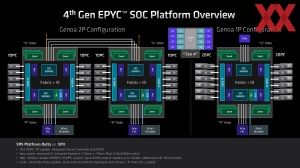

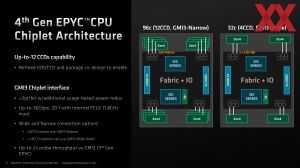

Im Vorfeld hatte AMD bereits mehrfach die wichtigsten Eckdaten der Genoa EPYCs genannt. Zu diesen zählen die 96 Zen-4-Kerne, die sich in zwölf CCDs zu jeweils acht Kernen befinden und an einen zentralen IOD angebunden sind. Dieser IOD stellt die Anbindung von DDR5-Speicher sowie die PCI-Express-5.0-Lanes bereit.

Für das größere Package, aber vor allem um mit DDR5 und PCI-Express 5.0 die I/O-Funktionen in der Form aufrecht erhalten zu können, setzt AMD auf einen neuen Sockel SP5. Dieser hat als LGA6096 satte 6.096 Kontakte. Die EPYC-Prozessoren, bzw. das Package misst 72 x 75 mm und die Kontakte haben einen Abstand von 0,94 x 0,81 mm zueinander. Der SP3 kommt auf Dimensionen von 58,5 x 75,4 mm.

Um den Kontakt in der korrekten Form herzustellen hat AMD den Mechanismus am Sockel leicht verändert. Über eine Feder gehalten wird ein Rahmen heruntergeklappt und mit einer Schraube befestigt. Der eigentliche Druck auf den Sockel, damit der Kontakt zwischen den Pads und den LGA-Pins korrekt hergestellt wird, wird über den Kühler aufgebracht. Dazu wird dieser mit sechs Schrauben und einem definierten Drehmoment mit dem ILM befestigt.

Genoa und die Zen-4-Architektur

Einer der großen Vorteile der Chiplet-Architektur bei AMD ist die Tatsache, dass die CCDs innerhalb der Ryzen (Threadripper) und EPYC-Prozessoren identisch sind. AMD lässt die CCDs in 5 nm bei TSMC fertigen und acht Zen-4-Kerne kommen zusammen mit einem 32 MB L3-Cache zum Einsatz – sowohl bei Ryzen als auch bei EPYC. Der CCD ist 70 mm² groß, wird wie gesagt in 5 nm gefertigt und besitzt 6,5 Milliarden Transistoren.

Grundsätzlich unterscheidet sich die Zen-4-Architektur zwischen den Ryzen- und EPYC-Prozessoren nicht. In der Auslegung der Architektur muss AMD also beide Anwendungsfelder in Betracht ziehen und im Hinterkopf behalten. Bisher war dies immer von Erfolg bekrönt, während Intel in den Performance-Kernen spezifische Anpassungen für die Core- und Xeon-Prozessoren macht.

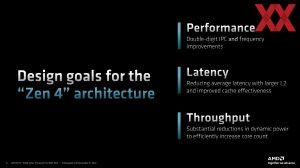

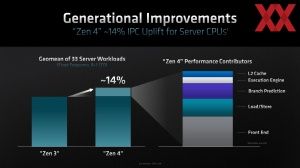

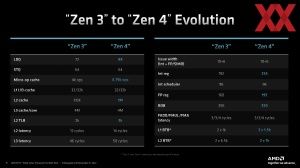

Für die Ryzen-Prozessoren gab AMD ein IPC-Plus von 13 % an, bei EPYC sind es nun 14 %. Dieser kleine Unterschied wird durch die Tatsache begründet sein, dass hier ein Durchschnittswert über mehrere Anwendungen hergenommen wird und sich dieser aufgrund der unterschiedlichen Anwendungen im Serverbereich eben unterscheidet. Die Latenzen sollten durch die größeren Caches und höhere Anzahl an CCDs nicht ansteigen. Zugleich war eben geplant, den L2-Cache zu verdoppeln, während der L3-Cache unangetastet geblieben ist. Neben der reinen Leistung war Steigerung der Effizienz eine weitere Maßgabe.

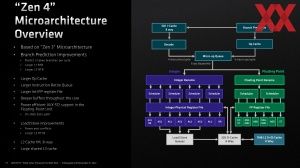

Die Sprungvorhersage ist einer der Punkte, der mit der Zen-4-Architektur überarbeitet und verbessert wurde. Pro Taktzyklus können nun zwei Sprungvorhersagen gemacht werden. Der Op Cache fällt um 68 % größer aus und kann nun neun statt acht Micro-Ops pro Taktzyklus in die Micro-Op Queue liefern. An den Funktionseinheiten für ganzzahlige und Fließkomma-Operationen gibt es keine Änderungen. Die Register Files fallen allerdings größer aus. Die Fließkomma-Einheiten sind unter anderem dazu verantwortlich, die AVX-512-Befehlssätze auszuführen.

Im Backend gibt es Detailverbesserungen in den Load/Store-Einheiten, die eine um 22 % größere Queue vorzuweisen haben. Am D-Cache wurden Optimierungen durchgeführt, sodass es zu weniger Konflikten bei Zugriffen auf die Daten kommt.

Die eben erwähnten Änderungen in Zahlen ausgedrückt, zeigen die obigen Tabellen. Dort zu sehen sind der größere Micro-Op Cache, L2-Cache, L2 TLB, Integer Register, Fließkomma Register sowie L2 und L2 BTB (blau markiert).

Aber es gibt auch Punkte, in denen Zen 4 auf dem Papier schlechter dasteht, als Zen 3. So vergrößert sich die L2-Latenz von zwölf auf 14 Taktzyklen, was bei einem doppelt so großen Cache aber auch nicht weiter verwunderlich ist. Beim L3-Cache sind es nun 50 anstatt 46 Taktzyklen.

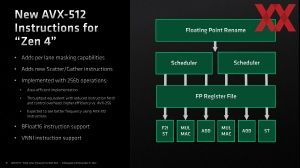

Ein echtes Highlight ist die Integration von AVX-512- in die Zen-4-Architektur und damit die EPYC-Prozessoren. AMD setzt dies in 256-Bit-Operationen um – zweimal ausgeführt ergibt dies 512 Bit. Laut AMD gibt es keinerlei Einfluss auf die Taktfrequenz des Kerns, wenn dieser AVX-512-Befehlssätze ausführt. Dies ist bei den Intel-Prozessoren anders. Die AVX-512-Umsetzung bei AMD ist hinsichtlich der Instruktionen auf Niveau von Cooper-Lake/Ice-Lake bei Intel. Mit Sapphire Rapids wird Intel die AVX-512-Befehlssätze sicherlich um neue Instruktionen erweitern, AMD deckt aber die nach eigenen Angaben wichtigsten ab.

Die Ausführung der AVX-512-Befehlssätze erfolgt in Form zweier 256-Bit-Operationen, die nacheinander ausgeführt werden. Die Zen-4-Architektur besitzt vier 256-Bit-Einheiten, zwei für Fließkomma- und zwei für ganzzahlige Operationen.

Da die EPYC-Prozessoren der dritten Generation die AVX-512-Befehlssätze nicht oder mit einem deutlich geringeren Durchsatz schaffen kann, liegen die neuen Prozessoren natürlich deutlich vor den Vorgängern. Ein Vergleich zu Intel wäre hier sicherlich interessant.

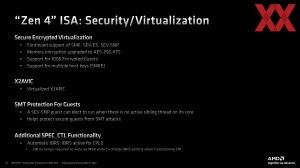

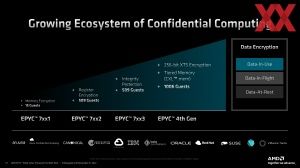

Im Datacenter-Segment ebenfalls besonders wichtig sind Sicherheits- und Visualisierungs-Funktionen. Von diesen unterstützt EPYC viele, die wir schon von der vorherigen Generation kennen. 1.006 Encrypted Guests können pro Sockel auf den Prozessoren ausgeführt werden. Beim Vorgänger waren es 509. Auch multiple Host Keys (SMKE) sind nun möglich.

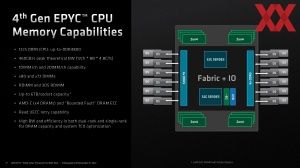

Genoa und DDR5

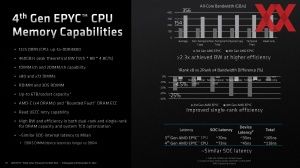

Insgesamt bietet Genoa zwölf Speicherkanäle für DDR5-4800 und über zwei DIMMs pro Speicherkanal können somit 6 TB pro Sockel realisiert werden. Die Speicherbandbreite liegt bei zwölf aktiven Speicherkanälen bei 460 GB/s. Neben den üblichen RDIMM- und 3DS-RDIMM-Modulen mit 80 Datenbits (2x 40 Bit, 2x 32 Data + 8 ECC) unterstützt AMD DDR5-Module, die nur 72 Bits verwenden und daher auf das ECC verzichten.

Die EPYC-Vorgänger Milan bieten acht Speicherkanäle für DDR4-3200 und kommen damit auf 204,8 GB/s. Bei Genoa sollen es nun theoretisch bis zu 460 GB/s sein und in der Praxis zeigt sich laut AMD eine Verdopplung in der Speicherbandbreite. Vielmehr soll der Unterschied zwischen DDR-Speicher als 1Rank x8 gegenüber 2Rank x4 deutlich geringer sein, so dass auf auf den günstigeren 2Rank x4 gesetzt werden kann, ohne dass die Leistung dadurch allzu sehr einbricht.

Für Speicherzugriffe gibt es durch den neuen IOD mit DDR5-Speichercontroller natürlich auch Änderungen in der Latenz.

| SoC-Latenz | Modul-Latenz | Gesamt | |

| 3. Generation EPYC (Milan) | ≈ 70 ns | ≈ 35 ns | ≈ 105 ns |

| 4. Generation EPYC (Genoa) | ≈ 73 ns | ≈ 45 ns | ≈ 118 ns |

Im IOD, bzw. über den Speichercontroller kann AMD fast die identische Latenz erreichen (70 vs. 73 ns). Die DDR5-Module haben durch ihren Aufbau (Takt, Timings, etc.) eine um etwa 10 ns höhere Latenz, so dass dies auch den Gesamtunterschied beschreibt. Mit den stetigen Verbesserungen beim DDR5-Speicher erwartet AMD hier aber zukünftig deutlich geringere Auswirkungen, die für Genoa noch keine Rolle spielen.

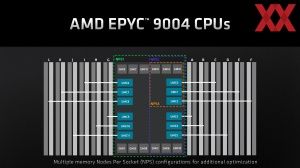

Weiterhin unterstützt werden die NUMA-Konfigurationen NPS1, NPS2 und NPS4. Der Einsatz von NPS2 und NPS4 kann bei bestimmten Anwendungen Sinn machen und beschränkt die Anwendung auf die Ausführung auf nur einem Teilbereich der CCDs sowie der dazugehörigen Speicherkanäle.

Die Mainboard-, bzw. Serverhersteller können abhängig vom Platzbedarf und der Zielgruppe entscheiden, ob sie alle 24 DIMM-Steckplätze zur Verfügung stellen oder nur zwölf, um ein Modul pro Kanal umzusetzen. Das Memory Interleaving ermöglicht zudem eine Beschränkung auf nur zwei, vier, sechs, acht und zehn DIMM-Slots, was natürlich nur dann Sinn macht, wenn der Speicherausbau und die Speicherbandbreite für die jeweilige Anwendung nicht weiter relevant sind. Auf Seiten der Serverhersteller und Cloud-Anbieter hilft dies aber dort, wo es möglich ist, Kosten zu sparen.