Werbung

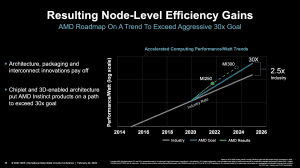

Aktuell findet in San Francisco die International Solid-State Circuits Conference 2023 statt. Auf dieser hielt unter anderem AMD, vertreten durch ihren CEO Dr. Lisa Su, den sogenannten Plenary-Talk zum Start der Konferenz. Die Themen waren die weitere Entwicklung im Compute-Bereich und wie man es schaffen will die Leistung weiter zu steigern, ohne an aktuelle Grenzen hinsichtlich der Fertigung und Anforderungen an die Bandbreite zu zu stoßen.

Der Instinct-MI300A-Beschleuniger, erstmals auf der CES gezeigt, ist AMDs aktueller Fokus und soll noch in diesem Jahr an die ersten Kunden ausgeliefert werden. Natürlich ist man bei AMD bereits einen Schritt weiter, man möchte aber natürlich über das nächste und nicht schon das übernächste Produkt – auch um seinen Konkurrenten nicht allzu viel zu verraten.

Eine Kombination aus Zen-4-Kernen und einer CDNA-3-Compute-Architektur sind die Bausteine des Instinct-MI300A-Beschleunigers. Das Max Plank Institut gab kürzlich bekannt seinen Supercomputer mit diesen Beschleunigern 2024 in Betrieb nehmen zu wollen.

Die Herausforderungen für eine immer höhere Rechenleitung sind zum Einen wie üblich eine Spagat zwischen dem gewünschten Design und einer möglichen Leistungsaufnahme sowie der Umstand, dass die Recheneinheiten mit Daten gefüttert werden müssen. HBM ist für solche Beschleuniger bereits ein Quasi-Standard, aber auch die Caches werden immer größer. Wie wichtig diese sind, zeigt das Aufkommen der Xeon-Max-Prozessoren mit HBM2e, aber auch AMDs Packaging-Highlight 3D V-Cache, bei dem ein zusätzlicher SRAM-Chip direkt auf dem CCD mit den Zen-Kernen aufgebracht wird. Einige EPYC- als auch Ryzen-Prozessoren werden damit ausgestattet.

Cache auf Compute – so könnte man den aktuellen Ansatz von AMD aktuell bezeichnen. Aber es gibt auch Herausforderungen, die sich daraus ergeben. Beispielsweise die Kühlung. Für den Instinct-MI300A-Beschleuniger geht AMD offenbar einen Weg, den wir von Intels Ponte Vecchio kennen: Ein oder mehrere Base Tiles sitzen unter den Compute Tiles und stellen nicht nur die notwendigen Verbindungen bereit, sondern besitzen auch SRAM, der als Cache verwendet werden kann.

Dies gilt in ähnlicher Form wohl auch für den Instinct-MI300A-Beschleuniger, denn in der Präsentation spricht AMD von "Next-gen Infinity Cache and 4th Gen Infinity Fabric base die". Auf diesen Base Dies befinden sich dann wiederum die Chiplets mit den Zen-4-Kernen und die CDNA-3-Chiplets.

Die Tatsache, dass sich die Cache-Chiplets unter den Compute-Dies befinden, dürfte AMD auch die Kühlung vereinfachen, denn letztgenannte Chips sorgen für einen Großteil der Abwärme des gesamten Package.

Die Caches, eine schnelle Anbindung der einzelnen Chiplets für den Infinity Fabric – all das sind Bausteine, die für den Instinct-MI300A-Beschleuniger zum Compute-Bereich hinzukommen und eine wichtige Rolle in der "Unified Memory Architectur" spielen. Über alle Hersteller hinweg sind entsprechende Bestrebungen erkennbar die Speicher und Caches zu vergrößern, sie schneller anzubinden und möglichst allen Recheneinheiten zur Verfügung zu stellen, um multiple Speicherzugriffe und Kopien der Daten zu vermeiden. Auf der ISSCC 2023 gab AMD einen interessanten Einblick in die Umsetzungen der nächsten Generation, zu der wir in den kommenden Monaten sicherlich noch viel hören werden.