News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

SRAM

-

Vertical Compute: imec Spin-Off soll Chiplet-Speichertechnologien entwickeln

Das imec Forschungszentrum hat mit Vertical Compute eine Ausgründung verkündet, welche als Deep-Tech-Halbleiter-Startup die Entwicklung von Chiplet-Technologien vorantreiben soll. Dabei konzentriert man sich auf die Herausforderungen im Bereich der Speicherintegration in Systemen, um die sogenannte Memory Wall zu umgehen, bzw. die Limitierungen im Bereich des schnellen und hochkapazitiven Speichers zu verschieben. In einer ersten... [mehr]

Das imec Forschungszentrum hat mit Vertical Compute eine Ausgründung verkündet, welche als Deep-Tech-Halbleiter-Startup die Entwicklung von Chiplet-Technologien vorantreiben soll. Dabei konzentriert man sich auf die Herausforderungen im Bereich der Speicherintegration in Systemen, um die sogenannte Memory Wall zu umgehen, bzw. die Limitierungen im Bereich des schnellen und hochkapazitiven Speichers zu verschieben. In einer ersten... [mehr] -

2. Generation 3D V-Cache: Neue Details zu AMDs Stapeltechnik

Zusammen mit dem Ryzen 7 9800X3D (Test) führte AMD die zweite Generation der 3D-V-Cache-Technologie ein und in dieser gab es einige entscheidende Änderungen im Aufbau, die letztendlich dazu geführt haben, dass der Ryzen 7 9800X3D höhere Taktraten halten kann und weniger kritisch auf hohe Lasten und Temperaturen reagiert. Mit der zweiten Generation der 3D-V-Cache-Technologie platziert AMD den SRAM-Chip unter dem CCD. Soweit so gut,... [mehr]

Zusammen mit dem Ryzen 7 9800X3D (Test) führte AMD die zweite Generation der 3D-V-Cache-Technologie ein und in dieser gab es einige entscheidende Änderungen im Aufbau, die letztendlich dazu geführt haben, dass der Ryzen 7 9800X3D höhere Taktraten halten kann und weniger kritisch auf hohe Lasten und Temperaturen reagiert. Mit der zweiten Generation der 3D-V-Cache-Technologie platziert AMD den SRAM-Chip unter dem CCD. Soweit so gut,... [mehr] -

Mehr Leistung und niedrigere Temperaturen: Ryzen 9000X3D hat den 3D V-Cache unter dem CCD

Für Anfang November hat AMD den oder die ersten Ryzen-9000-Prozessoren mit zusätzlichem Cache angekündigt. Vermutlich wird es mit dem Ryzen 7 9800X3D nur ein Modell sein, mit dem AMD startet. Aufgrund der Tatsache, dass es sich um den Achtkerner mit einem CCD handelt, umgeht AMD bei diesem Modell die Problematik der Zuteilung der Kerne in Spielen. Wie sich die später erwarteten Modelle mit zwei CCDs, aber nur einmal zusätzlichem Cache verhalten... [mehr]

Für Anfang November hat AMD den oder die ersten Ryzen-9000-Prozessoren mit zusätzlichem Cache angekündigt. Vermutlich wird es mit dem Ryzen 7 9800X3D nur ein Modell sein, mit dem AMD startet. Aufgrund der Tatsache, dass es sich um den Achtkerner mit einem CCD handelt, umgeht AMD bei diesem Modell die Problematik der Zuteilung der Kerne in Spielen. Wie sich die später erwarteten Modelle mit zwei CCDs, aber nur einmal zusätzlichem Cache verhalten... [mehr] -

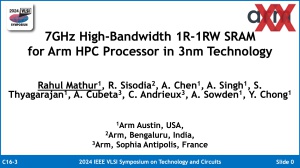

High Bandwidth Instance: ARM will SRAM auf 7 GHz beschleunigen

Um die Daten möglichst nahe und schnell an den Kernen oder Beschleunigern zu haben, sieht nahezu jedes CPU- oder GPU-Design eine Cache-Hierarchie vor. Mit der kleinsten Kapazität ausgestattet, aber am schnellsten ist der L0- oder L1-Cache – je nachdem wie der Hersteller diesen benennt. Er stellt die letzte Speicherebene dar, in der die Daten vorgehalten werden können. Abhängig vom Chip-Design und den Vorgaben im Hinblick auf die Chipgröße... [mehr]

Um die Daten möglichst nahe und schnell an den Kernen oder Beschleunigern zu haben, sieht nahezu jedes CPU- oder GPU-Design eine Cache-Hierarchie vor. Mit der kleinsten Kapazität ausgestattet, aber am schnellsten ist der L0- oder L1-Cache – je nachdem wie der Hersteller diesen benennt. Er stellt die letzte Speicherebene dar, in der die Daten vorgehalten werden können. Abhängig vom Chip-Design und den Vorgaben im Hinblick auf die Chipgröße... [mehr] -

Zen 4 + 3D V-Cache: AMD verrät weitere Details

Kaum ein Thema hat in der vergangenen Woche die Berichterstattung bei den PC-Komponenten derart dominiert, wie die neuen Ryzen-7000X3D-Prozessoren. Bisher hatten wir den Ryzen 9 7950X3D im Test, ein Ryzen 9 7900X3D ist im Zulauf und den Ryzen 7 7800X3D schauen wir uns aktuell in simulierter Form an, denn er wird erst Anfang April erhältlich sein. Aus technologischer Sicht ist das Package der Ryzen-7000X3D-Prozessoren ein echtes Highlight. Mit... [mehr]

Kaum ein Thema hat in der vergangenen Woche die Berichterstattung bei den PC-Komponenten derart dominiert, wie die neuen Ryzen-7000X3D-Prozessoren. Bisher hatten wir den Ryzen 9 7950X3D im Test, ein Ryzen 9 7900X3D ist im Zulauf und den Ryzen 7 7800X3D schauen wir uns aktuell in simulierter Form an, denn er wird erst Anfang April erhältlich sein. Aus technologischer Sicht ist das Package der Ryzen-7000X3D-Prozessoren ein echtes Highlight. Mit... [mehr] -

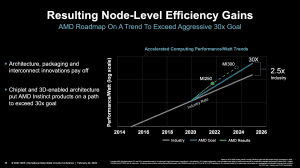

ISSCC 2023: Auf Cache auf Compute folgt bei AMD Compute auf Cache

Aktuell findet in San Francisco die International Solid-State Circuits Conference 2023 statt. Auf dieser hielt unter anderem AMD, vertreten durch ihren CEO Dr. Lisa Su, den sogenannten Plenary-Talk zum Start der Konferenz. Die Themen waren die weitere Entwicklung im Compute-Bereich und wie man es schaffen will die Leistung weiter zu steigern, ohne an aktuelle Grenzen hinsichtlich der Fertigung und Anforderungen an die Bandbreite zu zu... [mehr]

Aktuell findet in San Francisco die International Solid-State Circuits Conference 2023 statt. Auf dieser hielt unter anderem AMD, vertreten durch ihren CEO Dr. Lisa Su, den sogenannten Plenary-Talk zum Start der Konferenz. Die Themen waren die weitere Entwicklung im Compute-Bereich und wie man es schaffen will die Leistung weiter zu steigern, ohne an aktuelle Grenzen hinsichtlich der Fertigung und Anforderungen an die Bandbreite zu zu... [mehr] -

MCD mit 3D V-Cache: AMD scheint Grafik-Chiplets mit zusätzlichem Cache vorzubereiten

Einen Prozessor und eine GPU in ihren Aufgaben und Ressourcen in mehrere Chips aufzuteilen hat AMD aus technologischer Sicht sicherlich einen Vorteil verschafft. Mit dem aufgestapelten SRAM (3D V-Cache) des Ryzen 5 5800X3D und den Milan-X-Prozessoren wurde dann der nächste Schritt in dieser Chiplet-Strategie gemacht. Die nächste Ryzen- und EPYC-Generation mit dem zusätzlichen Cache steht ebenfalls schon in den Startlöchern. Dass sich... [mehr]

Einen Prozessor und eine GPU in ihren Aufgaben und Ressourcen in mehrere Chips aufzuteilen hat AMD aus technologischer Sicht sicherlich einen Vorteil verschafft. Mit dem aufgestapelten SRAM (3D V-Cache) des Ryzen 5 5800X3D und den Milan-X-Prozessoren wurde dann der nächste Schritt in dieser Chiplet-Strategie gemacht. Die nächste Ryzen- und EPYC-Generation mit dem zusätzlichen Cache steht ebenfalls schon in den Startlöchern. Dass sich... [mehr] -

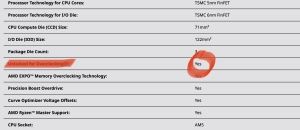

Nun doch oder ein Fehler: Ryzen-7000X3D-Prozessoren mit OC-Unterstützung (Update)

Zur CES stellte AMD die Ryzen-7000X3D-Prozessoren vor. Diese basieren auf der Zen-4-Architektur und bringen 64 MB an zusätzlichem SRAM mit, welcher den L3-Cache in seiner Kapazität deutlich vergrößert. Besonders Spiele sollen davon profitieren und somit diese Modelle die neuen Gaming-Spitzenreiter werden. Kurz nach dem Start veröffentlichte AMD auf den Produktseiten den vermeintlichen Starttermin für die drei Modelle: Den 14. Februar. Doch... [mehr]

Zur CES stellte AMD die Ryzen-7000X3D-Prozessoren vor. Diese basieren auf der Zen-4-Architektur und bringen 64 MB an zusätzlichem SRAM mit, welcher den L3-Cache in seiner Kapazität deutlich vergrößert. Besonders Spiele sollen davon profitieren und somit diese Modelle die neuen Gaming-Spitzenreiter werden. Kurz nach dem Start veröffentlichte AMD auf den Produktseiten den vermeintlichen Starttermin für die drei Modelle: Den 14. Februar. Doch... [mehr] -

Geköpfter Ryzen 7 5800X3D zeigt interessante Details

Das Köpfen eines Prozessors, das heißt das Entfernen des Heatspreaders und der Wechsel des Materials zwischen den eigentlichen Chip und dem Heatspreader ist für Extreme-Overclocker und Enthusiasten eine fast schon alltägliche Prozedur. Mit der inzwischen vom Hersteller vorgenommenen Verlötung bei den High-End-Modellen von Intel und AMD sind die Vorteile dieser Maßnahme allerdings immer weiter zusammengeschrumpft. Hinzu kommt die Gefahr der... [mehr]

Das Köpfen eines Prozessors, das heißt das Entfernen des Heatspreaders und der Wechsel des Materials zwischen den eigentlichen Chip und dem Heatspreader ist für Extreme-Overclocker und Enthusiasten eine fast schon alltägliche Prozedur. Mit der inzwischen vom Hersteller vorgenommenen Verlötung bei den High-End-Modellen von Intel und AMD sind die Vorteile dieser Maßnahme allerdings immer weiter zusammengeschrumpft. Hinzu kommt die Gefahr der... [mehr] -

Ryzen mit 3D V-Cache im Frühjahr, Zen 4 in 5nm + Sockel AM5 im zweiten Halbjahr

Die Vorstellung der mobilen Prozessoren der Ryzen-6000-Serie mit Zen-3+-Kernen und der integrierten RDNA-2-Grafikeinheit ist sicherlich eines der Highlights von AMD. Doch Desktop-Spieler warten auch sehnsüchtig auf Neuigkeiten für ihre favorisierte Plattform und hier stehen zunächst die Ryzen-Prozessoren mit 3D V-Cache an. Diese stellt AMD bereits im vergangenen Jahr für das Frühjahr 2022 in Aussicht und dies bestätigte AMD nun abermals. Aber... [mehr]

Die Vorstellung der mobilen Prozessoren der Ryzen-6000-Serie mit Zen-3+-Kernen und der integrierten RDNA-2-Grafikeinheit ist sicherlich eines der Highlights von AMD. Doch Desktop-Spieler warten auch sehnsüchtig auf Neuigkeiten für ihre favorisierte Plattform und hier stehen zunächst die Ryzen-Prozessoren mit 3D V-Cache an. Diese stellt AMD bereits im vergangenen Jahr für das Frühjahr 2022 in Aussicht und dies bestätigte AMD nun abermals. Aber... [mehr] -

Milan-X: AMD stellt EPYC-Prozessoren mit 3D V-Cache vor

Nach vielen Gerüchten und unbestätigten Meldungen dazu hat AMD nun endlich die EPYC-Prozessoren mit 3D V-Cache vorgestellt. Analog zu den Ryzen-Prozessoren wird über dem Bereich des L3-Caches das CCD angeschliffen und eine Lage zusätzlicher SRAM oben aufgelegt, um die Kapazität des L3-Caches zu verdreifachen. Insgesamt stehen dann 768 MB an L3-Cache zur Verfügung. Die EPYC-Prozessoren mit 3D V-Cache basieren also weiterhin auf der... [mehr]

Nach vielen Gerüchten und unbestätigten Meldungen dazu hat AMD nun endlich die EPYC-Prozessoren mit 3D V-Cache vorgestellt. Analog zu den Ryzen-Prozessoren wird über dem Bereich des L3-Caches das CCD angeschliffen und eine Lage zusätzlicher SRAM oben aufgelegt, um die Kapazität des L3-Caches zu verdreifachen. Insgesamt stehen dann 768 MB an L3-Cache zur Verfügung. Die EPYC-Prozessoren mit 3D V-Cache basieren also weiterhin auf der... [mehr] -

Milan-X: Die ersten EPYC-Prozessoren kommen mit 512 MB 3D V-Cache

Der Start der ersten EPYC-Prozessoren mit 3D V-Cache rückt offenbar immer näher, denn nach dem Auftauchen der ersten Produktnamen gibt es nun weitere Details zu den ersten Modellen – vor allem zur Größe des zusätzlichen Caches. Demnach plant AMD vier Modelle, die mit 16, 24, 32 und 64 Kernen ausgestattet sind und damit hinsichtlich der Anzahl der Kerne die aktuelle Produktpalette abdecken. Der L3-Cache wächst für diese Modelle allerdings... [mehr]

Der Start der ersten EPYC-Prozessoren mit 3D V-Cache rückt offenbar immer näher, denn nach dem Auftauchen der ersten Produktnamen gibt es nun weitere Details zu den ersten Modellen – vor allem zur Größe des zusätzlichen Caches. Demnach plant AMD vier Modelle, die mit 16, 24, 32 und 64 Kernen ausgestattet sind und damit hinsichtlich der Anzahl der Kerne die aktuelle Produktpalette abdecken. Der L3-Cache wächst für diese Modelle allerdings... [mehr] -

Erste Produktnamen der EPYC-CPUs mit 3D V-Cache tauchen auf

Der 3D V-Cache ist die nächste Innovationsstufe, die AMD zündet. Auf den L3-Cache der Chiplets kommen ein bis vier oder gar acht Lagen weiterer SRAMs und schon kann der Cache des Prozessors auf das Vielfache ausgebaut werden. Erstmals sprach AMD zur Computex Anfang Juni über entsprechende Pläne, nannte und zeigte in diesem Zusammenhang aber nur Ryzen-Prozessoren der 5000-Serie. Da gerade Spiele von einem Cache mit höherer Kapazität (bis zu... [mehr]

Der 3D V-Cache ist die nächste Innovationsstufe, die AMD zündet. Auf den L3-Cache der Chiplets kommen ein bis vier oder gar acht Lagen weiterer SRAMs und schon kann der Cache des Prozessors auf das Vielfache ausgebaut werden. Erstmals sprach AMD zur Computex Anfang Juni über entsprechende Pläne, nannte und zeigte in diesem Zusammenhang aber nur Ryzen-Prozessoren der 5000-Serie. Da gerade Spiele von einem Cache mit höherer Kapazität (bis zu... [mehr] -

Milan-X: AMD arbeitet an EPYC-Prozessoren mit 3D-SRAM

Die Gerüchteküche brodelt derzeit kräftig und kocht dabei über einem Mitte März 2020 von AMD zumindest in einer Vorschau präsentierten Technologie. Dabei handelt es sich um das X3D Packaging, also das stapeln von Chips übereinander. Derzeit führt AMD sein Chiplet-Design so aus, dass ein IOD mit bis zu acht CCDs kombiniert wird. Auf einem Package sind die neun Chips nebeneinander angeordnet. Mit dem X3D Packaging sollen die Chips auch... [mehr]

Die Gerüchteküche brodelt derzeit kräftig und kocht dabei über einem Mitte März 2020 von AMD zumindest in einer Vorschau präsentierten Technologie. Dabei handelt es sich um das X3D Packaging, also das stapeln von Chips übereinander. Derzeit führt AMD sein Chiplet-Design so aus, dass ein IOD mit bis zu acht CCDs kombiniert wird. Auf einem Package sind die neun Chips nebeneinander angeordnet. Mit dem X3D Packaging sollen die Chips auch... [mehr] -

AMD will DRAM und SRAM in das CPU-Package bringen

Auf der High Performance Computing Conference gab Forrest Norrod, Senior Vice President und General Manager der Datacenter-Gruppe bei AMD, eine interessante Präsentation. Dabei ging er zunächst einmal auf die aktuellen Herausforderungen im Chipdesign ein. Diese liegen laut AMD in der Fertigung immer kleinerer Strukturen bei gleichzeitig immer größeren Anzahl an Transistoren und damit einer erhöhten Komplexität sowie der Tatsache, dass die... [mehr]

Auf der High Performance Computing Conference gab Forrest Norrod, Senior Vice President und General Manager der Datacenter-Gruppe bei AMD, eine interessante Präsentation. Dabei ging er zunächst einmal auf die aktuellen Herausforderungen im Chipdesign ein. Diese liegen laut AMD in der Fertigung immer kleinerer Strukturen bei gleichzeitig immer größeren Anzahl an Transistoren und damit einer erhöhten Komplexität sowie der Tatsache, dass die... [mehr] -

Quest: Schichten im SRAM Neural Prozessor sprechen per Induktionsschleifen

Für die Steigerung der Rechenleistung moderner Prozessoren sind möglichst viele Datenverbindungen essentiell – gleiches gilt für die Anbindung von schnellem Speicher. Im Falle von High Bandwidth Memory verwenden die meisten Hersteller sogenannte Through-Silicon Vias (TSVs). Bei den TSVs handelt es sich um eine Halbleitertechnik, die durch das Silizium-Substrat geführt wird. Neben der enorm komplizierten Fertigung dieser TSVs bestehen... [mehr]

Für die Steigerung der Rechenleistung moderner Prozessoren sind möglichst viele Datenverbindungen essentiell – gleiches gilt für die Anbindung von schnellem Speicher. Im Falle von High Bandwidth Memory verwenden die meisten Hersteller sogenannte Through-Silicon Vias (TSVs). Bei den TSVs handelt es sich um eine Halbleitertechnik, die durch das Silizium-Substrat geführt wird. Neben der enorm komplizierten Fertigung dieser TSVs bestehen... [mehr]