Werbung

Geleakte Spezifikationen (via Twitter) rahmen die technischen Eckdaten der noch fehlenden Zen-4-Varianten bei den EPYC-Prozessoren ein. Siena ist als EPYC-8004-Serie für Telekommunikationsanwendungen vorgesehen. Genoa-X ist das EPYC-Design mit zusätzlichem 3D V-Cache – ähnlich wie bei den Ryzen-7000X3D-Prozessoren sowie den Vorgängern alias Milan-X.

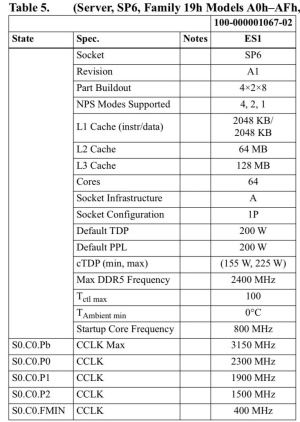

Siena findet seinen Platz im kleineren Sockel SP6 und ist mit einer TDP von 155 bis 225 W vorgesehen. Bei maximal 64 Kernen arbeiten diese vereinzelt mit 3,15 GHz Kerntakt. Der L1- und L2-Cache ist identisch zu allen Prozessoren auf Basis der Zen-4-Architektur. Der L3-Cache ist mit 16 MB allerdings nur halb so groß wie üblicherweise. Ähnliches wird auch für Bergamo, eine auf Cloud-Anwendungen ausgelegte Version, erwartet, die aber auch noch weitere Änderungen enthalten soll. Nicht zuletzt bezeichnet AMD die verwendete Architektur als Zen 4c.

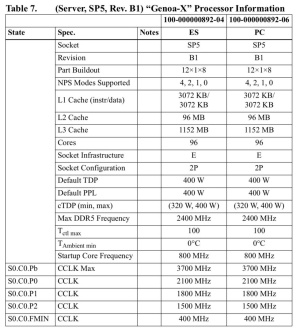

Genau das Gegenteil ist bei Genoa-X der Fall. Hier setzt AMD auf jedes CCD mit acht Kernen noch 64 MB an L3-Cache auf, so dass jedes Chiplet auf 32 + 64 = 96 MB kommt. Wie auch schon bei Milan-X verwendet AMD immer die volle Anzahl bei den CCDs. Im Falle von Genoa sind dies 12 Chiplets für maximal 96 Kerne und damit auch 1.152 MB an L3-Cache. Bei den normalen Genoa-Prozessoren sind des 384 MB. Die TDP reicht auf bis zu 400 W. Es wird auch sicherlich Modelle geben, die auf nur einen Kern pro CCD und dennoch den vollen L3-Cache setzen, was für bestimmte Anwendungen einen deutlichen Vorteil bringen kann.

Sowohl Siena als auch Genoa-X unterstützen zwölf Speicherkanäle für DDR5-4800. Während Siena eine Single-Socket-Umsetzung ist, können zwei Genoa-X-Prozessoren gemeinsam betrieben werden.

Wann die Siena- und Genoa-X-Prozessoren offiziell vorgestellt werden, ist noch nicht bekannt.