Werbung

Um die Daten möglichst nahe und schnell an den Kernen oder Beschleunigern zu haben, sieht nahezu jedes CPU- oder GPU-Design eine Cache-Hierarchie vor. Mit der kleinsten Kapazität ausgestattet, aber am schnellsten ist der L0- oder L1-Cache – je nachdem wie der Hersteller diesen benennt. Er stellt die letzte Speicherebene dar, in der die Daten vorgehalten werden können.

Abhängig vom Chip-Design und den Vorgaben im Hinblick auf die Chipgröße können die Chiphersteller die Größe des L1-Cache grundsätzlich frei wählen. Natürlich gibt es hier gewisse Abhängigkeiten. Beispielsweise ist der L1-Data-Cache der Lion-Cove-Architektur von Intel 48 kB groß. In der Zen-4-Architektur von AMD sind es 32 kB.

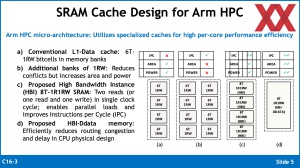

Nun lässt ein hier eingesetzter SRAM in 6T-1RW-Bitzellen aufbauen, so wie dies klassisch meist gemacht wird. Pro Taktzyklus kann aus diesem gelesen oder geschrieben werden. Setzt der Chipdesigner zwei Bänke ein, könnte auf einer Bank gelesen werden, während auf die andere geschrieben wird. Dies würde die Leistung des L1-Data-Caches deutlich erhöhen, hat jedoch den Nachteil, dass die Chipfläche und der Stromverbrauch ansteigen.

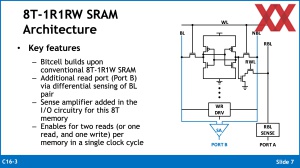

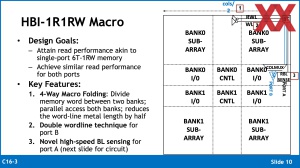

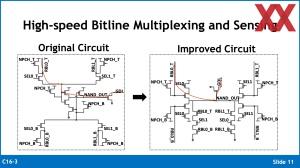

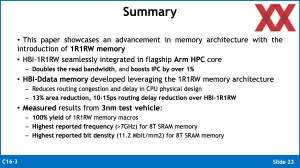

ARM hat auf dem VLSI Symposium 2024 ein Konzept namens High Bandwidth Instance (HBI) vorgestellt. Dieser besteht aus 8T 1R1RW SRAM, sprich die Speicherzellen verfügen über einen zusätzlichen Port, so dass zwei Lese-Vorgänge oder ein gleichzeitiger Lese- und Schreibvorgang stattfinden können.

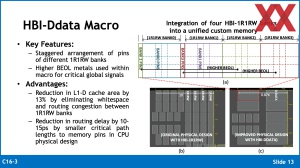

Darüber hinaus sieht ARM einen HBI-DDATA-Speicher vor, der sich von der klassischen Sichtweise und Implementierung eines SRAM für den L1-Data-Cache löst und ein vereinfachtes Design ermöglicht. Zudem sieht ARM einen kleinen Latenzvorteil von 10 bis 15 ps bei einer für L1-Cache typischen Latenz von etwa 0,8 ns.

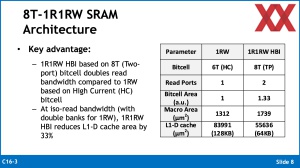

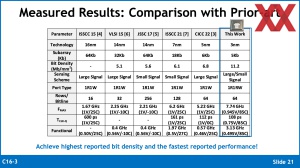

Die Speicherzelle wird bei gleicher Kapazität zwar um 33 % größer (128 kB an 1RW-SRAM benötigen 83.991 µm² und 64 kB an 1R1RW HBI 55.636 µm²), normiert man dies allerdings auf die Bandbreite fällt ein L1-Data-Cache um 33 % kleiner aus. Aber für eine ebenso hohe Kapazität muss mehr Fläche mit eingeplant werden.

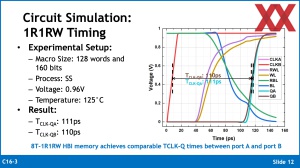

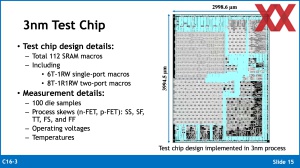

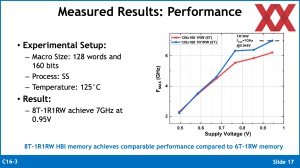

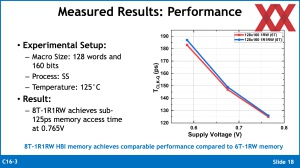

ARM hat für Tests einen Chip in 3 nm mit einer Fläche von 2,9986 x 3,9945 mm (11,98 mm²) fertigen lassen und auf diesem 112 SRAM-HBI-Makrozellen abgebildet, um die elektrischen Eigenschaften überprüfen zu können. Dabei wurde bei einer Spannung von 0,945 V und Takt von 7,74 GHz erreicht. Bei einer Spannung von 0,495 V, was für SRAM eher typisch ist, waren noch immer 3,13 GHz möglich. Die Ausbeute lag bei 100 %. Allerdings ist die Fertigung von SRAM aufgrund der recht einfachen Struktur und der Möglichkeit, hier Redundanzen einzubauen auch nicht sonderlich komplex. Die Skalierung von SRAM in den Chip-Designs ist zu einem größeren Problem geworden und daher spielt die Bandbreite pro Fläche auch eine zunehmend wichtige Rolle.

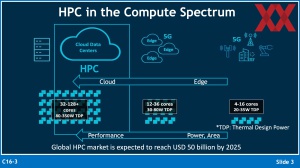

Das, was ARM auf dem VLSI 2024 als High Bandwidth Instance vorstellt, ist ein Konzept und zeigt die vielfältige Weiterentwicklung im Chipdesign. Alle Komponenten sind daran beteiligt und von einem schnelleren SRAM profitieren die Recheneinheiten, egal ob in Prozessoren oder GPUs/Beschleunigern gleichermaßen. SRAM ist ein Grundbaustein und jeden Chipdesigns und daher in seiner Wichtigkeit nicht zu unterschätzen.