Werbung

Mit der Zen-5-Architektur und deren Aufbau sowie den Auswirkungen hinsichtlich der Latenzen sowie Cache- und Speicherbandbreiten haben wir uns bereits beschäftigt. Mehr oder weniger für eine Überraschung sorgte der Umstand, dass AMD mit dem massiven Umbau von Zen 4 auf Zen 5 und der auf 8,315 Milliarden Transistoren deutlich gestiegenen Komplexität des CCDs die Chipgröße mit 70,6 mm² nahezu beibehalten konnte. Ein Grund dafür ist sicherlich, dass der Wechsel von TSMC N5 auf N4X die Transistordichte steigern konnte.

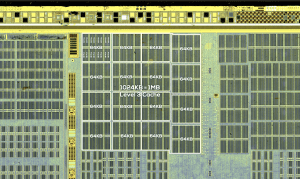

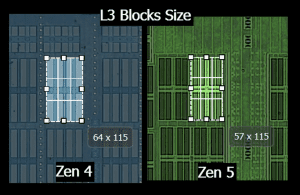

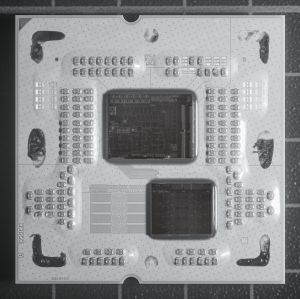

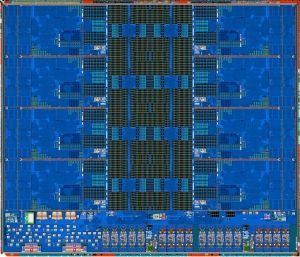

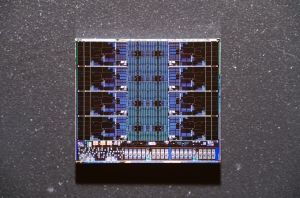

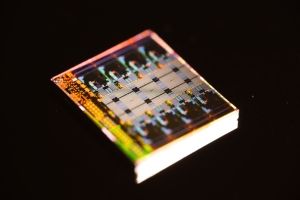

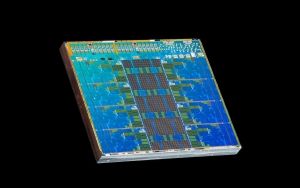

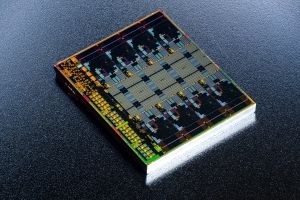

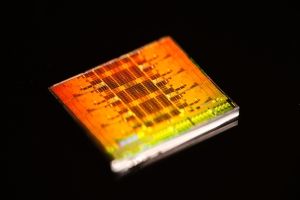

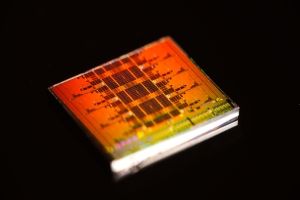

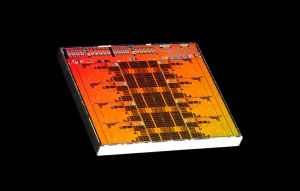

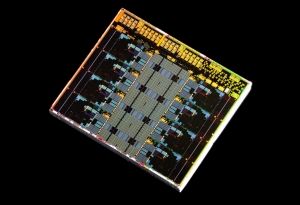

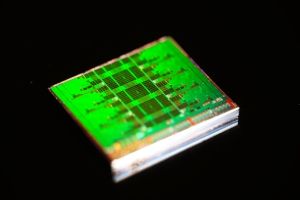

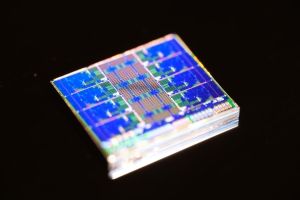

Neue Die-Shots von Fritzchen Fritz offenbaren aber weitere Gründe. Diese gehen auch aus einer Analyse des YouTube-Channels High Yield hervor. So ist der grundsätzliche Aufbau des CCDs mit den Zen-5-Kernen zum Vorgänger identisch. Er enthält weiterhin acht Kerne und einen 32 MB fassenden L3-Cache. Doch beim L3-Cache sind die größeren Veränderungen deutlich erkennbar, denn AMD kann die SRAM-Zellen ausgehend von 24 mm² im Zen-4-CCD auf 15,7 mm² im Zen-5-CCD verkleinern. Von gut einem Drittel der Chipgröße reduziert sich der Anteil des L3-Cache auf weniger als ein Viertel.

| Fertigung | Die-Größe | Transistoren | Dichte | |

| Zen (Zeppelin) | 14 nm | 212 mm² | 4,8 Milliarden | 22,6 MTr/mm² |

| Zen+ (Zeppelin) | 12 nm | 212 mm² | 4,8 Milliarden | 22,6 MTr/mm² |

| CCD (Aspen Highlands, Ryzen 3000) | 7 nm | 74 mm² | 3,9 Milliarden | 52,7 MTr/mm² |

| IOD (Ryzen 3000) | 12 nm | 125 mm² | 2,09 Milliarden | 16,7 MTr/mm² |

| CCD (Breckenridge, Ryzen 5000) | 7 nm | 80,7 mm² | 4,15 Milliarden | 51,4 MTr/mm² |

| IOD (Ryzen 5000) | 12 nm | 125 mm² | 2,09 Milliarden | 16,7 MTr/mm² |

| CCD (Durango, Ryzen 7000) | 5 nm | 71 mm² | 6,5 Milliarden | 92,9 MTr/mm² |

| IOD (Ryzen 7000) | 6 nm | 122 mm² | 3,4 Milliarden | 27,9 MTr/mm² |

| CCD (Eldora, Ryzen 9000) | 4 nm (N4X) | 70,6 mm² | 8,315 Milliarden | 117,78 MTr/mm² |

| IOD (Ryzen 9000) | 6 nm | 122 mm² | 3,4 Milliarden | 27,9 MTr/mm² |

Wie AMD dies zusammen mit TSMC gelungen ist, zeigt sich in der Reduzierung des Platzes zwischen den einzelnen 4kB-SRAM-Zellen. In modernen Fertigungsverfahren skalieren SRAM- und Analogzellen nicht so sehr, wie dies für die Logikbereiche der Fall ist. AMD packt die Zellen also deutlich dichter und erreicht somit eine Reduzierung des Platzbedarfs.

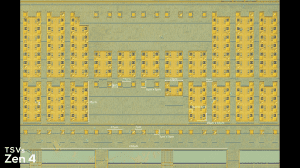

Den Platz zwischen den L3-Cache SRAM-Zellen nutzte AMD in der Zen-3-Generation für die TSVs für Signalleitungen sowie Power/Control des darüber platzierten 3D-V-Cache-Chiplets. Durch die Verkleinerung des CCD mit den Zen-4-Kernen musste AMD die TSVs anders platzieren. Die TSVs für das Signaling befinden sich weiterhin Bereich des L3-Caches. Die für Power/Control sind in den Bereich des L2-Cache gewandert.

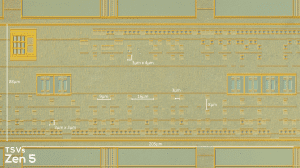

Im Zen-5-CCD sind die Reihen für die TSVs noch einmal deutlich geschrumpft. Die Trennung in der Mitte gibt es quasi gar nicht mehr und es bleiben nur zwei deutlich schmalere Reihen rechts und links im Bereich des L3-Cache übrig. In diesen Bereichen sind die typischen Elemente der TSVs aber nicht mehr erkennbar.

Aber damit stellt sich die Frage, wo AMD die TSVs für Zen 5 mit 3D V-Cache im CCD vorsieht. Die Auflösung: Die Signaling-TSVs befinden sich offenbar noch immer in den zwei Reihen des L3-Cache, sie sind allerdings deutlich kleiner und es sind offenbar auch deutlich weniger als bisher. Waren es im CCD mit Zen-3 und Zen-4-Kernen noch etwa 24.000 TSVs, sind es nun laut High Yield nur noch etwa 9.000.

Auch hier konnte AMD offenbar zusammen mit TSMC in der Ausführung der Fertigung weitere Optimierungen durchführen. Waren die Signaling-TSVs aufgrund eines zusätzlichen Schaltkreises etwa 10 x 10 µm und die Power/Control-TSCs ohne diesen etwa 5 x 5 µm groß, sind es nun 3 x 3 bzw. 3 x 4 µm und auf den zusätzlichen Schaltkreis scheint AMD gänzlich verzichten zu können. Im L2-Cache-Bereich sind keinerlei Power/Control-TSVs zu erkennen.

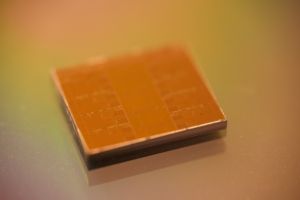

AMD wird für den CCD mit zusätzlichem SRAM-Chiplet aber noch weitere Änderungen vorgenommen haben müssen. Bisher deckte das SRAM-Chiplet mit seiner Größe von 36 mm² genau den Bereich des L3- und L2-Caches des CCDs ab. Als Erweiterung des L3-Caches ist dies auch recht passend, da diese mit hoher Bandbreite (AMD gibt hier 2,5 TB/s an) und niedrigen Latenzen möglich ist.

Mit der kleineren Fläche des L3-Caches im Zen-5-CCD würde das bisher verwendete SRAM-Chiplet nicht nur den Bereich der Caches abdecken, sondern auch noch einen Teil der eigentlichen Kerne. Da diese aber für einen Großteil der Abwärme verantwortlich sind, wäre eine Abdeckung durch den SRAM-Chiplet sicherlich hinderlich für die Kühlung. Wir sind also gespannt, wie AMD dieses Problem lösen wird. Möglich wäre eine Aufteilung von 64 MB zusätzlichem Cache in einem 2-Hi Chiplet – also zweimal 32 MB übereinandergestapelt. Erste Hinweise dazu entdeckten wir bereits 2021 im BIOS eines EPYC-Servers. Damit würde das SRAM-Chiplet nicht mehr Platz benötigen, als die 32 MB an L3-Cache im CCDs selbst. Allerdings hat ein solcher SRAM-Stapel andere technische Herausfordeurngen.

Wir werden einfach abwarten müssen, wie AMD dieses Problem löst. In der Zwischenzeit können wir die die Die-Shots von Die-Shots von Fritzchen Fritz genießen. Zur Analyse von High Yield geht es hier entlang:

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Wer sich für die einzelnen Funktionseinheiten des IOD und CCD interessiert, der findet bei GPUsAreMagic ein paar weitere Details:

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Update:

Im Forum von AnandTech hat Hans de Vries sich die Die-Shots noch einmal genauer angeschaut und ist im Bereich des L2-Cache bis in die Integer-Einheiten hinein dann doch noch auf einige TSVs gestoßen, die bisher vermisst wurden. Bis in den L2-Cache hinein sah AMD auch mit der zweiten Generation des 3D V-Cache bereits Power/Control-TSVs vor, diese rücken nun scheinbar noch weiter in die Kerne hinein.

Zu den bisher entdecken etwa 9.000 TSVs kommen nun etwa 8.500 hinzu. AMD scheint für die TSV-Gruppen nun MIM-Kondensatoren (Metal-Insulator-Metal) zu verwenden, wie sie für spannungsführende Metallschichten in Prozessoren ohnehin schon zum Einsatz kommen.

Dennoch gibt es noch viele Fragen zur Umsetzung von 3D V-Cache mit den Zen-5-CCDs.