Werbung

Auf der International Solid-State Circuits Conference (ISSCC) zeigten zahlreiche Unternehmen aus der Halbleiterbranche ihre Weiter- und Neuentwicklungen aus den verschiedenen Bereichen. Dabei kommen auch immer wieder einige interessante Details zu Tage und aus dem Themenfeld der Fertigung sind dies einige Zahlen zu den Leistungsdaten der nächsten Fertigungsprozesse im Sub-2-nm-Bereich. Sowohl für TSMC wie auch Intel werden dies wichtige Schritte sein - und so geht es auch darum den Kunden zu zeigen, welche Vorteile die neuen Fertigungsprozesse zu bieten haben.

Für Intel ist die Fertigung in Intel 18A aus gleich zweierlei Sicht extrem wichtig. So sollen zukünftige Produkt wie Panther Lake oder Clearwater Forest auf Intel 18A basieren und dem einstiegen Chipgiganten wieder in die Erfolgsspur verhelfen. Die Milliarden-Investitionen, die Intel aktuell vor allem in den USA, aber auch in Irland tätigt, zielen aber auch auf eine deutliche Ausweitung des Foundry-Geschäfts ab. Mittelfristig will man Samsung als zweitgrößten Auftragsfertiger ablösen, längerfristig sollen große Kunden wie NVIDIA und Apple aber auch von TSMC weggelockt werden.

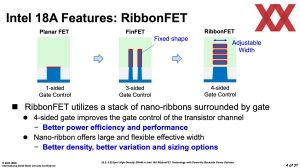

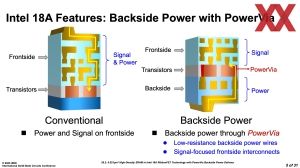

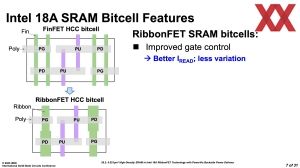

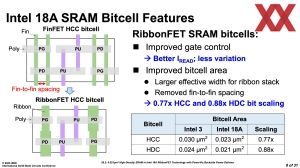

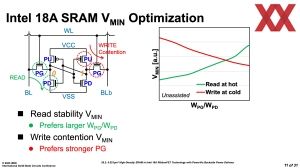

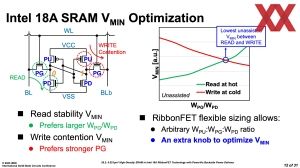

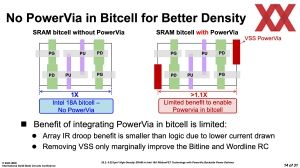

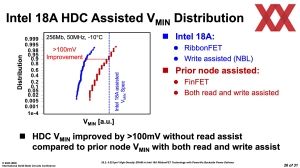

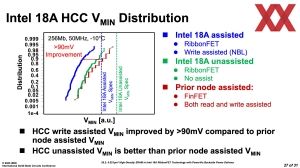

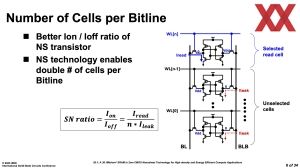

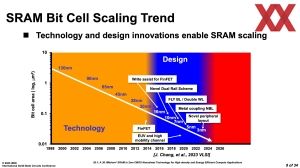

Auf der ISSCC 2025 präsentierte Intel einige Zahlen zur Fertigung von SRAM-Bitzellen in Intel 18A. Für die Logikelelemte der Prozessoren koppelt eine Fertigung in Intel 18A die rückseitige Stromversorgung (Back Side Power Delivery Network oder kurz BSPDN), die bei Intel als PowerVia bezeichnet wird, an die Nutzung der RibbonFET bzw. GAA-Transistoren. Während der Einsatz der GAA-Transistoren für SRAM-Zellen von großem Vorteil ist, sind die Vias für das BSPDN eher hinderlich. Eine höhere Zelldichte erreicht Intel hier demnach nur, wenn in diesem Bereich ausschließlich auf die GAA-Transistoren gesetzt wird.

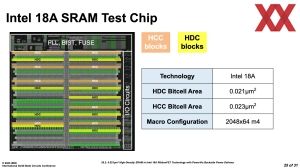

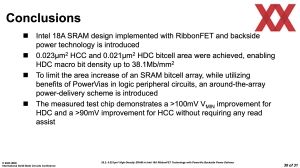

In Zahlen ausgedrückt, kommt eine HCC-Bitzelle (High-Performance) in Intel 3 gefertigt auf 0,03 µm², während es in Intel 18A 0,023 µm² sein sollen. Die dichter gepackten HDC-Bitzellen (High-Density) kommen in Intel 3 auf 0,024 µm² und sollen in Intel 18A auf 0,021 µm² schrumpfen. Was in den Zahlen noch sehr wenig klingt, sind in der Skalierung immerhin Faktor 0,77 bzw. 0,88, was vor allem für die Skalierung von SRAM sehr viel sind.

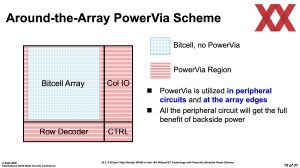

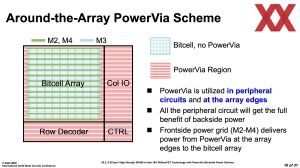

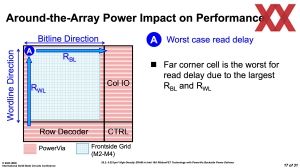

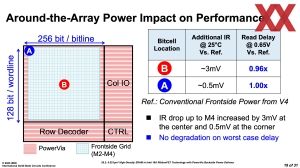

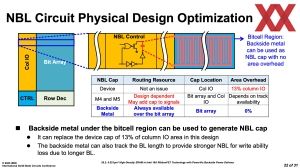

Die PowerVia-Technologie wird vor allem in den Logikbereichen der Prozessoren eine wichtige Rolle spielen, da diese anfälliger für Spannungs-Abfälle (Vdroop) und Interferenzen (RC) sind. Stattdessen wird Intel bei den Bitzellen ein "Around the Array"-Schema mit PowerVia fahren. Bei den Bitzellen wird also auf eine rückseitige Versorgung verzichtet, während die I/O-, Controll- und Decoder-Elemente des SRAMs über PowerVias verfügen.

Nicht nur Intel selbst, sondern auch anhand der präsentierten Leistungswerte scheint Intel 18A tatsächlich der große Wurf zu werden. Eine Macro Bit Density von 38,1 MBit/mm² ist ein ausgezeichneter Wert, der auf Augenhöhe mit dem liegt, was TSMC mit N2 erreichen will. Allerdings gibt es bei den SRAM-Bitzellen immer eine gewisse Abwägung zwischen Leistung (auch minimale Spannung etc.) und Dichte.

Auch TSMC nennt Zahlen zur Skalierung

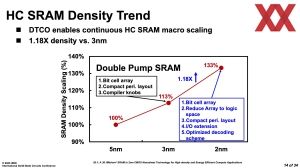

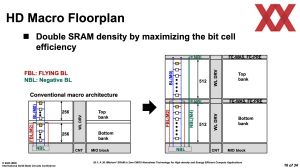

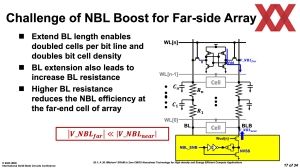

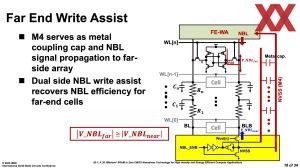

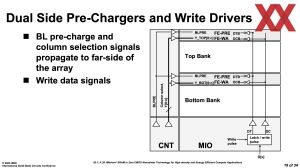

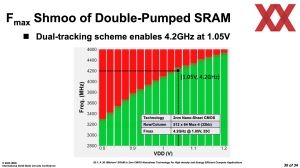

Auch TSMC nannte auf der ISSCC Zahlen zur Skalierung von HD-Makro-Zellen für die Fertigung in N2. Diese sollen einen Wert von 38,1 MBit/mm² oder mehr erreichen. Nicht zufällig ist der Wert identisch zu dem, was Intel zeigte und mit einem Größerzeichen zeigt TSMC einerseits, dass man mehr wird erreichen wollen und andererseits wird das volle Potential gegenüber dem Konkurrenten nicht offenbart. TSMC spricht von einer um den Faktor 1,18 höheren Dichte für die Speicherzellen.

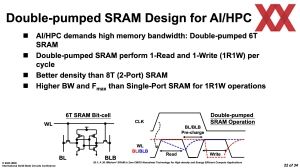

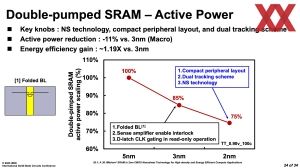

Der Double Pumped SRAM führt pro Taktzyklus einen Lese- und einen Schreibvorgang aus. Neben einer um 18 % höheren Dichte erreicht der SRAM auch einen um 8 % höheren Takt und eine um 19 % höhere Effizienz.