Werbung

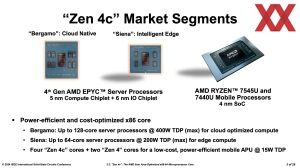

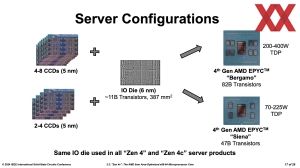

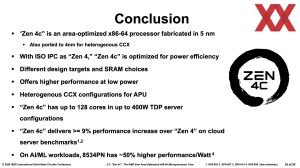

Mit den für Cloud-Anwendungen optimierten EPYC-Prozessoren mit Codenamen Bergamo sowie einigen Ryzen-Prozessoren für das Notebook-Segment präsentierte AMD im vergangenen Jahr die Zen-4c-Kerne. In Teilen sind wir damals bereits darauf eingegangen, wie es AMD schafft, doppelt so viele Kerne auf dem CCD unterzubringen. Mit bis zu 128 Kernen spielt dies für die EPYC-Prozessoren eine wichtige Rolle, aber natürlich darf auch die Leistung keinen Schritt rückwärts machen. Eine höhere Effizienz pro Kern waren neben der größeren Kerndichte der Fokus in der Entwicklung der Zen-4c-Kerne. In den Notebooks spielt diese ebenfalls eine wichtige Rolle. Schlussendlich nutzen auch die auf Infrastruktur ausgelegten EPYC-Prozessoren alias Sienna die Zen-4c-Kerne.

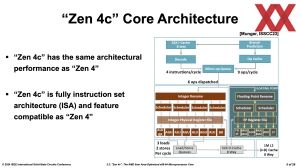

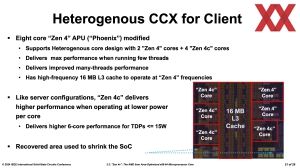

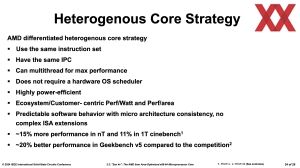

Die Funktionskompatibilität zwischen Zen 4 und Zen 4c ist einer der entscheidenden Vorteile, denn es gibt keinerlei Unterscheidung hinsichtlich der Befehlssatzarchitektur (ISA). Programme müssen daher nicht zwischen zwei Kerntypen unterscheiden können und zudem bietet Zen 4c eine Unterstützung für SMT. Dies ist ein entscheidender Unterschied zum Hybrid-Design mit Performance- und Efficiency-Kernen, wie es bei Intel zum Einsatz kommt.

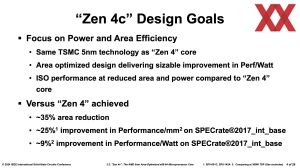

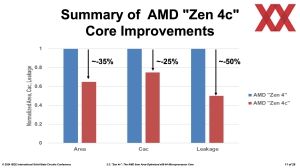

Gegenüber eines Zen-4-Kerns sparen die Zen-4c-Kerne etwa 35 % an Fläche, bieten eine 25 % höhere Leistung pro Fläche und eine 9 % höhere Leistung pro Watt.

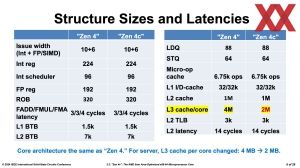

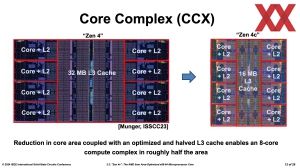

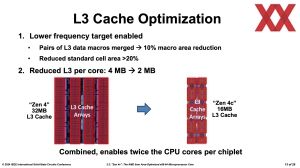

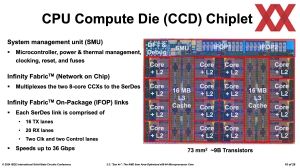

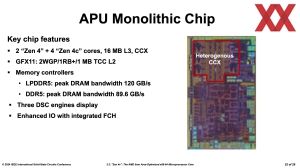

Register, Caches, Scheduler, Integer- und Fließkomma-Recheneinheiten – alles ist zwischen Zen 4 und Zen 4c identisch. Um etwas Platz zu sparen, reduziert AMD den L3-Cache für einen Core Complexes (CCX) auf den CCDs. Dieser ist nun nur noch 16 MB groß. Statt einem CCX mit acht Kernen wie bei Zen 4 sind es hier nun zwei CCX mit jeweils acht Kernen, aber eben auf Basis von Zen 4c. Die L1- und L2-Caches bleiben mit 32 kB (Instruktionen und Data) und 1 MB unangetastet. Auf einem CCD ist der L3-Cache weiterhin 32 MB groß, aber pro Kern steht eben nur die Hälfte zur Verfügung.

Bei den monolithischen Chips für Ryzen Mobile teilen sich 2x Zen 4 plus 4x Zen 4c insgesamt 16 MB an L3-Cache. Bei den Ryzen-Mobile-Prozessoren verwendete AMD bereits häufiger nur den halben L3-Cache.

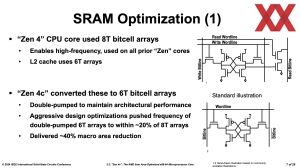

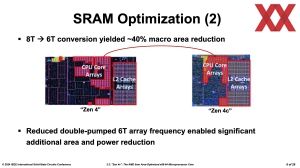

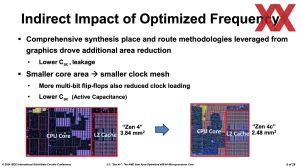

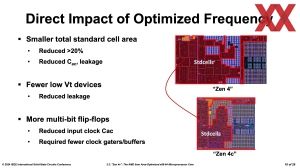

Die Halbierung des L3-Caches spielt in der Verringerung der Größe eine wichtige Rolle. Eine weitere Maßnahme ist der Wechsel von 8T-SRAM-Zellen zu 6T-SRAM-Zellen. Dies gilt für alle SRAM-Zellen des L1 und darunter. Der L2-Cache verwendet auch bei Zen 4 schon 6T-Zellen. Über die verschiedenen Caches und Register hinweg kann AMD hier etwa 40 % an Platz für diesen SRAM einsparen.

Der L2-Cache bleibt mit 1 MB an Kapazität unverändert. Aber auch hier gibt es Optimierungen, die dazu führen, dass die Fläche, die dieser belegt, von 3,84 auf 2,28 mm2 reduziert werden konnte. Für den L3-Cache ist die Halbierung der Kapazität der größte Faktor. Durch eine Neuanordnung der Makro- und Standard-Zellen reduziert AMD die Fläche für den L3-Cache um weitere 10, bzw. 20 %.

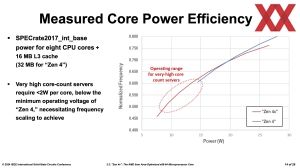

Höhere Leistung bei geringerer Leistungsaufnahme

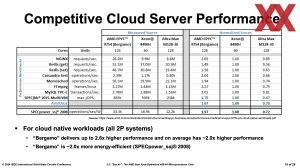

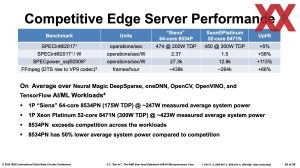

Mehr Kerne pro CCD führen zu mehr Kernen im Package – somit erreicht AMD für die Serverprozessoren eine höhere Kern- und Leistungsdichte. AMD vergleicht hier gegen die eigenen Produkte mit Zen-4-Kernen, vor allem aber gegen die Xeon-Prozessoren von Intel. Ein Sienna-Prozessor mit 64 Kernen soll um etwa 5 % schneller als ein Xeon Platinum 8471N mit 52 Kernen sein, dabei aber mit 200 W TDP sparsamer als die 300 W der Konkurrenz sein. Im SPEC-Power-Rating liegt AMD zwischen 60 und 110 % vor der Konkurrenz.

Für die Ryzen-Mobile-Prozessoren sind die Vorgaben ähnlich, aber doch anders. Für eine TDP von 15 W bieten die Ryzen-Prozessoren mit Zen-4c-Kernen eine höhere Leistung als deren Zen-4-Pendant. Darüber hinaus wendet sich das Blatt zugunsten der reinen Zen-4-Chips.

Für eine nächste Generation mit Zen 5c sieht AMD das Potential die Anzahl der sparsamen Kernen weiter zu erhöhen. Über das Verhältnis aus dann Zen 5 und Zen 5c will AMD die Leistung und Effizienz weiterhin auf die verschiedenen Anwendungsbereiche hin optimieren. Das Konzept wird in dieser Form fortgesetzt werden.

Aber es wird wohl auch dabei bleiben, dass ein heterogenes Design den Mobilprozessoren vorbehalten bleibt. Die Desktop-Modelle werden weiterhin reine Zen-5-Kerne verwenden. Bei den EPYC-Prozessoren wird AMD weiterhin auf reine Zen-5 und Zen-5c-Modelle setzen. Aber den sparsamen Kernen wird eine zunehmend wichtigere Rolle zukommen – so viel deutet sich bereits an.