P

pillenkoenig

Guest

Aaah, ein klassischer holt.

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Das gibts schon, nur nicht von Intel. Bei Linux ist dann eig. schon immer mit FOSS-Tools möglich gewesen.Also wäre dein Fazit unterm strich wäre es besser gewesen nicht so Beta zeug auf den Kunden los zu lassen sondern das mit z. B MS besser abzusprechen, das der USER die Option bekommt für eine Anwendung manuell zu definieren welche Kerne genutzt werden sollen?

Das geht.Könnte die Funktion die E-Cores dynamisch abschalten?

Linux ist halt leider nicht die breite Masse, bei Servern durchaus aber AL in Form von Core i ist halt für Home User ;-)Das gibts schon, nur nicht von Intel. Bei Linux ist dann eig. schon immer mit FOSS-Tools möglich gewesen.

Das geht.

Zur Vergleichbarkeit Beinchen wir wieder auf dem ASUS Z690 Hero mit DDR5.Auf was für ein Board gesockelt?

Ach komm schon, muss man immer für jeden googeln ?Linux ist halt leider nicht die breite Masse, bei Servern durchaus aber AL in Form von Core i ist halt für Home User ;-)

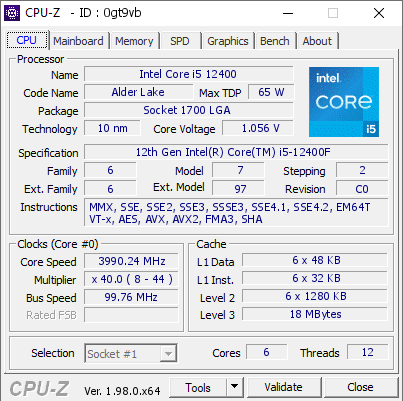

Und warum wird das auf deinen CPU-Z Screen nicht angezeigt?

Außerdem entfällt auch AVX512 von Haus aus, egal welcher Microcode gerade im BIOS implementiert wurde. Hier hat Intel von Beginn an die Reißleine gezogen.

Quelle Igor

Außerdem entfällt auch AVX512 von Haus aus, egal welcher Microcode gerade im BIOS implementiert wurde. Hier hat Intel von Beginn an die Reißleine gezogen.

Irgend einer muss ja mal anfangen, dieser Marktstart bis sich alles einspielt ist echt immer etwas steinig, vor allem da die Produkt Zyklen immer kleiner werden und die Test Phasen kleiner ausfallen, klar KI hilft da mittlerweile. Aber KI kann Menschliches Versagen nicht berücksichtigen.AMD hat aber mit Zen4 einen Vorteil: Dimm DDR5 schon lang am Markt und preislich kaufbar. PCIe5.0 SSD eventuell auch.

Dafür hatte Intel sich z.T. noch das Weihnachtsgeschäft mit den dicken K-Prozis vereinnahmt. Aber optimales Release Setup stelle ich mir anders vor.

Hä? Hat sich da bei Intel was geändert?Je nachdem wie man das nun interpretiert ist das ja irgendwo Dual Kanal.

Zum besseren Verständnis:

H510/610: Dimm A1/B1 (1 Kanal = 2 Dimms)

H570/670: Dimm A1/B1 + A2/B2 (2 Kanäle = 4 Dimms)

B560/660: Dimm A1/B1 + A2/B2 (2 Kanäle = 4 Dimms)

Naja, bei Multicore wars zunächst wurscht, auf welchem Kern was läuft, weil ja eh alle gleich waren.Also wäre dein Fazit unterm strich wäre es besser gewesen nicht so Beta zeug auf den Kunden los zu lassen sondern das mit z. B MS besser abzusprechen, das der USER die Option bekommt für eine Anwendung manuell zu definieren welche Kerne genutzt werden sollen? Ähnlich wie bei Switchable Graphics? Zumindest bis der Threaddirektor reif genug ist automatisiert zu laufen?

Das widerspricht aber dem wie man aktuelle Boards so bestückt. Man steckt ja eben in A1 und B1 und hat damit ja DualChannel. Wenn die "1" den Kanal bezeichnen würde, wären aber ja beide Module auf einem Kanal?Logisch wäre A1/B1 da "A/B" für den Slot steht und "1" halt für den Speicherkanal. Ist ja bei 4 Slot 2 Kanal auch so spezifiziert für DC Modus.

Nein, auch der H610 hat Dual Channel, aber eben nur ein DIMM pro Channel. Spieluhr sollte man ignorieren, denn er stiftet nur Verwirrung, entweder mit Absicht oder weil er einfach keine Ahnung hat und deshalb alles durcheinander bringt.Weiß nicht, wie die Boards beschriftet sind, aber demnach müsste H610 nicht A1 und B1 haben, sondern mit nur einem Kanal eher A1 und A2.

Umgekehrt ist es richtig, lies mal hier auf S. 21, da steht der Hinweis bei Skylake-X CPUs erst A1/B1/C1/D1 zu bestücken und auf der nächsten Seite steht, dass man bei Kaby Lake-X nur die Slots C1/C2/D1/D2 nutzen kann, der hat ja nur 2 RAM Channels.A-D gibt immer den jeweiligen Dimm slot an, 1-2 den jeweiligen Speicherkanal.

Nein, mit den H610 und seinen Vorgängern geht das nicht, die unterstützen nur ein DIMM pro Channel.Und zu 2 Dimms auf einen Kanal: Ja, sind die immer!

Nein, die RAM Riegel selbst haben nur 64 Bit Datenbreit, die 128 Bit werden da angezeigt, weil es eben der Dual Channell Modus ist.Denn der hat einen Datenbitbreite von 256bit, die Module aber 128bit.