Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

-

Hallo Gast!

Noch bis zum 10.05. kannst Du an unserer Hardwareluxx Hardware-Umfrage 2026 teilnehmen! Als Gewinn verlosen wir unter allen Teilnehmern dieses Mal ein Notebook für bis zu 1.800 EUR - über eine Teilnahme würden wir uns sehr freuen!

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

[Sammelthread] AMD K7 - Sockel A (462)

- Ersteller ItsFun

- Erstellt am

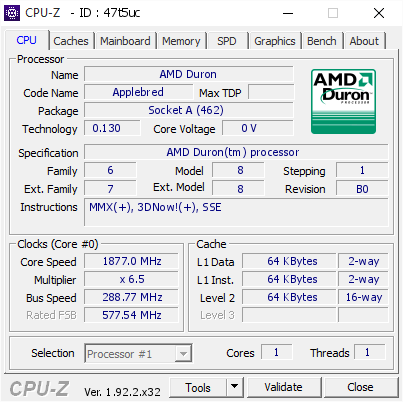

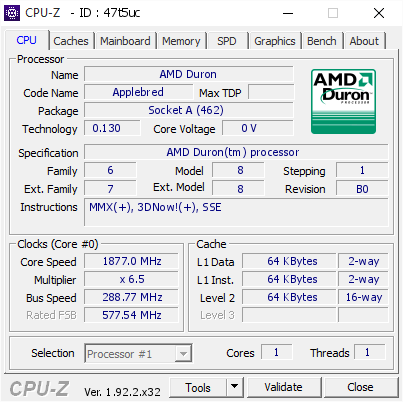

Ich denke wir haben noch etwas Luft beim Asus:

valid.x86.fr

valid.x86.fr

EDIT:

@Strunkenbold

Kann es sein das das Asus A7N8X-E doppelt in der HWBot Datenbank ist? Einmal als A7N8X-E und einmal als A7N8X-E Deluxe? Ein -E non-Deluxe gab es meines wissens nicht?!

AMD Duron @ 1877 MHz - CPU-Z VALIDATOR

[47t5uc] Validated Dump by TerraRaptor (2020-08-28 21:20:19) - MB: Asus A7N8X-E - RAM: 256 MB

EDIT:

@Strunkenbold

Kann es sein das das Asus A7N8X-E doppelt in der HWBot Datenbank ist? Einmal als A7N8X-E und einmal als A7N8X-E Deluxe? Ein -E non-Deluxe gab es meines wissens nicht?!

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

@The Sandman

Beim letzten offiziellen LP B BIOS 2004/11/24 sehe ich tatsächlich mehrere Tebellen für FSB>200MHz. Danke für die Info.

Demnach müssten die Tabellen bei LP B 2004/11/24 BIOS sein:

133MHz

166MHz

200MHz

220MHz

240MHz

263MHz

133MHz

166MHz

@Atlan1980

BIOS platt? Ich hoffe, du hast ein Ersatz-BIOS?

@Tzk Terras brett ist ja auch nicht von dieser Welt

Terras brett ist ja auch nicht von dieser Welt

Beim letzten offiziellen LP B BIOS 2004/11/24 sehe ich tatsächlich mehrere Tebellen für FSB>200MHz. Danke für die Info.

Demnach müssten die Tabellen bei LP B 2004/11/24 BIOS sein:

133MHz

166MHz

200MHz

220MHz

240MHz

263MHz

133MHz

166MHz

@Atlan1980

BIOS platt? Ich hoffe, du hast ein Ersatz-BIOS?

@Tzk

Terras brett ist ja auch nicht von dieser Welt

Terras brett ist ja auch nicht von dieser Weltdigitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Die 200, 220, 240, 263MHz Tabellen scheinen sich nur bei einem Wert zu unterscheiden. Davon schreibt NEOAethyr in seinem Post. Es ist der register 68h (b0d0f3) Wert:

200MHz - DDh

220MHz - AAh

240MHz - 55h

263MHz - 22h

200MHz - DDh

220MHz - AAh

240MHz - 55h

263MHz - 22h

Jop, das kann ich bestätigen. Der Wert ist in den Romsips in der zweiten Zeile an Stelle 10 und 11 zu finden. In der System.bin sieht das dann so aus für diesen Wert:

Romsip 1 + 2: FF

3+4: 00

5+6: DD

7+8: AA

9+10: 55

11+12: 22

13+14: FF

15+16: 00

Daher solltest du mit deiner Sortierung aus Post #3578 Recht haben, es ist 133-166-200-220-240-263-133-166. Damit sind die 263er Sips folgende:

Und:

Hmm, ob die wohl mehr Takt zulassen als Merlins ED aus dem Taipan 0.3?

Romsip 1 + 2: FF

3+4: 00

5+6: DD

7+8: AA

9+10: 55

11+12: 22

13+14: FF

15+16: 00

Daher solltest du mit deiner Sortierung aus Post #3578 Recht haben, es ist 133-166-200-220-240-263-133-166. Damit sind die 263er Sips folgende:

Code:

65D0 162B 0200 0310 0303 0303 1818 1818

0000 6100 227E 7477 5005 6600 0600 0763

0000 0000 1F3F 62F7 0000 0000 86A8 1000

0D0C DD00 0000 0000 0000 0000 FFFF FFFF

FFFF FFFF 0000 0000 0000 0000 0000 0000

0380 804B 0400 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0F40 0000 0000 0008 0000 0000 0000 0000

2141 2400 00ED 1618 2141 2500 00ED 1618

2141 2500 00ED 1618 2141 2600 00ED 1618

2141 2300 00ED 2720 2141 2400 00ED 2720

2141 2500 00ED 2618 2141 2600 00ED 2618

2141 2000 00ED 1618 2141 2100 00ED 1618

2141 2100 00ED 1618 2141 2200 00ED 1618

2141 2200 00ED 1618 2141 2300 00ED 1618

2141 2300 00ED 1618 2141 2400 00ED 1618Und:

Code:

65D0 162B 0200 0310 0303 0303 1818 1818

0000 6100 227E 7477 5005 6600 0600 0763

0000 0000 1F3F 62F7 0000 0000 86A8 1000

0D0C DD00 0000 0000 0000 0000 FFFF FFFF

FFFF FFFF 0000 0000 0000 0000 0000 0000

0380 804B 0400 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0F40 0000 0000 0008 0000 0000 0000 0000

6941 2400 00ED 1510 6941 2500 00ED 1510

6941 2500 00ED 1510 6941 2600 00ED 1510

6941 2300 00ED 2620 6941 2400 00ED 2620

6941 2500 00ED 2618 6941 2600 00ED 2618

6941 2000 00ED 1618 6941 2100 00ED 1618

6941 2100 00ED 1618 6941 2200 00ED 1618

6941 2200 00ED 1510 6941 2300 00ED 1510

6941 2300 00ED 1510 6941 2400 00ED 1510Hmm, ob die wohl mehr Takt zulassen als Merlins ED aus dem Taipan 0.3?

Zuletzt bearbeitet:

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Diese Tabellen werden den Tabellen vom X1 sehr ähneln. Der 68h=22 (vs. 55) wird wohl verschieden sein. Ich denke mit deinen Tabellen wirst du etwas mehr Erfolg haben, als mit ED. Versuch macht klug.

Die ED55 (bzw X1) Tabelle ist bis auf die letzten 2 Blöcke der ersten Zeile (codierter FSB) komplett identisch zu den DFI 240Mhz Romsips...  Was wie gehabt gefixt wurde sind die letzten vier Einträge der Multitabellen (1510 -> 1518). Ansonsten alles gleich.

Was wie gehabt gefixt wurde sind die letzten vier Einträge der Multitabellen (1510 -> 1518). Ansonsten alles gleich.

Also mal ED55 statt die Taipan ED antesten und die 55 in 22 ändern und sehen was FSB und Bandbreite machen.

Was wie gehabt gefixt wurde sind die letzten vier Einträge der Multitabellen (1510 -> 1518). Ansonsten alles gleich.

Was wie gehabt gefixt wurde sind die letzten vier Einträge der Multitabellen (1510 -> 1518). Ansonsten alles gleich.Also mal ED55 statt die Taipan ED antesten und die 55 in 22 ändern und sehen was FSB und Bandbreite machen.

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

@Atlan1980 geht mir genauso. Die blöden Löcher lotfrei zu bekommen ist das schlimmste. Ich habe auch nur eine manuelle Lötpumpe. Für etwas gescheites bin ich irgendwie zu geizig. Viel Erfolg, dass du die Leiterbahnen gefixt oder überbrückt bekommst.

Viel Erfolg, dass du die Leiterbahnen gefixt oder überbrückt bekommst.

@Tzk

der codierte FSB in der ersten Zeile macht manchmal irgendwie keinen Sinn. Ich denke nicht, dass das System 100% stur danach geht. Warum, keine Ahnung.

Ich muss zugeben, dass ich mit 22 noch nie im oberen Bereich getestet habe. Muss ich auch mal machen. Vielleicht schreibe ich die 22 direkt in die sips und passe gleich noch die multitables noch an.

Viel Erfolg, dass du die Leiterbahnen gefixt oder überbrückt bekommst.

Viel Erfolg, dass du die Leiterbahnen gefixt oder überbrückt bekommst.@Tzk

der codierte FSB in der ersten Zeile macht manchmal irgendwie keinen Sinn. Ich denke nicht, dass das System 100% stur danach geht. Warum, keine Ahnung.

Ich muss zugeben, dass ich mit 22 noch nie im oberen Bereich getestet habe. Muss ich auch mal machen. Vielleicht schreibe ich die 22 direkt in die sips und passe gleich noch die multitables noch an.

The Sandman

Urgestein

NEO schreibt auch, dass die DFI Biose automatisch auf andere Timings springen können (so verstehe ich das), was andere Biose nicht machen. Als ich mit dem X1 und dem Abit an den 250-MHz rumprobiert habe, war der Lauf mit den 250-MHz aus dem Bios auch langsamer wie der mit den von 200 auf 250-MHz per clockgen unter Windows gesetzten...

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

The Sandman

Urgestein

E: Naja... machen lassen.

Das LanParty Ultra B hat er aber wohl mal gut durchgemessen bzw. auch im BadCaps Sachen gepostet.

Das LanParty Ultra B hat er aber wohl mal gut durchgemessen bzw. auch im BadCaps Sachen gepostet.

Temp Offset: +3c (-3c to get the real)

CPU-Diode Offset: -30c (+30c to get real)

Used the hd temps to get the offset, I'll need to verify that the hd temps are calibrated correctly...

AGP-VDDQ Src: +3.33v

North Bridge Voltage Src: +3.33v

agp Mod is By Pin 2 (Inverting Input A) on the LM358

;;;;;;

RS232-DB9 COM/Serial Port: Doesn't Use Power

RS232-DB25 LPT/Printer Port: +5.00v

AGP Slot: +12.00v, +5.00v, +3.33v, AGP-VDDQ

PCI Slot: +12.00v, -12.00v, +5.00v, +3.33v

;;;;;;

Supposedly R151 is For The South Bridge Voltage Mod.

R151 is a 0k Resistor

Reads back as:

LM3580

Memory Voltage Controller: Semtech SC2616

VDDQ Mod: 100k Pot

CMOS EEPROM: ATMEL 24C32AN

;;; Notes:

DMM of 0.7% accuracy.

Ground accuracy of 0.02v given the stock psu I'm using, however in practice it was actually 0% (un-meassurable when used with a +).

I always used a ground from the psu, incase the float was a diff level on the board's grounds.

;;; Resistors

R156: 102 North Bridge Voltage Regulator Feedback (Offset)

R192: 10d Memory VDDQ Feedback

R186: 25C Memory VDDQ+VTT (Lower Resitance = More Voltage Output)

R198: 30C Memory VDDQ of some sort

MEM-VDDQ -> R198 -> R186 -> Ground ... Pencil R186 For MEM-VDDQ+MEM-VTT Mod

;;;

+5.00v -> Q26 -> Q23 -> MEM-VDDQ(RAW) & Q21

Q21 -> SC2616 Pin: BG

BG = Bottem Gate Drive

;;; Caps:

C3C2: 100uf 16v

C3E2: 100uf 16v

C5C3 (Missing): ? +3.33v

C5E3 (Missing): ? +5.00v

C5F2 (Missing): ?

C6C1: 470uf 16v +12.00v

C6C2: 10uf 16v

C6D3: 10uf 16v

C8C7: 10uf 16v

C11J2: 10uf 16v

EC3 (Missing): ? ? 2.40v+, same thing as EC65, measured resistance, probably will prevent the board form booting if a cap is placed there, then again there are caps in place by stock that do the same thing...

EC4: 10uf 16v

EC5: 100uf 16v

EC6: 100uf 16v

EC7: 100uf 16v

EC8 (Missing): ? +12.00v

EC9: 10uf 16v

EC10: 470uf 16v +5.00v

EC11: 470uf 16v +5.00v

EC12: 10uf 16v

EC13: 1500uf 16v +12.00v

EC14: 22uf 25v (AB0, Couldn't read on AC0)

EC15: 3300uf 6.3v CPU-VDD

EC16 (Missing): ? +12.00v

EC17: 100uf 16v

EC18 (Missing): ? +12.00v

EC19 (Missing): ? +3.33v

EC20: 3300uf 6.3v CPU-VDD

EC21: 1500uf 16v +12.00v

EC22: 1500uf 16v +12.00v

EC23: 3300uf 6.3v CPU-VDD

EC25 (Missing): ? +3.33v

EC24: 10uf 16v

EC26: 100uf 16v

EC27: 10uf 16v

EC29 (Missing): ? +5.00v

EC2d: 100uf 16v

EC30: 100uf 16v

EC31 (Missing): ? +3.33v

EC32 (Missing): ? +5.00v

EC33: 3300uf 6.3v CPU-VDD

EC34 (Missing): ? +3.33v

EC35 (Missing): ? +5.00v

EC36: 3300uf 6.3v CPU-VDD

EC37: 1000uf 10v +5.00v

EC38 (Missing): ? +12.00v

EC40: 100uf 16v

EC41 (Missing): ? +3.33v

EC42: 10uf 16v Supposedly The South Bridge Voltage, 1.62v

EC43: 1000uf 6.3v AGP VDDQ (Main Cap)

EC44 (Missing): 10uf 16v ??? North Bridge Regulated Output, Hooks into the regulator chip, Used for smoothing out the regulator a bit, dn if it works

EC45: 10uf 16v

EC46: 10uf 16v

EC47: 1000uf 6.3v North Bridge Regulated Output (Main Cap)

EC50: 1000uf 6.3v MEM VDDQ

EC52 (Missing): 10uf 16v ??? North Bridge Regulated Output, to smooth out the fluctuations if any (there is by that point on the board).

EC53: 470uf 16v +5.00v

EC54 (Missing): ? +12.00v, probably for the SC2616.

EC55: 470uf 6.3v +3.33v

EC56: 1000uf 6.3v MEM VDDQ

EC57 (Missing): ? MEM VTT & VTT-Sense (VTT is tied directly to VTT-Sense unfortunatly..., there is no way of adjusting it separately without cutting the trace from under the board and redoing it)

EC59: 220uf 10v MEM VTT

EC60: 1000uf 10v +5.00v (Assumed MEM VDDQ Src)

EC61 (Missing): ?

EC62: 220uf 10v MEM VTT

EC63 (Missing): 4.7uf 16v ??? MEM VDDQ & ATMEL 24C32AN (CMOS / CMOS Reloaded) (From what it looks like, it looks like it's only for the CMOS)

EC64: 1000uf 10v +5.00v (Assumed MEM VDDQ Src)

EC65 (Missing): ? +5.00v, Supposedly (trodas) if you put a cap here the board won't post, Note that if measured resistance against ground it opens then closes immediately, hence to say it will prevent the board from starting up probably

EC66: 220uf 10v MEM VTT

EC67: 1000uf 6.3v MEM VDDQ

EC68: 220uf 10v MEM VTT

EC69: 1000uf 6.3v ??? Read 1.86v

CPU-VDD Source: EC13, EC21, EC22

Stock: 3x 1500uf (4500uf)

Better: 3x ??? (Using 1800uf for now)

Notes:

1800uf seems worse, but the better caps allow me to use lower vcore values and have them actually work... (only if the cpu speed is low enough)

CPU-VDD: EC15, EC20, EC23, EC33, EC36

Stock: 5x 3300uf (16500uf)

AGP-VDDQ: EC43

Stock: 1x 1000uf

NB-Voltage: EC47

Stock: 1x 1000uf

Better: 1x 1800uf

Notes:

Stability increased in memory timings and bus timings.

Stability increased by a decent amount with lower nb voltages.

Overall bandwith and stability increases.

MEM-SRC: EC60, EC64

Stock: 2x 1000uf (2000uf)

DataSheet: 3x 1500uf (4500uf)

MEM-VTT: EC59, EC62, EC66, EC68

Stock: 4x 220uf (880uf)

DataSheet: 1x 1500uf

MEM-VDDQ: EC50, EC56, EC67

Stock: 3x 1000uf (3000uf)

Better: 3x 1800uf (5400uf)

DataSheet: 2x 3300uf (6600uf)

Notes:

Big improvements in load, ie 2x512m is allmost like 1x512m.

Bandwith and stability overall is slightly higher.

CPU-VDD is less dependant on memory load and config types.

;;;

;;; Coils:

LC5: MEM-VDDQ, Offset: -0.1v

;;;

;;; North Bridge Readings:

Q18: (Regulator)

BIOS: Actual

1.6v: 1.62v

1.7v: 1.73v

1.8v: 1.83v

1.9v: 1.94v

EC52: (After Fet)

BIOS: Actual

1.6v: 1.62v

1.7v: 1.73v

1.8v: 1.83v

1.9v: 1.94v

EC44: (After Fet, way after...)

Seemed lower then the last cap...

1.72v I believe.

Read the Regulator by reading off the leg towards the bottom, next to the board's screw hole (MH6).

;;;

;;; AGP Readings:

Q12: AGP Regulator

Src: +3.33v

BIOS: Actual (BIOS VAGP Setting Thingy)

1.5v: 1.54v

1.6v: 1.64v

1.7v: 1.74v

1.8v: 1.84v

Measure by top leg, closest to agp slot.

;;;

;;; MEM Readings:

Q21: VDDQ Regulated Final Output To Memory.

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 2.60v

2.7v: 2.71v

2.8v: 2.80v

2.9v: 2.91v

3.0v: 3.00v

3.1v: 3.09v

3.2v: 3.19v

3.3v: 3.29v

Q23: VDDQ Regulated Output To Q21.

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 2.63v

2.7v: 2.72v

2.8v: 2.82v

2.9v: 2.92v

3.0v: 3.01v

3.1v: 3.10v

3.2v: 3.18v

3.3v: 3.29v

Q26: ??? (Seems like Regulated Rail To Q23, not sure yet)

Measure Q21 By it's base.

Measure Q23 By the leg closest to Q21.

Update!: I apparently have no idea how to really measure those mem fets, neither does anyone else...

Go by the darn caps on the board, there's a huge diff!, I'd otherwise go by the fets if I knew how they were configured and how to read them.

Also note that it's about equal with VTT that way, now it makes sense...

Also that's why mbm reads it way off, like it should apparently, when sensor is *0.016 (I dn if that calculation for the sensor is correct though).

EC63: (Missing cap, VDDQ, It's inbetween slots 1+2 (farthest and 2nd farthest away from chipset, ie labled slot 2+3 on the board)

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 2.68v

2.7v: 2.79v

2.8v: 2.88v

2.9v: 2.99v

3.0v: 3.08v

3.1v: 3.18v

3.2v: 3.28v

3.3v: 3.39v

EC57: MEM VTT / VTT-Sense

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 1.35v

2.7v: 1.4v

2.8v: 1.45v

2.9v: 1.5v

3.0v: 1.54v

3.1v: 1.6v

3.2v: 1.65v

3.3v; 1.7v (note a 3.4v vddq would be for this vtt if it was a stock 1/2 setup, it's making sense now, mobo overvolts by 0.1v and doesn't tell you...)

MEM FeadBack (VDDQ-Sense) Readings: (Via After Resistor just before the pin on the SC2616)

BIOS: Actual

2.6v: 1.27v

2.7v: 1.27v ...

Wth you know...

That's not how the bios is setting voltage, it is using it as a slight offset though.

That would be my guess.

What the heck though.

I dn understand yet...

;;;

R186: Black 25C

Around 9.5k stock resistance, I think (9.49k, left ground)

MEM-VDDQ & MEM-VTT Pencil Mod

You can max the VTT and VDDQ this way..., and I mean max...

8.87k = 2.87v

I want something inbetween these 2 values...

8.75k = 2.92v

8.49k = +0.4v

Supposedly it's an 18.2k resistor

25 = 178

C = 100

= 17800, 17.8k

Code:

;;; Intersil HIP6301CB

Default-Spec: 1.1v-1.85v

Default: 1.1v-2v (1.25v-2v?)

VSEN:

-10% of VCORE

Causes Power Good To Go Low.

+15% of VCORE

Causes CPU power shutdown until VCORE is lower then +15% then set VID.

;;;

vcore mod by fb to ground

ocp mod

Phillips LM3580

CSI 93C46S

0340H

Texas Instruments GD75232

39K

FR95

Winbond

5TS-S

346GB

Intersil HIP6301CB CPU

Intersil HIP6601BCB CPU

Phillips 74HCT74D Wierd

Attansic AT209S PCI Arbiter & Clock Buffer

Attansic ATXP1 Overclock Controller

IDT/ICS ICS1893AF Intergrated nVidia LAN

Texas Instruments LC06A Buffer/Hex Inverter

CPU-Diode Offset: -30c (+30c to get real)

Used the hd temps to get the offset, I'll need to verify that the hd temps are calibrated correctly...

AGP-VDDQ Src: +3.33v

North Bridge Voltage Src: +3.33v

agp Mod is By Pin 2 (Inverting Input A) on the LM358

;;;;;;

RS232-DB9 COM/Serial Port: Doesn't Use Power

RS232-DB25 LPT/Printer Port: +5.00v

AGP Slot: +12.00v, +5.00v, +3.33v, AGP-VDDQ

PCI Slot: +12.00v, -12.00v, +5.00v, +3.33v

;;;;;;

Supposedly R151 is For The South Bridge Voltage Mod.

R151 is a 0k Resistor

Reads back as:

LM3580

Memory Voltage Controller: Semtech SC2616

VDDQ Mod: 100k Pot

CMOS EEPROM: ATMEL 24C32AN

;;; Notes:

DMM of 0.7% accuracy.

Ground accuracy of 0.02v given the stock psu I'm using, however in practice it was actually 0% (un-meassurable when used with a +).

I always used a ground from the psu, incase the float was a diff level on the board's grounds.

;;; Resistors

R156: 102 North Bridge Voltage Regulator Feedback (Offset)

R192: 10d Memory VDDQ Feedback

R186: 25C Memory VDDQ+VTT (Lower Resitance = More Voltage Output)

R198: 30C Memory VDDQ of some sort

MEM-VDDQ -> R198 -> R186 -> Ground ... Pencil R186 For MEM-VDDQ+MEM-VTT Mod

;;;

+5.00v -> Q26 -> Q23 -> MEM-VDDQ(RAW) & Q21

Q21 -> SC2616 Pin: BG

BG = Bottem Gate Drive

;;; Caps:

C3C2: 100uf 16v

C3E2: 100uf 16v

C5C3 (Missing): ? +3.33v

C5E3 (Missing): ? +5.00v

C5F2 (Missing): ?

C6C1: 470uf 16v +12.00v

C6C2: 10uf 16v

C6D3: 10uf 16v

C8C7: 10uf 16v

C11J2: 10uf 16v

EC3 (Missing): ? ? 2.40v+, same thing as EC65, measured resistance, probably will prevent the board form booting if a cap is placed there, then again there are caps in place by stock that do the same thing...

EC4: 10uf 16v

EC5: 100uf 16v

EC6: 100uf 16v

EC7: 100uf 16v

EC8 (Missing): ? +12.00v

EC9: 10uf 16v

EC10: 470uf 16v +5.00v

EC11: 470uf 16v +5.00v

EC12: 10uf 16v

EC13: 1500uf 16v +12.00v

EC14: 22uf 25v (AB0, Couldn't read on AC0)

EC15: 3300uf 6.3v CPU-VDD

EC16 (Missing): ? +12.00v

EC17: 100uf 16v

EC18 (Missing): ? +12.00v

EC19 (Missing): ? +3.33v

EC20: 3300uf 6.3v CPU-VDD

EC21: 1500uf 16v +12.00v

EC22: 1500uf 16v +12.00v

EC23: 3300uf 6.3v CPU-VDD

EC25 (Missing): ? +3.33v

EC24: 10uf 16v

EC26: 100uf 16v

EC27: 10uf 16v

EC29 (Missing): ? +5.00v

EC2d: 100uf 16v

EC30: 100uf 16v

EC31 (Missing): ? +3.33v

EC32 (Missing): ? +5.00v

EC33: 3300uf 6.3v CPU-VDD

EC34 (Missing): ? +3.33v

EC35 (Missing): ? +5.00v

EC36: 3300uf 6.3v CPU-VDD

EC37: 1000uf 10v +5.00v

EC38 (Missing): ? +12.00v

EC40: 100uf 16v

EC41 (Missing): ? +3.33v

EC42: 10uf 16v Supposedly The South Bridge Voltage, 1.62v

EC43: 1000uf 6.3v AGP VDDQ (Main Cap)

EC44 (Missing): 10uf 16v ??? North Bridge Regulated Output, Hooks into the regulator chip, Used for smoothing out the regulator a bit, dn if it works

EC45: 10uf 16v

EC46: 10uf 16v

EC47: 1000uf 6.3v North Bridge Regulated Output (Main Cap)

EC50: 1000uf 6.3v MEM VDDQ

EC52 (Missing): 10uf 16v ??? North Bridge Regulated Output, to smooth out the fluctuations if any (there is by that point on the board).

EC53: 470uf 16v +5.00v

EC54 (Missing): ? +12.00v, probably for the SC2616.

EC55: 470uf 6.3v +3.33v

EC56: 1000uf 6.3v MEM VDDQ

EC57 (Missing): ? MEM VTT & VTT-Sense (VTT is tied directly to VTT-Sense unfortunatly..., there is no way of adjusting it separately without cutting the trace from under the board and redoing it)

EC59: 220uf 10v MEM VTT

EC60: 1000uf 10v +5.00v (Assumed MEM VDDQ Src)

EC61 (Missing): ?

EC62: 220uf 10v MEM VTT

EC63 (Missing): 4.7uf 16v ??? MEM VDDQ & ATMEL 24C32AN (CMOS / CMOS Reloaded) (From what it looks like, it looks like it's only for the CMOS)

EC64: 1000uf 10v +5.00v (Assumed MEM VDDQ Src)

EC65 (Missing): ? +5.00v, Supposedly (trodas) if you put a cap here the board won't post, Note that if measured resistance against ground it opens then closes immediately, hence to say it will prevent the board from starting up probably

EC66: 220uf 10v MEM VTT

EC67: 1000uf 6.3v MEM VDDQ

EC68: 220uf 10v MEM VTT

EC69: 1000uf 6.3v ??? Read 1.86v

CPU-VDD Source: EC13, EC21, EC22

Stock: 3x 1500uf (4500uf)

Better: 3x ??? (Using 1800uf for now)

Notes:

1800uf seems worse, but the better caps allow me to use lower vcore values and have them actually work... (only if the cpu speed is low enough)

CPU-VDD: EC15, EC20, EC23, EC33, EC36

Stock: 5x 3300uf (16500uf)

AGP-VDDQ: EC43

Stock: 1x 1000uf

NB-Voltage: EC47

Stock: 1x 1000uf

Better: 1x 1800uf

Notes:

Stability increased in memory timings and bus timings.

Stability increased by a decent amount with lower nb voltages.

Overall bandwith and stability increases.

MEM-SRC: EC60, EC64

Stock: 2x 1000uf (2000uf)

DataSheet: 3x 1500uf (4500uf)

MEM-VTT: EC59, EC62, EC66, EC68

Stock: 4x 220uf (880uf)

DataSheet: 1x 1500uf

MEM-VDDQ: EC50, EC56, EC67

Stock: 3x 1000uf (3000uf)

Better: 3x 1800uf (5400uf)

DataSheet: 2x 3300uf (6600uf)

Notes:

Big improvements in load, ie 2x512m is allmost like 1x512m.

Bandwith and stability overall is slightly higher.

CPU-VDD is less dependant on memory load and config types.

;;;

;;; Coils:

LC5: MEM-VDDQ, Offset: -0.1v

;;;

;;; North Bridge Readings:

Q18: (Regulator)

BIOS: Actual

1.6v: 1.62v

1.7v: 1.73v

1.8v: 1.83v

1.9v: 1.94v

EC52: (After Fet)

BIOS: Actual

1.6v: 1.62v

1.7v: 1.73v

1.8v: 1.83v

1.9v: 1.94v

EC44: (After Fet, way after...)

Seemed lower then the last cap...

1.72v I believe.

Read the Regulator by reading off the leg towards the bottom, next to the board's screw hole (MH6).

;;;

;;; AGP Readings:

Q12: AGP Regulator

Src: +3.33v

BIOS: Actual (BIOS VAGP Setting Thingy)

1.5v: 1.54v

1.6v: 1.64v

1.7v: 1.74v

1.8v: 1.84v

Measure by top leg, closest to agp slot.

;;;

;;; MEM Readings:

Q21: VDDQ Regulated Final Output To Memory.

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 2.60v

2.7v: 2.71v

2.8v: 2.80v

2.9v: 2.91v

3.0v: 3.00v

3.1v: 3.09v

3.2v: 3.19v

3.3v: 3.29v

Q23: VDDQ Regulated Output To Q21.

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 2.63v

2.7v: 2.72v

2.8v: 2.82v

2.9v: 2.92v

3.0v: 3.01v

3.1v: 3.10v

3.2v: 3.18v

3.3v: 3.29v

Q26: ??? (Seems like Regulated Rail To Q23, not sure yet)

Measure Q21 By it's base.

Measure Q23 By the leg closest to Q21.

Update!: I apparently have no idea how to really measure those mem fets, neither does anyone else...

Go by the darn caps on the board, there's a huge diff!, I'd otherwise go by the fets if I knew how they were configured and how to read them.

Also note that it's about equal with VTT that way, now it makes sense...

Also that's why mbm reads it way off, like it should apparently, when sensor is *0.016 (I dn if that calculation for the sensor is correct though).

EC63: (Missing cap, VDDQ, It's inbetween slots 1+2 (farthest and 2nd farthest away from chipset, ie labled slot 2+3 on the board)

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 2.68v

2.7v: 2.79v

2.8v: 2.88v

2.9v: 2.99v

3.0v: 3.08v

3.1v: 3.18v

3.2v: 3.28v

3.3v: 3.39v

EC57: MEM VTT / VTT-Sense

BIOS: Actual (BIOS VDDQ Setting)

2.6v: 1.35v

2.7v: 1.4v

2.8v: 1.45v

2.9v: 1.5v

3.0v: 1.54v

3.1v: 1.6v

3.2v: 1.65v

3.3v; 1.7v (note a 3.4v vddq would be for this vtt if it was a stock 1/2 setup, it's making sense now, mobo overvolts by 0.1v and doesn't tell you...)

MEM FeadBack (VDDQ-Sense) Readings: (Via After Resistor just before the pin on the SC2616)

BIOS: Actual

2.6v: 1.27v

2.7v: 1.27v ...

Wth you know...

That's not how the bios is setting voltage, it is using it as a slight offset though.

That would be my guess.

What the heck though.

I dn understand yet...

;;;

R186: Black 25C

Around 9.5k stock resistance, I think (9.49k, left ground)

MEM-VDDQ & MEM-VTT Pencil Mod

You can max the VTT and VDDQ this way..., and I mean max...

8.87k = 2.87v

I want something inbetween these 2 values...

8.75k = 2.92v

8.49k = +0.4v

Supposedly it's an 18.2k resistor

25 = 178

C = 100

= 17800, 17.8k

Code:

;;; Intersil HIP6301CB

Default-Spec: 1.1v-1.85v

Default: 1.1v-2v (1.25v-2v?)

VSEN:

-10% of VCORE

Causes Power Good To Go Low.

+15% of VCORE

Causes CPU power shutdown until VCORE is lower then +15% then set VID.

;;;

vcore mod by fb to ground

ocp mod

Phillips LM3580

CSI 93C46S

0340H

Texas Instruments GD75232

39K

FR95

Winbond

5TS-S

346GB

Intersil HIP6301CB CPU

Intersil HIP6601BCB CPU

Phillips 74HCT74D Wierd

Attansic AT209S PCI Arbiter & Clock Buffer

Attansic ATXP1 Overclock Controller

IDT/ICS ICS1893AF Intergrated nVidia LAN

Texas Instruments LC06A Buffer/Hex Inverter

Zuletzt bearbeitet:

Sehr interessant und informativ. Ich nehme vorallem das hier mit:Für mich der bisher informativste Post bisher : link

3-3-2-3, 9-13

0-0-2-2-0-5-3

cas3, cmd2

dc, 2x 256m

1.7v vdd, 2.8v vmem

250mhz fsb @ 10.5x, @ 1.9v

Sprich wenn da von 275Mhz die Rede ist, dann ist das kaum schneller als unsere 250Mhz...

The Sandman

Urgestein

Eher interessant ist, ob die Boards die 260-MHz+ mit CMD2 verlassen können. Ob auch das Shuttle damals so nach unten frisiert wurde? Ist aber auch der Grund, warum ich nen AIDA-Screen mache statt CPU-z - die CR sieht man da.

The Sandman

Urgestein

Ahm, hab hier noch was für die LP Bler was dieses winzige würfelartige Bauteil aka "bridging cap" unterhalb der RAM-Slots bei den VRM's betrifft:

www.hardwareluxx.de

www.hardwareluxx.de

Auch:

Was bei mir von grün zu schwarz wurde, wird wahrscheinlich etwas gewesen sein, was eine Garantieverwehrung bewirkt hat. Das grüne Zeug unter dem Arretierungshebel scheint ab einer gewissen Temperatur schwarz und hart zu werden. DFI hat sich wohl gegen Hardcore-Overclocker gewehrt und denen dadurch die Garantie verweigert. Smarter Wu - wieder mal

- wieder mal

Mainboard DFI NFII Ultra -Infinity - Sammelthread

nö... mein board macht im SC 261,5 mit dem 06/19 bios :love: und DC wird mit mehr vdimm sicherlich auch möglich sein nur habe ich die shice kiste immernoch nicht wieder zusammen, da mir noch 'ne pumpe fehlt ich brauche kein anderes bios

Auch:

Was bei mir von grün zu schwarz wurde, wird wahrscheinlich etwas gewesen sein, was eine Garantieverwehrung bewirkt hat. Das grüne Zeug unter dem Arretierungshebel scheint ab einer gewissen Temperatur schwarz und hart zu werden. DFI hat sich wohl gegen Hardcore-Overclocker gewehrt und denen dadurch die Garantie verweigert. Smarter Wu

- wieder mal

- wieder mal

Zuletzt bearbeitet:

Nonaamee

Urgestein

Heute war das Epox 8KHA+ mit KT266A nochmal dran. Die NB macht die 200MHz wohl ganz gut mit. Leider kann man nicht noch mehr einstellen 😅

Aber ich bekomm es einfach nicht hin, den Ram 1:1 mitlaufen zu lassen....

Finde ich nicht schlecht, für einen Chip der für nur 133Mhz ausgelegt ist.

Aber ich bekomm es einfach nicht hin, den Ram 1:1 mitlaufen zu lassen....

Finde ich nicht schlecht, für einen Chip der für nur 133Mhz ausgelegt ist.

Ich habe heute ein ENMIC 8NAX+ bekommen, war als defekt bei ebay drin. Board funktioniert aber bestens, keine Probleme beim Starten und vorallem mit Post-Code-Anzeige. Bilder dann morgen.

The Sandman

Urgestein

http://www.x86-secret.com/articles/ram/km400/km400en-4.htm

OverclockersShootout-Overclocked CPU's and hardware rewievs

OverclockersShootout-Overclocked CPU's and hardwaretesting.

web.archive.org

Zuletzt bearbeitet:

Sparksnl

Urgestein

I just quicktested a Palomino Athlon XP 2000+. It seems to be running Ok for a Palomino, 2GHz @1.975v.

Is this an Ok or a good OC? For me it is 17 years ago at least since I used one...

Is this an Ok or a good OC? For me it is 17 years ago at least since I used one...

My guess is that most of the users in this thread aren't clocking Palominos. Tbred B and Barton just clock way better... I got some Palos here, but i haven't bent the pins back yet (got them as trash) let alone tested them.

Out of interest i just had a look at the HWBot results. Looks like most people with a 1900+ Palo ran it at default multi (12x). Can't you unlock Palominos and use a lower multi to at least get the FSB to 200Mhz?I remember painting the L1 Bridges on the cpu worked?!

Out of interest i just had a look at the HWBot results. Looks like most people with a 1900+ Palo ran it at default multi (12x). Can't you unlock Palominos and use a lower multi to at least get the FSB to 200Mhz?I remember painting the L1 Bridges on the cpu worked?!

Zuletzt bearbeitet:

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Sparksnl

Urgestein

I always thought it was impossible to unlock them.

I threw away enough Palo’s... Somehow I finally wanted to test one. And no regrets since this one seems to be good enough.

I will be testing 2 Thunderbirds as well.

I threw away enough Palo’s... Somehow I finally wanted to test one. And no regrets since this one seems to be good enough.

I will be testing 2 Thunderbirds as well.

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.510

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Results are always nice to see.

Yep, results are nice. I‘d also like to test some Palos, however my a7n8x are limited at 1.85v vcore in bios and i‘m not sure how far you can push it above 2V vcore without blowing up the board, let alone cooling it properly.

Sparksnl

Urgestein

I will be finding out because I intend to max core voltage (watercooled, 2.2v) 😁

I should probably test it on the 1700 Palo first.

Edit: I just noticed that there are Thornton cpu’s made in week 51 With really low batch numbers.

I could not help buying all available (2)...

I should probably test it on the 1700 Palo first.

Edit: I just noticed that there are Thornton cpu’s made in week 51 With really low batch numbers.

I could not help buying all available (2)...

Zuletzt bearbeitet:

Now you got me thinking. I still have a nf7 with me which tops out at around 220mhz fsb, but that one is perfect for palominos as the nf7 got a max. vcore of 2.25V. Paired with 2x512mb tccds that might be a killer combo for 32M on old chips.

I got my trusty old watercooling right next to it (nexxxos xp bold, airplex evo 360, eheim 1046), so that might get interesting if i got a decent chip in my pile of cpus.

I got my trusty old watercooling right next to it (nexxxos xp bold, airplex evo 360, eheim 1046), so that might get interesting if i got a decent chip in my pile of cpus.