Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

AMDs Sockel-AM5 soll DDR5, aber kein PCIe 5.0 mitbringen

- Ersteller HWL News Bot

- Erstellt am

G

Gelöschtes Mitglied 312983

Guest

Letzten Endes ist das eine künstliche Marktsegmentierung, denn wenn Genoa es kann, könnten es auch die Desktop Zen 4. Noch ist es aber ein Gerücht.

S

Sweetangel1988

Guest

Gibt es parallel überhaupt passende M.2s die von PCIe 5.0 profitieren würden?

Eine GPU läuft ja auch gut in PCIe 4.0

Die kommen zur computex 2021 raus Anfang Juni 2021.

Ist immer so bzw. werden angekündigt.

Kannst damit rechnen das bei Alderlake, Gigabyte/corsair etc.. *Langsame pcie 5.0 nvmes raus bringen werden*.

Bzw released werden die dann keine Ahnung August-Dezember. Wenn Alder lake raus kommt halt.

Ich meine kannst damit rechnen das welche so im minimum etwa 9000 mb/s lesen bereich raus kommen werden und 6000 mb/s schreiben.. obwohl bis 15.000 Wahrscheinlich im lesen möglich sein wird. Sowie 11.000-12.000 im schreiben.

Bzw. nach Aktuellen Stand für GPUs

Bremst bei aktuellen modellen 3.0 mini mini minimal aus.

4.0 reicht die nächste Zeit eh für die Gpus.

5.0 ist erstmal egal für gpus.. aber man muss auch sagen.

Um ehrlich zu sein, manche tuen für ne Workstation/server die gpu weg lassen . Verbauen statt ner gpu ne M.2 Karte pci expreess die mit 16 lanes angebunden wird bzw mit 4x m.2 Dann ist kannste auch PCI express 5.0 damit bzw. im pci express 5.0 x16 slot voll auslasten.

Zuletzt bearbeitet:

Holzmann

The Saint

- Mitglied seit

- 02.05.2017

- Beiträge

- 43.182

- Desktop System

- The Behemoth

- Details zu meinem Desktop

- Prozessor

- Intel® Core™ Ultra 9 285K

- Mainboard

- ASRock Z890 Taichi OCF

- Kühler

- CPU: ALC Core One Carbon

- Speicher

- GSkill 48GB F5-8400-TZ5CRK @9000 CL40 G2

- Grafikprozessor

- MSI Suprim RTX 5090 SOC Edition

- Display

- ASUS ROG Swift OLED PG34WCDM

- SSD

- Crucial T705 gen5 1TB System / Samsung 990 evo plus 2TB Daten

- Soundkarte

- Sound Blaster AE-5 Plus / beyerdynamic MMX 330 PRO

- Gehäuse

- Corsair 7000D

- Netzteil

- ASUS ROG Strix 1200 W Platinum ATX3.1

- Keyboard

- ASUS ROG Azoth

- Mouse

- ASUS ROG Spatha X on ASUS ROG Balteus

- Betriebssystem

- Win11 pro

- Sonstiges

- MO-RA3 420 LT White / D5 Next / Thrustmaster T 818 Base

Das waren noch ZeitenVobis.

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.541

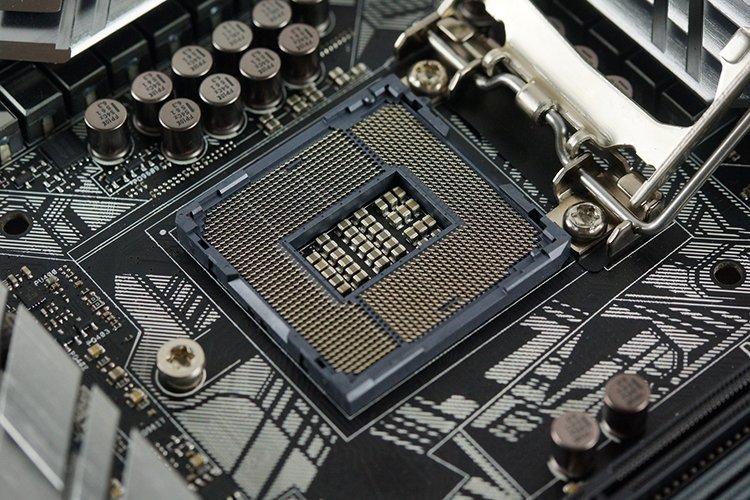

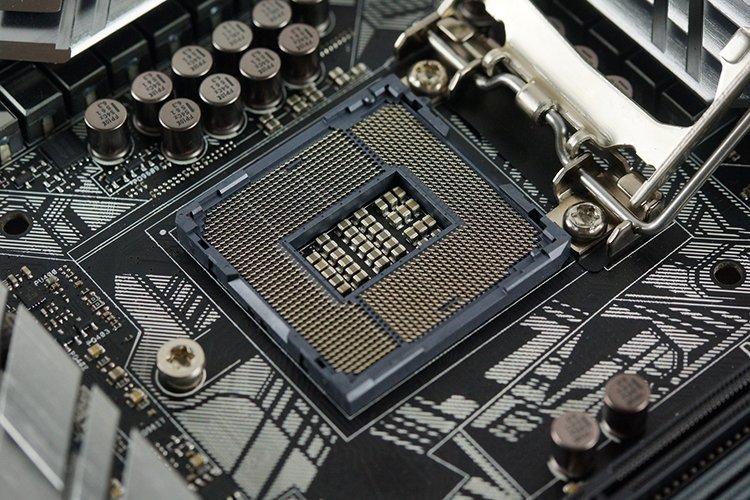

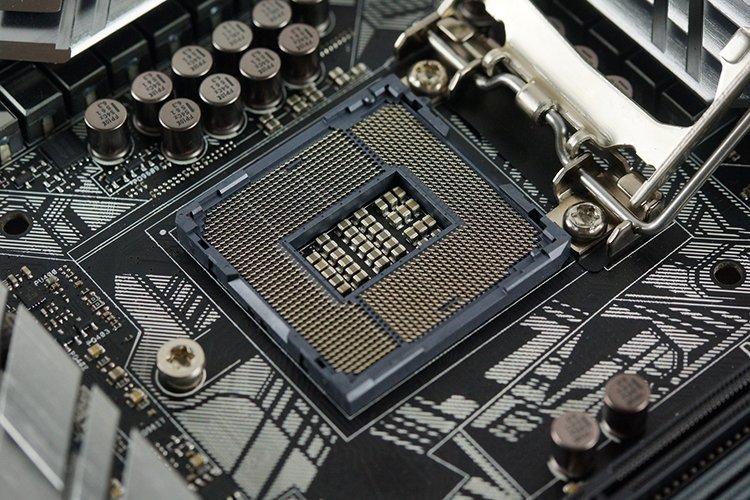

Ja, die Komplexität bzw. die Gefahr etwas zu beschädigen wandert im Grunde vom Prozessor in den Sockel. Ich weiß nicht was häufiger passiert: Jemand beschädigt seine Pins am Prozessor oder jemand beschädigt den Sockel. So dieser Moment halt:Ich kann die LGA-Sockel absolut nicht leiden, Pins kann ich gerade biegen oder sogar anlöten. Im Sockel ist das ungleich schwieriger -.-

So ein Montage-Mechanismus wie beim SP3 ist aber vor allem aufgrund des gleichmäßiges Drucks notwendig. Das gleiche gilt ja auch für die Sockel LGA3547 und LGA4189 von Intel. Hier müssen eben alle knapp 4.000 Pins Kontakt haben.Würde es begrüßen, denn die pins an der CPU sind schon sehr empfindlich, da es schon bei leicht verbogenen pins zu Fehlfunktionen kommen kann.

massaker

Enthusiast

- Mitglied seit

- 28.02.2008

- Beiträge

- 1.065

- Details zu meinem Desktop

- Prozessor

- Ryzen 5800X3D

- Mainboard

- ASUS C8E

- Kühler

- TechN x570 Nickel

- Speicher

- G.Skill RipJaws Black 64GB @3600MHz CL-14-14-14-28-42-272T

- Grafikprozessor

- Zotac 4090 AMP Extreme AIRO 24G @ Bykski

- Display

- LG UltraGear OLED 45GR95QE-B @240Hz

- SSD

- P5800X+905P+Micron9400Pro+FireCuda530 2TB+Aorus7000S 2TB+990Pro 4TB+5х870 4TB+4xMX500 2T+U3D 2T

- HDD

- WD 12TB+10TB+8TB+2x4TB, Seagate 4TB

- Opt. Laufwerk

- ASUS BW-16D1HT Blu-ray Brenner

- Soundkarte

- Creative BlasterX G6

- Gehäuse

- LianLi PC-V2120B Black BigTower

- Netzteil

- Corsair AX1600i

- Keyboard

- Logitech G910 Orion

- Mouse

- Razer DeathAdder + Logitech G900 + Logitech G502 Lightspeed

- Betriebssystem

- Win11 Pro

- Webbrowser

- Google Chrome

- Sonstiges

- 3xD5 für 2 Kreisläufe, MoRa420 extern, Aquaero 6 XT

Ja... höchstens angekündigt... Und eher Computex 2022 - dann evtl. nochmal angekündigtDie kommen zur computex 2021 raus Anfang Juni 2021.

Ist immer so bzw. werden angekündigt.

So wirklich in Endprodukten bei uns - so ca. 2023... LoL

So wirklich in Endprodukten bei uns - so ca. 2023... LoLIst das Deine Einschätzung? August-Dezember 2022 lasse ich gelten... Noch dieses Jahr - halte ich für sehr unwahrscheinlich.... released werden die dann keine Ahnung August-Dezember. Wenn Alder lake raus kommt halt.

Sind das alles Deine Schätzungen? Oder gibt's eine Quelle? (Ich habe da eigentlich auch gewisse Schätzungen, etwas abweichend, will aber nicht zu sehr öffentlich spekulieren)Ich meine kannst damit rechnen das welche so im minimum etwa 9000 mb/s lesen bereich raus kommen werden und 6000 mb/s schreiben.. obwohl bis 15.000 Wahrscheinlich im lesen möglich sein wird. Sowie 11.000-12.000 im schreiben.

Ja, genau so, aber am besten gleich ein Epyc/Threadripper-System... aber bis solche mit PCIe5.0-Unterstützung rauskommen, dauert wiederum paar Jährchen, also sind wir wieder mindestens bei 2023...statt ner gpu ne M.2 Karte pci expreess die mit 16 lanes angebunden wird bzw mit 4x m.2 Dann ist kannste auch PCI express 5.0 damit bzw. im pci express 5.0 x16 slot voll auslasten.

pumuckel

Urgestein

- Mitglied seit

- 13.12.2002

- Beiträge

- 8.199

- Ort

- Bayern

- Desktop System

- Workstation

- Laptop

- Acer Travemate AMD 4650 pro - 32GB 2TB und Samsung S6 Lite Tablet mit pen

- Details zu meinem Desktop

- Prozessor

- i5 12600 (non k - AVX 512 fähig)

- Mainboard

- AsRock z690 itx TB4 (nur weil super billig bekommen)

- Kühler

- Thermalright SI-100 full black (toller Kühler!)

- Speicher

- 2*16GB Corsair 6000 30-36-36-76 ( (nur weil super billig bekommen))

- Grafikprozessor

- PNY 4070 XLR8 - undervolting incomming aber auch so sehr sparsam und leise

- Display

- LG48 Zoll C27 Oled (<50W modded) + Dell G2724 Pivot (18W) + 2 Lenovo T22( (je 9W)

- SSD

- 4TB WD 850x (nur weil super billig bekommen)

- HDD

- dafür hat man Truenas Scale :)

- Opt. Laufwerk

- was ist ein optisches Laufwerk ? Datasette ?

- Soundkarte

- onboard mit Logitech Z906 per opt - oder interne des LG Oled je nach Game/Anwendung

- Gehäuse

- Cooler Master HAF Stacker 915R (davon hab ich 3 übereinander für 3 Systeme)

- Netzteil

- Seasonic Focus PX-750

- Keyboard

- Razer Tartarus 2 Gamepad, Huntsman V2 TKL Red mit Pud-Caps, (rein nur um nur noch eine SW zu haben)

- Mouse

- Razer Basilisk V3 (rein nur um nur noch eine SW zu haben)

- Betriebssystem

- Leider auf dem Hauptsystem nun Win 11

- Webbrowser

- Firefox (full privacy modded) und Librewolf portable (für Käufe), dazu Vivaldi (für den Rest)

- Sonstiges

- in den Rear NVMe 4*4x slot kommt noch ein Riser Cable für ne 10GBe Karte irgendwann

Pcie 5.0 wird interessant wegen Compute eXpress Link (CXL)

S

Sweetangel1988

Guest

1.Ja... höchstens angekündigt... Und eher Computex 2022 - dann evtl. nochmal angekündigtSo wirklich in Endprodukten bei uns - so ca. 2023... LoL

2.Ist das Deine Einschätzung? August-Dezember 2022 lasse ich gelten... Noch dieses Jahr - halte ich für sehr unwahrscheinlich.

3.Sind das alles Deine Schätzungen? Oder gibt's eine Quelle? (Ich habe da eigentlich auch gewisse Schätzungen, etwas abweichend, will aber nicht zu sehr öffentlich spekulieren)

1. Nein, Selbe bei AM4 bzw. PCI Express 4.0 / X570 Kamm 2019 raus bzw. direkt zu release gabs. Corsair/Gigabyte NVMES mit 4.0. Auch zu sagen es gab anfangs nur 2 Modelle von Corsair nur 1 und 1 von Gigabyte (Das wars) bzw als /500/ 1tb variante.

2. Ich richte Mich ungefähr zu den Release wann Alderlake raus kommt.. obs jetzt August/september/okotober/November/dezmber raus kommt.. ist unterm schnitt egal.. wahrscheinlich eher Oktober - Dezember .. aber Ja wäre ne Einschätzung.

3. Ja das sind meine Einschätzungen , war bei 3.0 /4.0 Exaktiv gleich. Ich meine die ersten 3.0 NVMES die langsamen waren bei etwa 40-50% der Maximalen Lese /schreibgeschweindigkeit des topmodel bzw zb der 970 evo. Also etwa bei 1500 Mb/s lesen bzw. die Schnellste bei 3500 mb/s lesen. Die Langsamen 4.0 NVMES bei bei 5000-5500 mb/s lesen , die topmodelle bei 7500 mb/s (lesen). Also kannste bei doppelter datenrate zu 4.0 ungefähr diesen wert von ungefähr 9000 mb/s lesen (erwarten) bei den ersten modellen. Bzw. bei doppelte Bandbreite zu 4.0 bzw bei 5.0 . Kannste bei den Top modellen.. aber die werden wahrscheinlich. frühstens gegen ende 2022 /Anfang 2023 draussen sein bei max 15.000 lesen sein wenn bei 4.0 Aktuell bei 7500 (feierabend ist).

- Mitglied seit

- 15.10.2004

- Beiträge

- 5.264

- Ort

- Berlin

- Desktop System

- EIMER

- Laptop

- Schleppi

- Details zu meinem Desktop

- Prozessor

- Intel® Core™ Ultra 7 265K

- Mainboard

- ASUS STRIX Z890-A Gaming WiFi

- Kühler

- Watercool Heatkiller PRO

- Speicher

- G.SKILL Trident Z5 - 32 GB DDR5-8000 non RGB

- Grafikprozessor

- ASUS RTX 4090 TUF @Heatkiller V

- Display

- Asus VG28UQL1A 4K

- SSD

- Ganz ganz viele

- HDD

- keine

- Opt. Laufwerk

- Blue-Ray Brenner für Backups

- Soundkarte

- Creative XFi-Titanium + Sennheiser HD 555

- Gehäuse

- Corsair Obsidian 900D

- Netzteil

- Enermax MaxTytan 1050 W Titanium

- Keyboard

- Logitech K800

- Mouse

- Logitech G900

- Betriebssystem

- Windows 11 Prof.

- Webbrowser

- Mozilla Firefox

- Sonstiges

- Custom Wakü

- Internet

- ▼1000 Mbit ▲50 Mbit

Also ich bin schon ne Weile dabei, hab es aber in all den Jahren bei Intel nicht geschafft einen Sockel zu ruinieren.Ich bin da schon vorsichtig, keine Sorge. Ist für mich persönlich trotzdem nerviger als die Pins an der CPU zu richten und das hab ich oft getan.

Aber, wenn du schon PINs gerade biegen musstest dann weiß ich auch nicht weiter. Ich glaube, bei Intel war der Sockel 478 der letzte mit Pins (2001).

G

Gelöschtes Mitglied 312983

Guest

Die Lands im Sockel waren im retail Geschäft öfter kaputt als einem lieb ist, sei es durch unsachgemäße Handhabung oder schlechten Versand. Gibt da viele Möglichkeiten die Kunden nutzen können. Wir hatten auch mal jemanden, der hat zwei DVI-I auf DVI-D an seiner GPU geschrottet, weil der Adapter nicht reinwollte ohne KrafteinwirkungAlso ich bin schon ne Weile dabei, hab es aber in all den Jahren bei Intel nicht geschafft einen Sockel zu ruinieren.

Aber, wenn du schon PINs gerade biegen musstest dann weiß ich auch nicht weiter. Ich glaube, bei Intel war der Sockel 478 der letzte mit Pins (2001).

Btw: https://www.hardwareluxx.de/community/threads/grrrrr-lga-pins-verbogen.1297644/

Das gilt aber nur, wenn der genoa i/o-die direkt mit dem desktop die verwandt ist. Kann natürlich sein, dass der verwendete pcie controller das kann, man im desktop die 5.0 Kompatibilität abschaltet.Letzten Endes ist das eine künstliche Marktsegmentierung, denn wenn Genoa es kann, könnten es auch die Desktop Zen 4.

Aber bringt uns Endanwendern ja derzeit eh keine vorteile....

massaker

Enthusiast

- Mitglied seit

- 28.02.2008

- Beiträge

- 1.065

- Details zu meinem Desktop

- Prozessor

- Ryzen 5800X3D

- Mainboard

- ASUS C8E

- Kühler

- TechN x570 Nickel

- Speicher

- G.Skill RipJaws Black 64GB @3600MHz CL-14-14-14-28-42-272T

- Grafikprozessor

- Zotac 4090 AMP Extreme AIRO 24G @ Bykski

- Display

- LG UltraGear OLED 45GR95QE-B @240Hz

- SSD

- P5800X+905P+Micron9400Pro+FireCuda530 2TB+Aorus7000S 2TB+990Pro 4TB+5х870 4TB+4xMX500 2T+U3D 2T

- HDD

- WD 12TB+10TB+8TB+2x4TB, Seagate 4TB

- Opt. Laufwerk

- ASUS BW-16D1HT Blu-ray Brenner

- Soundkarte

- Creative BlasterX G6

- Gehäuse

- LianLi PC-V2120B Black BigTower

- Netzteil

- Corsair AX1600i

- Keyboard

- Logitech G910 Orion

- Mouse

- Razer DeathAdder + Logitech G900 + Logitech G502 Lightspeed

- Betriebssystem

- Win11 Pro

- Webbrowser

- Google Chrome

- Sonstiges

- 3xD5 für 2 Kreisläufe, MoRa420 extern, Aquaero 6 XT

1, 2. Ja, ich hoffe ja auch, dass sie rechtzeitig zum Release von Intel fertig werden, befürchte aber, dass entweder Intel was nach hinten verlegt oder genauso wie AMD PCIe5.0-Unterstützung komplett um 1 Release verschiebt. Die haben bei sich doch erst (mit großer Verspätung) PCIe4.0 endlich eingeführt. Und die SSD-Hersteller haben ja grad erst angefangen (zumindest bei sequentiellen Übertragungen) die PCIe4.0-Schnittstelle auszureizen, wobei da auch noch längst nicht alles glatt läuft (versuch mal von einer PCIe4.0-SSD auf andere zu kopieren und Du siehst dann ~2-2,2GB/s! statt ~1,8-1,9GB/s bei PCIe3.0).1. Nein, Selbe bei AM4 bzw. PCI Express 4.0 / X570 Kamm 2019 raus bzw. direkt zu release gabs. Corsair/Gigabyte NVMES mit 4.0. Auch zu sagen es gab anfangs nur 2 Modelle von Corsair nur 1 und 1 von Gigabyte (Das wars) bzw als /500/ 1tb variante.

2. Ich richte Mich ungefähr zu den Release wann Alderlake raus kommt.. obs jetzt August/september/okotober/November/dezmber raus kommt.. ist unterm schnitt egal.. wahrscheinlich eher Oktober - Dezember .. aber Ja wäre ne Einschätzung.

3. Ja das sind meine Einschätzungen , war bei 3.0 /4.0 Exaktiv gleich. Ich meine die ersten 3.0 NVMES die langsamen waren bei etwa 40-50% der Maximalen Lese /schreibgeschweindigkeit des topmodel bzw zb der 970 evo. Also etwa bei 1500 Mb/s lesen bzw. die Schnellste bei 3500 mb/s lesen. Die Langsamen 4.0 NVMES bei bei 5000-5500 mb/s lesen , die topmodelle bei 7500 mb/s (lesen). Also kannste bei doppelter datenrate zu 4.0 ungefähr diesen wert von ungefähr 9000 mb/s lesen (erwarten) bei den ersten modellen. Bzw. bei doppelte Bandbreite zu 4.0 bzw bei 5.0 . Kannste bei den Top modellen.. aber die werden wahrscheinlich. frühstens gegen ende 2022 /Anfang 2023 draussen sein bei max 15.000 lesen sein wenn bei 4.0 Aktuell bei 7500 (feierabend ist).

3. OK, hatte ähnliche Überlegungen wie Du. Aber bedenke die 7,5 GB/s - das ist echt Spitzenwert und eher Ausnahme (war das nicht irgendwo in Phison-Labor? Wer weiß welche optimale Bedingungen die dazu geschaffen haben...womöglich PCIe-Bus um 1% zusätzlich übertaktet?). Also absolute Spitze bei PCIe3.0 ist ~3600-3625 (auf meinem Brett sind's 3580MB/s), demnach beim Ausreizen von PCIe4.0 Schnittstelle werden wir wohl maximal 7200-7250 MB/s erleben. Weiter extrapoliert - beim Ausreizen von PCIe5.0 sehen wir dann wohl maximal 14-14,5 GB/s, keine 15GB/s. Und die ersten (frühen) PCIe5.0 SSDs habe ich halt etwas optimistischer als Du auf 10.000MB/s Lesen und 8.000MB/s Schreiben eingeschätzt, wobei Letzteres wohl fast schon zu optimistisch ist, Schreiben wohl eher 7000-7500 am Anfang und erst paar Jahre später bis zu. ~13GB/s (wenn wir schon als Spitze bei PCIe4.0 6500-6800 MB/s sehen!).

KaerMorhen

Legende

- Mitglied seit

- 17.04.2010

- Beiträge

- 17.352

- Laptop

- RaspberryPi 4B 8GB, Nintendo Switch

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D (CO -35 All Core)

- Mainboard

- Asus ROG Strix X670E -E Gaming Wifi

- Kühler

- TechN AM5

- Speicher

- G.Skill Trident Z5 NEO Schwarz 6000Mhz CL30 EXPO

- Grafikprozessor

- PowerColor Red Devil Radeon RX 7900 XTX @Asrock Aqua OC/Sapphire Nitro+ // EK-Quantum Vector² D-RGB

- Display

- Xiaomi Mi Curved Gaming Monitor 34" // 2x Dell Ultrasharp U2515H // Samsung 4K 28"

- SSD

- Corsair Force MP510B // WD BLACK SN750 // Samsung 980 Pro // 2x Samsung 840 Pro //2x Samsung 870

- HDD

- WD Blue 4TB, 2x WD 3TB

- Soundkarte

- Onboard, Arctis Nova Pro Wireless Headset + DAC, HyperX QuadCast+ Aokeo AK-55 LP, StreamDeck+ Dock

- Gehäuse

- Fractal Meshify 2 XL

- Netzteil

- DARK POWER PRO 12 1200W //

- Keyboard

- Corsair K100 RGB OPX

- Mouse

- Corsair DARK CORE RGB PRO SE // Corsair DARK CORE RGB PRO

- Betriebssystem

- Win10 Pro / Win11 Pro/ Win11 Pro IoT/ Mint 22

- Sonstiges

- High Flow Next // D5 Next // Mo-Ra3 420@200 // Mo-Ra3 360@120 // Mo-Ra2@120 // 1x Mo-Ra2 Eisbad

Ich musst gerade kürzlich mein Z68 Board entsorfen da einige Pins hinüber waren (definitiv irreparable), sehr ärgerlich, war aber auch das Erste Board das jemals so sein Ende gefunden hat.

Ich habe bei AMD einmal gehabt dass beim CPU ablösen trotz erwärmen 3 Pins stecken geblieben sind, das kommt glaube ich garnicht so selten vor und ist bei Intel Geschichte.

Einheitliche Sockel bei Intel und AMD müsste dann ja auch die Kühlerkompatibilität etwas verändern oder irre ich?

Ich habe bei AMD einmal gehabt dass beim CPU ablösen trotz erwärmen 3 Pins stecken geblieben sind, das kommt glaube ich garnicht so selten vor und ist bei Intel Geschichte.

Einheitliche Sockel bei Intel und AMD müsste dann ja auch die Kühlerkompatibilität etwas verändern oder irre ich?

Techlogi

Legende

- Mitglied seit

- 25.02.2006

- Beiträge

- 14.306

- Ort

- Lübeck

- Desktop System

- Desktop

- Laptop

- Laptop

- Details zu meinem Desktop

- Prozessor

- Ryzen 7 9800X3D; Watercooled (HK IV)

- Mainboard

- Asus B650E-E Gaming

- Kühler

- Mora420 9*P14; HK RAD 360S 3*P12; HK Tube; 2*D5 Next; Iceman Messing Dualtop; HF Next; Octo; CPC NS6

- Speicher

- 2x32gb Corsair Vengeance 6000 CL30

- Grafikprozessor

- Radeon 6800XT Ref. @2.5ghz, 350W PL; Watercooled (HK V)

- Display

- Dell S3220DGF + 2x U2415 + Panasonic TX-50ASW654

- SSD

- OS: Intel Optane 900P 280GB // Spiele: WD Black SN850X 4TB // Bench-OS: Samsung 970 Evo 250GB

- Soundkarte

- Onboard, Realtek ALC1220

- Gehäuse

- LianLi O11 EVO schwarz; Coldzero Backplate; 7x Arctic P12 ARGB

- Netzteil

- be quiet! Straight Power 11 850W Platinum

- Keyboard

- Logitech Illuminated

- Mouse

- Logitech MX518 Refresh

- Betriebssystem

- Win11 EN

- Sonstiges

- Asus XG-C100C V2 (10GbE); Xbox 360 Wireless Controller; TP-Link UH720 USB-Hub

- Internet

- ▼250Mbit ▲40Mbit

@KaerMorhen Was meinst du mit "einheitlicher Sockel"?

KaerMorhen

Legende

- Mitglied seit

- 17.04.2010

- Beiträge

- 17.352

- Laptop

- RaspberryPi 4B 8GB, Nintendo Switch

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D (CO -35 All Core)

- Mainboard

- Asus ROG Strix X670E -E Gaming Wifi

- Kühler

- TechN AM5

- Speicher

- G.Skill Trident Z5 NEO Schwarz 6000Mhz CL30 EXPO

- Grafikprozessor

- PowerColor Red Devil Radeon RX 7900 XTX @Asrock Aqua OC/Sapphire Nitro+ // EK-Quantum Vector² D-RGB

- Display

- Xiaomi Mi Curved Gaming Monitor 34" // 2x Dell Ultrasharp U2515H // Samsung 4K 28"

- SSD

- Corsair Force MP510B // WD BLACK SN750 // Samsung 980 Pro // 2x Samsung 840 Pro //2x Samsung 870

- HDD

- WD Blue 4TB, 2x WD 3TB

- Soundkarte

- Onboard, Arctis Nova Pro Wireless Headset + DAC, HyperX QuadCast+ Aokeo AK-55 LP, StreamDeck+ Dock

- Gehäuse

- Fractal Meshify 2 XL

- Netzteil

- DARK POWER PRO 12 1200W //

- Keyboard

- Corsair K100 RGB OPX

- Mouse

- Corsair DARK CORE RGB PRO SE // Corsair DARK CORE RGB PRO

- Betriebssystem

- Win10 Pro / Win11 Pro/ Win11 Pro IoT/ Mint 22

- Sonstiges

- High Flow Next // D5 Next // Mo-Ra3 420@200 // Mo-Ra3 360@120 // Mo-Ra2@120 // 1x Mo-Ra2 Eisbad

Habe mich verlesen, AM5 kommt mit LGA 1718, Alder Lake mit LGA 1700, dachte das wäre derselbe Sockel somit ja auch genormte Grössen für Halterungen von Kühllösungen.@KaerMorhen Was meinst du mit "einheitlicher Sockel"?

DAS wäre mal was. Also wenn Intel und AMD sich einigen könnten das man die gleiche Anzahl Löcher mit dem gleichen Abstand um den Sockel und die gleiche Höhe des Packages bauen könnte. Ist aber wohl zu einfach...auch genormte Grössen für Halterungen von Kühllösungen.

Case39

Experte

- Mitglied seit

- 22.04.2016

- Beiträge

- 1.254

Das wird sich mit Alder Lake nochmal ändern. Warum sollten sie das auch machen? Bis jetzt haben die Kühlerhersteller. gute Arbeit geleistet.DAS wäre mal was. Also wenn Intel und AMD sich einigen könnten das man die gleiche Anzahl Löcher mit dem gleichen Abstand um den Sockel und die gleiche Höhe des Packages bauen könnte. Ist aber wohl zu einfach...

Und nur, weil manch einer jedes Jahr ne neue CPU/Mobo kauft, wird man u.U. keine technischen Kompromisse eingehen wollen.

PCIE 5.0 ist für den Consumerbereich einfach oversized. 4.0 ist für den Anfang schon sinnvoller und hält dannein paar Jahre.

KaerMorhen

Legende

- Mitglied seit

- 17.04.2010

- Beiträge

- 17.352

- Laptop

- RaspberryPi 4B 8GB, Nintendo Switch

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D (CO -35 All Core)

- Mainboard

- Asus ROG Strix X670E -E Gaming Wifi

- Kühler

- TechN AM5

- Speicher

- G.Skill Trident Z5 NEO Schwarz 6000Mhz CL30 EXPO

- Grafikprozessor

- PowerColor Red Devil Radeon RX 7900 XTX @Asrock Aqua OC/Sapphire Nitro+ // EK-Quantum Vector² D-RGB

- Display

- Xiaomi Mi Curved Gaming Monitor 34" // 2x Dell Ultrasharp U2515H // Samsung 4K 28"

- SSD

- Corsair Force MP510B // WD BLACK SN750 // Samsung 980 Pro // 2x Samsung 840 Pro //2x Samsung 870

- HDD

- WD Blue 4TB, 2x WD 3TB

- Soundkarte

- Onboard, Arctis Nova Pro Wireless Headset + DAC, HyperX QuadCast+ Aokeo AK-55 LP, StreamDeck+ Dock

- Gehäuse

- Fractal Meshify 2 XL

- Netzteil

- DARK POWER PRO 12 1200W //

- Keyboard

- Corsair K100 RGB OPX

- Mouse

- Corsair DARK CORE RGB PRO SE // Corsair DARK CORE RGB PRO

- Betriebssystem

- Win10 Pro / Win11 Pro/ Win11 Pro IoT/ Mint 22

- Sonstiges

- High Flow Next // D5 Next // Mo-Ra3 420@200 // Mo-Ra3 360@120 // Mo-Ra2@120 // 1x Mo-Ra2 Eisbad

Wieso sollte sich das nochmal ändern? Sockel 1700 für Alderlake steht fest. Wieso sollten Sie es nicht tun? Wenn AMD nun auf LGA 1718 geht.Das wird sich mit Alder Lake nochmal ändern. Warum sollten sie das auch machen? Bis jetzt haben die Kühlerhersteller. gute Arbeit geleistet.

Das wäre nicht so abwägig, sind dann ja lediglich die Lochabstände, die könnte man mit einer verstellbaren Halterung nutzen.

Gerade für Upgrades von alten Sockeln echt super.

Das wäre halt die Frage ob sich das ändert wenn AMD vom AM Sockel zum LGA wechselt.Sicher? Klar, das Package wird wohl deutlich rechteckiger, aber trotzdem sollten die derzeit im Quadrat angeordneten Löcher von Intel auch weiterhin passen. AMD hat die ja eh im Rechteck angeordnet.

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.541

Lochabstände kannst du mit Adaptern recht einfach ändern, Höhen im Package sind da schon schwieriger und genau da soll LGA1700 gegenüber LGA1200 deutlich (- 1 mm) anders sein.Das wäre nicht so abwägig, sind dann ja lediglich die Lochabstände, die könnte man mit einer verstellbaren Halterung nutzen.

Gerade für Upgrades von alten Sockeln echt super.

Holzmann

The Saint

- Mitglied seit

- 02.05.2017

- Beiträge

- 43.182

- Desktop System

- The Behemoth

- Details zu meinem Desktop

- Prozessor

- Intel® Core™ Ultra 9 285K

- Mainboard

- ASRock Z890 Taichi OCF

- Kühler

- CPU: ALC Core One Carbon

- Speicher

- GSkill 48GB F5-8400-TZ5CRK @9000 CL40 G2

- Grafikprozessor

- MSI Suprim RTX 5090 SOC Edition

- Display

- ASUS ROG Swift OLED PG34WCDM

- SSD

- Crucial T705 gen5 1TB System / Samsung 990 evo plus 2TB Daten

- Soundkarte

- Sound Blaster AE-5 Plus / beyerdynamic MMX 330 PRO

- Gehäuse

- Corsair 7000D

- Netzteil

- ASUS ROG Strix 1200 W Platinum ATX3.1

- Keyboard

- ASUS ROG Azoth

- Mouse

- ASUS ROG Spatha X on ASUS ROG Balteus

- Betriebssystem

- Win11 pro

- Sonstiges

- MO-RA3 420 LT White / D5 Next / Thrustmaster T 818 Base

Moin,

bin nicht ganz sicher, für den Fall das es schon gepostet wurde Sorry.

aber die Pins an der CPU sind bei AMD dann wohl mit AM5 Geschichte:

videocardz.com

videocardz.com

Also keine am Kühlerboden klebende aus dem Sockel gerissene PGA-CPUs mehr!

Ich bin enttäuscht.

bin nicht ganz sicher, für den Fall das es schon gepostet wurde Sorry.

aber die Pins an der CPU sind bei AMD dann wohl mit AM5 Geschichte:

AMD next-gen AM5 platform to feature LGA1718 socket - VideoCardz.com

AMD AM5 platform detailed ExecutableFix has revealed the first details on the upcoming next-gen AMD socket. AMD AM5, the successor to AM4 is to feature an LGA1718 socket. AMD is apparently changing its socket type from PGA to LGA (land grid array), which means there be no pins on the next-gen...

Also keine am Kühlerboden klebende aus dem Sockel gerissene PGA-CPUs mehr!

Ich bin enttäuscht.

Zuletzt bearbeitet:

- Mitglied seit

- 15.11.2002

- Beiträge

- 27.541

Moin,

bin nicht ganz sicher, für den Fall das es schon gepostet wurde Sorry.

aber die Pins an der CPU sind bei AMD dann wohl mit AM5 Geschichte:

Unter anderem darum geht es in einem Großteil der News …

smalM

Enthusiast

Dann iss ein stück schokolade vorher und geh mit normaler vorsicht an die sache ran.

Mit Tower-Kühler und 12cm-LüfterDie kommen zur computex 2021 raus Anfang Juni 2021.

Ist immer so bzw. werden angekündigt.

Kannst damit rechnen das bei Alderlake, Gigabyte/corsair etc.. *Langsame pcie 5.0 nvmes raus bringen werden*.

Bzw released werden die dann keine Ahnung August-Dezember. Wenn Alder lake raus kommt halt.

Ich meine kannst damit rechnen das welche so im minimum etwa 9000 mb/s lesen bereich raus kommen werden und 6000 mb/s schreiben.. obwohl bis 15.000 Wahrscheinlich im lesen möglich sein wird. Sowie 11.000-12.000 im schreiben.

Morrich

Legende

- Mitglied seit

- 29.08.2008

- Beiträge

- 5.681

Gut zusammengefasst. Der normale Nutzer profitiert im Moment kaum von PCIe 4.0, sprich 5.0 wäre derzeit nur ein Argument fürs Marketing. Ich kann daher voll und ganz verstehen, wenn AMD bei 4.0 bleibt bzw. verstehe nicht warum Intel mit LGA1700 auf PCIe 5.0 wechselt.

Du beantwortest dir deine Frage doch selbst. Intel kann mit PCIe 5.0 Marketing betreiben.

Und durch massives Marketing verkauft Intel auch heute, wo sie technisch hinterher hinken noch immer Millionen CPUs und andere Produkte.

Es ist also kein technisch notwendiges oder sinnvolles Feature, sondern bringt gute Presse.

sch4kal

Enthusiast

- Mitglied seit

- 18.07.2016

- Beiträge

- 4.411

- Desktop System

- PC

- Laptop

- Thinkpad E15 G4 AMD

- Details zu meinem Desktop

- Prozessor

- i9-13900K@P6.0B/E4.3B

- Mainboard

- Asus ROG Strix Z690-A Gaming WiFi D4@2103

- Kühler

- BeQuiet Silent Loop 2 360er

- Speicher

- 2x16 GB Ripjaws DDR4 @ 4133C15 + Subs

- Grafikprozessor

- Asus ROG Strix RTX 3090 OC

- Display

- Samsung Odyssey G7 27" WQHD@240Hz

- SSD

- Optane 900P 480GB PCIe, PM9A1 256GB M.2, Crucial P3 4TB M.2

- Gehäuse

- Fractal Define 7

- Netzteil

- Seasonic Prime TX-850W

- Keyboard

- Logitech Internet Navigator SE

- Mouse

- Logitech MX500

- Betriebssystem

- Win 10 Edu 2004, Gentoo, Fedora $latest

- Sonstiges

- Mellanox CX3 10G NIC via M.2 to PCIe Adapter

- Internet

- ▼100G ▲100G

Also wie bei Matisse damals...wobei Intel ja auch fast zeitgleich Sapphire Rapids released, und da bringt PCIe 5.0 ja durchaus was.Du beantwortest dir deine Frage doch selbst. Intel kann mit PCIe 5.0 Marketing betreiben.

Und durch massives Marketing verkauft Intel auch heute, wo sie technisch hinterher hinken noch immer Millionen CPUs und andere Produkte.

Es ist also kein technisch notwendiges oder sinnvolles Feature, sondern bringt gute Presse.

Holt

Legende

- Mitglied seit

- 05.07.2010

- Beiträge

- 30.102

Intel wird nicht wieder der zweite sein wollen, so wie sie es bei PCIe 4.0 waren und während AMD und seine Fanboys dies ausgeschlachtet haben, kommt jetzt, von der Ecke der Hinweis PCie 5.0 wäre für Consumer überflüssig. Das konnte man am Anfang und kann man selbst heute noch, aber ebenso für PCIe 4.0 sagen. Es geht aber eben auch um das Haben-Wollen und nicht nur um das Brauchen und wirklich sinnvoll (Aus-)Nutzen-Können.Der normale Nutzer profitiert im Moment kaum von PCIe 4.0, sprich 5.0 wäre derzeit nur ein Argument fürs Marketing. Ich kann daher voll und ganz verstehen, wenn AMD bei 4.0 bleibt bzw. verstehe nicht warum Intel mit LGA1700 auf PCIe 5.0 wechselt.

PCIe 4.0 erfordert eben bessere und teuere Materialien für die Mainboards, andere Komponenten für die Slots, Redriver und mehr Aufwand bei Routing der Lanes im Mainboard, was leicht auch zu mehr Layern führern kann. PCIe 5.0 drüfte die Kosten weiter treiben, aber so wie Intel bisher PCIe 4.0 nur bei den Lanes von der CPU bietet und wohl erst mit Alder Lake dann auch von Chipsatz, wird auch Alder Lake PCIe 5.0 erstmal nur PCIe 5.0 für die Lanes der CPU bieten, also wohl wieder 20, die 16 für die Graka und 4 für einen M.2 Slot.Ich bin gespannt was die Intel Platinen kosten werden mit PCIe 5.0 ... aktuelle Platinen von AMD und Intel mit 4.0 sind schon sau teuer

Ja das Henne-Ei Problem, ich erinnere mich noch an diese News von 2016:Nur dazu brauchts dann wieder entsprechende Komponenten die dann z.B. auch mit ner x1 Anbindung laufen (z.B. 10GBE Karten - da würde das mit Single-Port Karten schon gehen). Ist also mal wieder ein Henne-Ei Problem. Wobei die PCIe4 Infrastruktur gibt's ja nun auch schon seit 2 Jahren im Consumer-Bereich, Komponenten abseits von SSDs und Grakas gibt es aber bislang quasi nicht...

Bisher ist der NIC meines Wissens nach noch nicht erschienen, aber es gibt ja auch kaum eine passende Plattform. Für Server ist 10GbE heute nicht viel und schon gar nicht ein NIC mit nur einem Port, TR3 wäre eine passende Plattform, aber da gibt es so viele PCIe 4.0 Lanes, dafür kann man auch andere NICs nehmen die dann 2 oder 4 Lanes brauchen, gibt ja schon genug davon und im Mainstream ist 10GbE weiterhin selten und außer dem X570 gibt es keinen einzigen Chipsatz mit PCIe 4.0 Lanes und wer will schon dafür eine Lanes für den NIC auf Lanes der Graka oder den M.2 Slot der SSD verzichten? Eben, keiner und damit hätte so ein 10GbE NIC mit einer PCIe 4.0 Lane bisher keinen Markt.

Auch bei SSDs dürfte es darauf hinauslaufen, dass die Hersteller mit diese dann zeigen wollen, was machbar ist um entsprechend hohe Preise verlangen zu können, statt Modelle mit nur 2 PCIe 5.0 Lanes anzubieten, weshalb die Mainboardhersteller dann auch nicht mehr (also 2 statt einem) M.2 Slots mit diesen Lanes der CPU verbauen werden, wobei denn jeder nur 2 statt 4 Lanes hätte. Ganz einfach weil solche PCIe 5.0 x2 SSD nicht mit besseren Werten als eine PCIe 4.0 x4 SSD im Datenblatt glänzen könnte und man daher nicht mehr für sich verlangen könnten und die Mainboardhersteller werden keine 2 Slot mit je 2 Lanes wollen, weil alle Kunden die noch PCIe 3.0 x4 oder PCIe 4.0 x4 SSDs haben, diese sonst nur halber Bandbreite anbinden könnten.

Wobei die Frage ist, ob AMD wieder so lange am AM5 Sockel festhalten wird wie an AM4. Damals mussten sie dies machen, um überhaupt wieder einen Fuß in die Tür zu bekommen und haben es daher für AM4 und EYPC versprochen, nicht aber für TR der ja erst später gekommen ist und dessen Sockel nach 2 Generation auch ersetzt wurde, wobei der eigentliche Sockel physikalisch sogar identisch und praktisch auch mit EYPC identisch ist. Schon bei Zen2 hat dies zu Problemen geführt und Kompromisse erzwungen und da AMD und weit besser aufgestellt ist, würde es mich nicht wundern, wenn sie künftig den Sockel auch öfter wechseln würden, einfach weil dies technisch weniger Probleme bedeutet.Intel bleibt eh nur 2 Generationen bei einem Sockel. Sprich 2023/24 gibt's den Nachfolger von LGA1700. Und AMD hat ja mit Sockel AM4 schon gezeigt, das man auch innerhalb eines Sockels die PCIe Generation wechseln kann, wenn man das will.

Außerem sehe ich diese regelmäßigen Plattformwechsel auch nicht wirklich als so ein Problem an, die meisten machen entweder nur alle paar bis viele Jahre ein Systemupgrade und dann ist sowieso ein neues Board fällig oder nehmen jeder Generation mit und wollen dann auch das neuste Mainboard mit den neusten Features. Schau Dir an wie viele hier im Forum ihre AM4 Boards mit 300er Chipsatz beim Wechsel auf Zen+ gleich gegen eines mit 400er Chipsatz getauscht haben, nur beim Zen2 haben viele vor dem Preis und dem Lüfter auf X570 Boards zurückgeschreckt und die B550 (und A520) ließen ja lange auf sich warten. Ebenso haben auch nicht wenige ihrer neuen Rocket Lake CPU dann ein Z590 Mainboard spendiert, obwohl sie schon ein Z490 hatten. Außerdem kann man die gebrauchten Boards genauso wie die gebrauchte CPU weiterverkaufen und realisiert dann eben den Wertverlust sofort statt erst später, aber es verliert eben auch dann weiter an Wert, wenn man es länger weiternutzt. Es bleibt also einzig der Mehraufwand des Wechseln, aber manche treibt ja auch der Basteltrieb zum Upgrade und der wird dann umso besser befriedigt.

Das liegt eben daran, dass die schnellen SSDs umso mehr lange und parallele Zugriffe brauchen um überhaupt hohe Transferraten zu erreichen. Die gilt vor allem für die Leseraten, aber die sind wichtigen, wenn Schreibvorgänge werden in der Praxis meist gepuffert, auch auf der SSD selbst und daher merkt man von der Schreibperformance gerade bei kurzen Schreibzugriffen viel weniger als von der Leseperformance.Und bei SSDs das gleiche Spiel, 7gb/s reichen noch ewig, sogar mit 500mb/s SATA SSDs läuft derzeit das meiste absolut zufriedenstellend.

CDM nutzt entweder 8 parallele 1MB Zugriffe oder 32 Zugriffe über je nur 128k, zusammen also nur 4MB und trotzdem erreichen die meisten SSDs mit 32 parallelen 128k Zugriffen bessere Werte als über die 8MB auf die mit 8 parallelen 1MB Zugegriffen wird und AS-SSD mit seinem einzelnen Zugriffe über 16MB kommt auf viel schlechtere Werte. Nur kommen eben im Alltag kaum je solche viele parallelen und lange Zugriffe vor und damit kann man im Alltag gar nicht die hohen Transferraten aus den SSD kitzeln die in den Datenblättern stehen und bei PCIe 5.0 SSD wird dies nochmal schwerer werden. Für mehr Alltagsperformance mit die Latenz runter, als die 4k QD1 Lesend müssen rauf, aber dazu muss vor allem die Laten des NANDs sinken, denn die macht den Löwenanteil der Laten einer SSD aus.

Das Problem ist aber dann die Verbindungstechnik der Dies, denn bei der von AMD bisher verwendeten traditionellen Verbindungstechnologie über die Platine statt mit Halbleitern wie Intel EMIB, ist man hart an der Grenze:Ich könnte durchaus verstehen, wenn man beim nächsten Shrink (12nm+?) des I/O-Die auf DDR5 und PCIe 4 geht und beim übernächsten (7nm?) dann auf PCIe 5.

So ein I/O Die braucht eben viele Verbindungen und damit viel Fläche oder einen Halbleiterinterposer, der aber die Kosten deutlich erhöht. Hat man genaug Platz unter dem HS des Packages, dann macht es keinen Sinn den I/O Die kleiner zu machen und da AMD noch bis Ende 2024 Wafer von GF beziehen wird, würde ich vorher nicht mit einem Shrink des I/O Dies rechnen, denn es ist doch angeblich schon in 12nm und alles darunter wären ein Prozess den GF nicht bietet und dazu würde man wohl einen teuren Halbleiterinterposer oder ein unnötig großes Die brauchen.

PCIe 4.0 SSDs gab es zum Start von X570 auch noch nicht und die ersten waren alles solche mit dem Phison E16, der ein E12 nur mit PCIe 4.0 statt PCIe 3.0 Anbindung war. Aber es dürften dann sicher bald erste PCIe 5.0 SSDs geben, auch wenn dies anfangs auch nur bekannte PCIe 4.0 Controller mit auf PCIe 5.0 aufgebohrtem Interface sind, die also die Bandbreite der Schnittstelle gar nicht ausnutzen können. Dazu wird dann noch das Problem der Leistungsaufnahme und damit der Wärmeentwicklung kommen, schnellere Übertragungen erhöhen immer auch die Leistungsaufnahme (was man ja auch beim Ethernet über Kupfer sieht) und dazu braucht eine SSD um wirklich schneller zu werden auch einen schnelleren Controller, also einen mit mehr Kernen oder mehr Takt und es müssen mehr RAM Dies parallel angesprochen werden, was dann dazu zwingt die Controller in noch effizierteren, also kleineren Fertigungsverfahren herzustellen, der Phiseon E18 wird in 12 nm FFC geferigt, E12 und E16 waren noch aus 28nm Fertigung und Samsung fertigt den Elpis Controller der 980 Pro in 8nm. Nur werden die Kosten vor allem der Entwicklung so eines Chips expotentiell höher, je kleiner der Fertigungsprozess ist und da geht es um Hunderte von Millionen USD für ein Design, solche SSD Controller und damit die SSDs werden dann also auch einiges kosten.Gibt es parallel überhaupt passende M.2s die von PCIe 5.0 profitieren würden?

Wie gesagt kann man echt darüber streiben wie weit selbst PCIe 4.0 heute schon sinnvoll ist, aber wenn man "ein paar Jahre" in die Zukunft schaut, so wird eine schnelle Schnittstelle umso sinnvoller je mehr Jahre es sind und dies gilt dann aber auch genauso für PCIe 5.0. Wenn heute PCIe 2.0 schon eindeutlich zu langsam ist, so ist es PCIe 1.x erst recht. Aber PCIe 3.0 von der CPU ist im April 2012 mit Ivy Bridge erschienen und damit vor mehr als 9 Jahren, PCIe 4.0 vor nicht ganz zwei Jahren mit Zen2 außer wenn man eine Graka mit zu wenig RAM hat oder sich an den Benchmarkwerten seiner SSD erfreut, selbst wenn sie im Alltag keinen spürbaren Vorteil bringt, hat man bisher keinen echten Vorteil davon.PCIE 5.0 ist für den Consumerbereich einfach oversized. 4.0 ist für den Anfang schon sinnvoller und hält dannein paar Jahre.

Viele wollen immer Zukunftssicherheit, ohne zu betrachen ab wann der Vorteil für den sie da viel Geld bezahlt haben, innerhalb der Nutzungsdauer des Systems überhaupt relevant wird.

PCIe4.0 bringt ggü. PCIe3.0 im Consumer-Bereich aktuell lediglich zwei Vorteile:

- schnellere NMVe-SSDs

- etwas mehr FPS bei kleinen GPUs mit wenig VRAM (á la RX5500 4GB)

Ansonsten ist selbst PCIe3.0 noch immer ausreichend schnell.

Bereits PCIe4.0 hat den Nachteil, dass es Platinen deutlich verteuert, weil die Leitungsqualität erhöht werden muss. Bei PCIe5.0 wird das nicht anders sein.

Ob und in welchem Umfang die Platinen für AlderLake tatsächlich PCIe5.0 unterstützen, bleibt abzuwarten. Wenn eine H610-Platine dann plötzlich fast 90€ kostet, kauft die ja keiner mehr. Die H510-Platinen liegen jetzt schon über 70€. Intels Einstieg lag früher bei 50€ (H310) und stieg mit dem H410 schon auf über 60€ an. So billig kann Intel seine CPUs gar nicht verramschen, als dass man da zugreifen möchte. Siehe Verkaufszahlen der Intel-CPUs bei MF.

AMDs A520 macht es vor: 50€ als Einstieg in die aktuellste AMD-CPU-Plattform. So habe ich die Wahl, wo ich preislich einsteigen möchte.

- schnellere NMVe-SSDs

- etwas mehr FPS bei kleinen GPUs mit wenig VRAM (á la RX5500 4GB)

Ansonsten ist selbst PCIe3.0 noch immer ausreichend schnell.

Bereits PCIe4.0 hat den Nachteil, dass es Platinen deutlich verteuert, weil die Leitungsqualität erhöht werden muss. Bei PCIe5.0 wird das nicht anders sein.

Ob und in welchem Umfang die Platinen für AlderLake tatsächlich PCIe5.0 unterstützen, bleibt abzuwarten. Wenn eine H610-Platine dann plötzlich fast 90€ kostet, kauft die ja keiner mehr. Die H510-Platinen liegen jetzt schon über 70€. Intels Einstieg lag früher bei 50€ (H310) und stieg mit dem H410 schon auf über 60€ an. So billig kann Intel seine CPUs gar nicht verramschen, als dass man da zugreifen möchte. Siehe Verkaufszahlen der Intel-CPUs bei MF.

AMDs A520 macht es vor: 50€ als Einstieg in die aktuellste AMD-CPU-Plattform. So habe ich die Wahl, wo ich preislich einsteigen möchte.

Case39

Experte

- Mitglied seit

- 22.04.2016

- Beiträge

- 1.254

Moin,

bin nicht ganz sicher, für den Fall das es schon gepostet wurde Sorry.

aber die Pins an der CPU sind bei AMD dann wohl mit AM5 Geschichte:

AMD next-gen AM5 platform to feature LGA1718 socket - VideoCardz.com

AMD AM5 platform detailed ExecutableFix has revealed the first details on the upcoming next-gen AMD socket. AMD AM5, the successor to AM4 is to feature an LGA1718 socket. AMD is apparently changing its socket type from PGA to LGA (land grid array), which means there be no pins on the next-gen...videocardz.com

Also keine am Kühlerboden klebende aus dem Sockel gerissene PGA-CPUs mehr!

Ich bin enttäuscht.

Ist es denn so schwer, den Kühler vor dem abnehmen etwas zu drehen?

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 289