en.wikipedia.org

Haben CPUs quasi schon immer.

Woher sollte Software wissen, wohin die Anfragen gehen sollen?

Wenn Software das wirklich so machen würde, wie Du es beschreibst / meinst, könnte man mit Software wie im Film die Hardware grillen.

Natürlich ist da nur eine API und was dahinter passiert ist ne Blackbox für das OS und läuft über die CU der CPU.

Was genau da nun Windows machen soll hab ich noch nicht ganz verstanden, weil alle Erklärungen dazu auf einer falschen Annahme beruhen. Nämlich, dass Windows die Aufgaben an die CPU Kerne verteilt.

Dem ist nicht so,... Windows kann bestenfalls der CPU sagen: "Hier ist ne Aufgabe, die eher eine starke CPU braucht!" oder "hier ist ne Aufgabe, die eher mehr Cache braucht!".

Die CU bekommt diese Info dann durch die API und kann das dann entweder befolgen, oder es komplett ignorieren,...

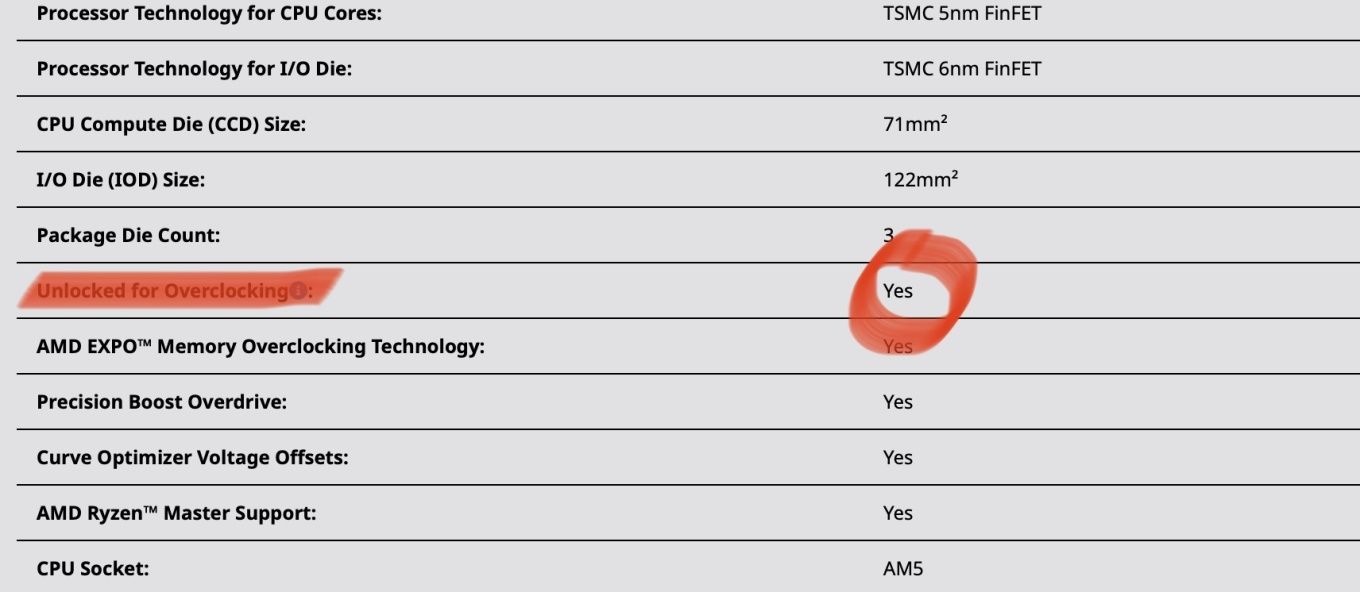

.. in der Realität wird das vermutlich so laufen, dass Windows sagt: "Need Cache Cores!" - die CU dann die Aufgabe für ein paar Nanosekunden splittet und checked, wo es wirklich schneller geht... und dann die volle Workload dahin umschichtet. Egal, was Windows sagt.

Natürlich wäre es toll, wenn Windows immer direkt richtig liegt. Das erspart paar Nanosekunden, was bei CPU Lasten durchaus spürbar ist. Aber es wird mitnichten so sein, dass die CPU hilflos ist ohne Windows.

Es wird immer Defaults geben und die CU wird immer recht gut wissen, was da verbaut ist und was sie damit tun kann.

Na, dann mache ich das eben.