RAMMon v3.3 Build: 1000 built with SysInfo v3.0 Build: 2001

PassMark (R) Software

www.passmark.com

============================

Memory settings

============================

Transfer rate: N/A - See help file for details

Memory timings: N/A - See help file for details

Channel mode: N/A - See help file for details

============================

Memory capacity / benchmarks

============================

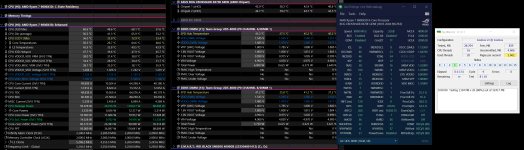

L1 cache: 80 KB (552.0 GB/s)

L2 cache: 1024 KB (135.4 GB/s)

L3 cache: 98304 KB (11.4 GB/s)

Physical RAM: 31.7 GB (3855 MB/s)

Latency: 217.477 ns

============================

Memory SPD information

============================

Item | Slot #1 | Slot #2 |

---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-

Ram Type | DDR5 | DDR5 |

Maximum Clock Speed (MHz) | 4000 (XMP) | 4000 (XMP) |

Maximum Transfer Speed (MT/s) | DDR5-8000 | DDR5-8000 |

Maximum Bandwidth (MB/s) | PC5-32000 | PC5-32000 |

Memory Capacity (MB) | 16384 | 16384 |

DIMM Temperature | N/A | N/A |

Jedec Manufacture Name | Team Group Inc. | Team Group Inc. |

Search Amazon.com | Search! | Search! |

SPD Revision | 1.0 | 1.0 |

Registered | No | No |

ECC | No | No |

On-Die ECC | Yes | Yes |

DIMM Slot # | 1 | 2 |

Manufactured | Week 49 of Year 2024 | Week 49 of Year 2024 |

Module Part # | UD5-8000 | UD5-8000 |

Module Revision | 0x0 | 0x0 |

Module Serial # | 0202B999 (04ef0024490202b999) | 0202B99A (04ef0024490202b99a) |

Module Manufacturing Location | 0 | 0 |

# of Row Addressing Bits | 16 | 16 |

# of Column Addressing Bits | 10 | 10 |

# of Banks | 32 | 32 |

# of Ranks | 1 | 1 |

Device Width in Bits | 8 | 8 |

Bus Width in Bits | 32 | 32 |

Module Voltage | 1.1V | 1.1V |

CAS Latencies Supported | 22 28 30 32 36 40 42 46 50 | 22 28 30 32 36 40 42 46 50 |

Timings @ Max Frequency (JEDEC) | 46-46-46-90 | 46-46-46-90 |

Maximum frequency (MHz) | 2800 | 2800 |

Maximum Transfer Speed (MT/s) | DDR5-5600 | DDR5-5600 |

Maximum Bandwidth (MB/s) | PC5-22400 | PC5-22400 |

Minimum Clock Cycle Time, tCK (ns) | 0.357 | 0.357 |

Minimum CAS Latency Time, tAA (ns) | 16.428 | 16.428 |

Minimum RAS to CAS Delay, tRCD (ns) | 16.428 | 16.428 |

Minimum Row Precharge Time, tRP (ns) | 16.428 | 16.428 |

Minimum Active to Precharge Time, tRAS (ns) | 32.000 | 32.000 |

Minimum Row Active to Row Active Delay, tRRD (ns) | 0.000 | 0.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Time, tRC (ns) | 48.428 | 48.428 |

Minimum Auto-Refresh to Active/Auto-Refresh Command Period, tRFC (ns) | 295.000 | 295.000 |

| | |

DDR5 Specific SPD Attributes | | |

Maximum Clock Cycle Time, tCKmax (ns) | 1.010 | 1.010 |

Write Recovery time (ns) | 30.000 | 30.000 |

Minimum Auto-Refresh to Active/Auto Refresh Command Period, tRFC2 (ns) | 160.000 | 160.000 |

Minimum Auto-Refresh to Active/Auto Refresh Command Period, tRFC4 (ns) | 130.000 | 130.000 |

Minimum Refresh Recovery Delay Time, tRFC1 (ns) | 0.000 | 0.000 |

Minimum Refresh Recovery Delay Time, tRFC2 (ns) | 0.000 | 0.000 |

Minimum Refresh Recovery Delay Time, tRFCsb (ns) | 0.000 | 0.000 |

Module Type | UDIMM | UDIMM |

Module information SPD revision | 1.0 | 1.0 |

SPD present | Yes | Yes |

SPD device type | SPD5118 | SPD5118 |

SPD Manufacturer | Montage Technology Group (Bank: 7, ID: 0x32) | Montage Technology Group (Bank: 7, ID: 0x32) |

PMIC 0 present | Yes | Yes |

PMIC 0 device type | PMIC5100 | PMIC5100 |

PMIC 0 Manufacturer | Richtek Power (Bank: 11, ID: 0x8C) | Richtek Power (Bank: 11, ID: 0x8C) |

PMIC 1 present | No | No |

PMIC 1 device type | | |

PMIC 1 Manufacturer | | |

PMIC 2 present | No | No |

PMIC 2 device type | | |

PMIC 2 Manufacturer | | |

Thermal Sensor 0 present | No | No |

Thermal Sensor 1 present | No | No |

Thermal Sensor device type | | |

Thermal Sensor Manufacturer | | |

Module Height (mm) | 32 | 32 |

Module Thickness Front (mm) | 2 | 2 |

Module Thickness Back (mm) | 1 | 1 |

Module Reference Card | Raw Card A Rev. 0 | Raw Card A Rev. 0 |

# DRAM Rows | 1 | 1 |

Heat spreader installed | No | No |

Operating Temperature Range | XT (0 to + 95 °C) | XT (0 to + 95 °C) |

Rank Mix | Symmetrical | Symmetrical |

Number of Package Ranks per Channel | 1 | 1 |

Number of Channels per DIMM | 2 | 2 |

Primary bus width per Channel | 32 bits | 32 bits |

Bus width extension per Channel | 0 bits | 0 bits |

DRAM Manufacture ID | 173 | 173 |

DRAM Manufacture Bank | 1 | 1 |

DRAM Manufacture Name | SK Hynix | SK Hynix |

DRAM Stepping | 15.15 | 15.15 |

SDRAM Package Type | Monolithic SDRAM | Monolithic SDRAM |

SDRAM Density Per Die | 16Gb | 16Gb |

SDRAM Bank Groups | 8 | 8 |

SDRAM Banks Per Bank Group | 4 | 4 |

Second SDRAM Package Type | | |

Second SDRAM Density Per Die | | |

Second SDRAM Column Address Bits | | |

Second SDRAM Row Address Bits | | |

Second SDRAM Device Width | | |

Second SDRAM Bank Groups | | |

Second SDRAM Banks Per Bank Group | | |

First SDRAM RFM RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) |

First SDRAM RFM RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) |

First SDRAM RFM Required | no | no |

First SDRAM RFM RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 |

Second SDRAM RFM RAAMMT | | |

Second SDRAM RFM RAAIMT | | |

Second SDRAM RFM Required | | |

Second SDRAM RFM RAA Counter Decrement per REF command | | |

First SDRAM ARFM Level A RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) |

First SDRAM ARFM Level A RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) |

First SDRAM ARFM Level A supported | no | no |

First SDRAM ARFM Level A RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 |

Second SDRAM ARFM Level A RAAMMT | | |

Second SDRAM ARFM Level A RAAIMT | | |

Second SDRAM ARFM Level A supported | | |

Second SDRAM ARFM Level A RAA Counter Decrement per REF command | | |

First SDRAM ARFM Level B RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) |

First SDRAM ARFM Level B RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) |

First SDRAM ARFM Level B supported | no | no |

First SDRAM ARFM Level B RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 |

Second SDRAM ARFM Level B RAAMMT | | |

Second SDRAM ARFM Level B RAAIMT | | |

Second SDRAM ARFM Level B supported | | |

Second SDRAM ARFM Level B RAA Counter Decrement per REF command | | |

First SDRAM ARFM Level C RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) |

First SDRAM ARFM Level C RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) |

First SDRAM ARFM Level C supported | no | no |

First SDRAM ARFM Level C RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 |

Second SDRAM ARFM Level C RAAMMT | | |

Second SDRAM ARFM Level C RAAIMT | | |

Second SDRAM ARFM Level C supported | | |

Second SDRAM ARFM Level C RAA Counter Decrement per REF command | | |

sPPR Granularity | bank group | bank group |

sPPR Undo/Lock | supported | supported |

Burst length 32 | not supported | not supported |

MBIST/mPPR | not supported | not supported |

mPPR/hPPR Abort | not supported | not supported |

PASR | not supported | not supported |

DCA Types Supported | Device supports DCA for 4-phase internal clock(s) | Device supports DCA for 4-phase internal clock(s) |

x4 RMW/ECS Writeback Suppression | not supported | not supported |

x4 RMW/ECS Writeback Suppression MR selector | MR9 | MR9 |

Bounded Fault | not supported | not supported |

SDRAM Nominal Voltage, VDDQ | 1.1V | 1.1V |

SDRAM Nominal Voltage, VPP | 1.8V | 1.8V |

Cyclical Redundancy Code (CRC) for Base Configuration | 9d1a | 9d1a |

| | |

XMP Attributes | | |

XMP version | 3.0 | 3.0 |

PMIC Vendor ID | 8A8C | 8A8C |

Number of PMICs on DIMM | 1 | 1 |

PMIC capabilities | | |

PMIC has capabilities for OC functions | Yes | Yes |

Current PMIC OC is enabled | Yes | Yes |

PMIC voltage default step size | 5mV | 5mV |

OC global reset functions | No | No |

Validation and Certification Capabilities | | |

DIMM is self-certified by DIMM vendor | No | No |

PMIC Component is validated by Intel AVL level | No | No |

XMP revision | 1.2 | 1.2 |

XMP Profile 1 | | |

Profile name | TG-8000-38-48-84 | TG-8000-38-48-84 |

XMP Certified | No | No |

Recommended number of DIMMs per channel | 1 | 1 |

Module VPP voltage | 1.80V | 1.80V |

Module VDD voltage | 1.45V | 1.45V |

Module VDDQ voltage | 1.45V | 1.45V |

Memory Controller voltage | 1.10V | 1.10V |

Clock speed (MHz) | 4000 | 4000 |

Transfer Speed (MT/s) | DDR5-8000 | DDR5-8000 |

Bandwidth (MB/s) | PC5-32000 | PC5-32000 |

Minimum clock cycle time, tCK (ns) | 0.250 | 0.250 |

Supported CAS latencies | 38 | 38 |

Minimum CAS latency time, tAA (ns) | 9.500 | 9.500 |

Minimum RAS to CAS delay time, tRCD (ns) | 12.000 | 12.000 |

Minimum row precharge time, tRP (ns) | 12.000 | 12.000 |

Minimum active to precharge time, tRAS (ns) | 21.000 | 21.000 |

Supported timing at highest clock speed | 38-48-48-84 | 38-48-48-84 |

Minimum Active to Auto-Refresh Delay, tRC (ns) | 33.000 | 33.000 |

Minimum Write Recovery Time, tWR (ns) | 30.000 | 30.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) | 295.000 | 295.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) | 160.000 | 160.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) | 130.000 | 130.000 |

Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Read Command Delay Time, Same Bank Group, tCCD_L_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Read Command Delay Time, Different Bank Group, tCCD_S_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Read to Precharge Command Delay Time, tRTP (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Four Activate Window, tFAW (ns) | 0.000 | 0.000 |

Advanced Memory Overclocking Features | | |

Real-Time Memory Frequency Overclocking | Not supported | Not supported |

Intel Dynamic Memory Boost | Not supported | Not supported |

System CMD Rate Mode | 2N | 2N |

Vendor Personality Byte | 0x00 | 0x00 |

XMP Profile 2 | | |

Profile name | TG-6000-38-38-78 | TG-6000-38-38-78 |

XMP Certified | No | No |

Recommended number of DIMMs per channel | 1 | 1 |

Module VPP voltage | 1.80V | 1.80V |

Module VDD voltage | 1.25V | 1.25V |

Module VDDQ voltage | 1.25V | 1.25V |

Memory Controller voltage | 1.10V | 1.10V |

Clock speed (MHz) | 3000 | 3000 |

Transfer Speed (MT/s) | DDR5-6000 | DDR5-6000 |

Bandwidth (MB/s) | PC5-24000 | PC5-24000 |

Minimum clock cycle time, tCK (ns) | 0.333 | 0.333 |

Supported CAS latencies | 38 | 38 |

Minimum CAS latency time, tAA (ns) | 12.654 | 12.654 |

Minimum RAS to CAS delay time, tRCD (ns) | 12.654 | 12.654 |

Minimum row precharge time, tRP (ns) | 12.654 | 12.654 |

Minimum active to precharge time, tRAS (ns) | 25.974 | 25.974 |

Supported timing at highest clock speed | 38-38-38-78 | 38-38-38-78 |

Minimum Active to Auto-Refresh Delay, tRC (ns) | 38.628 | 38.628 |

Minimum Write Recovery Time, tWR (ns) | 30.000 | 30.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) | 295.000 | 295.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) | 160.000 | 160.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) | 130.000 | 130.000 |

Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Read Command Delay Time, Same Bank Group, tCCD_L_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Write to Read Command Delay Time, Different Bank Group, tCCD_S_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Read to Precharge Command Delay Time, tRTP (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) |

Minimum Four Activate Window, tFAW (ns) | 0.000 | 0.000 |

Advanced Memory Overclocking Features | | |

Real-Time Memory Frequency Overclocking | Not supported | Not supported |

Intel Dynamic Memory Boost | Not supported | Not supported |

System CMD Rate Mode | 2N | 2N |

Vendor Personality Byte | 0x00 | 0x00 |

| | |

EXPO Attributes | | |

EXPO version | 1.0 | 1.0 |

PMIC feature support | | |

PMIC 10 mV step size support | No | No |

EXPO Profile 1 | | |

DIMMs per channel supported | 1 | 1 |

EXPO Optional Block Support | | |

Block 1 enabled | Yes | Yes |

SDRAM VDD | 1.45V | 1.45V |

SDRAM VDDQ | 1.45V | 1.45V |

SDRAM VPP | 1.80V | 1.80V |

Clock speed (MHz) | 4000 | 4000 |

Transfer Speed (MT/s) | DDR5-8000 | DDR5-8000 |

Bandwidth (MB/s) | PC5-32000 | PC5-32000 |

Minimum clock cycle time, tCK (ns) | 0.250 | 0.250 |

Minimum CAS latency time, tAA (ns) | 9.500 | 9.500 |

Minimum RAS to CAS delay time, tRCD (ns) | 12.000 | 12.000 |

Minimum row precharge time, tRP (ns) | 12.000 | 12.000 |

Minimum active to precharge time, tRAS (ns) | 21.000 | 21.000 |

Supported timing at highest clock speed | 38-48-48-84 | 38-48-48-84 |

Minimum Active to Auto-Refresh Delay, tRC (ns) | 33.000 | 33.000 |

Minimum Write Recovery Time, tWR (ns) | 30.000 | 30.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) | 295.000 | 295.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) | 160.000 | 160.000 |

Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) | 130.000 | 130.000 |

Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) | 5.000 | 5.000 |

Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) | 5.000 | 5.000 |

Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) | 20.000 | 20.000 |

Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) | 10.000 | 10.000 |

Minimum Four Activate Window, tFAW (ns) | 8.000 | 8.000 |

Minimum Write to Read Command Delay Time, Same Bank Group, tWTR_L (ns) | 10.000 | 10.000 |

Minimum Write to Read Command Delay Time, Different Bank Group, tWTR_S (ns) | 2.500 | 2.500 |

Minimum Read to Precharge Command Delay Time, tRTP (ns) | 7.500 | 7.500 |