Werbung

High Bandwidth Memory soll der Heilsbringer der GPU-Hersteller werden und gleich mehrere Probleme lösen, die sich im Zusammenhang mit der Anbindung und der Leistung von Grafikspeicher in letzten Jahren aufgebaut haben. Höhere Speicherbandbreite, mehr Speicherkapazität, geringere Leistungsaufnahme und geringerer Platzbedarf sind die wichtigsten Vorteile von HBM, die wir teilweise bereits beleuchtet haben, die AMD nun aber noch einmal genauer erklären möchte.

Bereits mehrfach haben wir uns mit dem Thema HBM beschäftigt. Schon im Sommer letzten Jahres sprach SK Hynix erstmals über HBM und kündigte in der Folge im November die baldige Massenproduktion des neuen Speichers an. Auf der GPU Technology Conference von NVIDIA stellte SK Hynix aus und präsentierte weitere technische Details. Eigentlich aber wurde HBM in technischer Hinsicht bereits im vergangenen Jahr umrissen, sowohl von AMD, wie auch von NVIDIA und SK Hynix selbst. Aus den bisher verfügbaren Informationen haben wir einen umfangreichen Artikel erstellt, der die Vorteile von HBM genauer erläutert und auch klärt, warum HBM mehr als nur eine Erhöhung der Speicherbandbreite ist. Nun spricht auch AMD wieder einmal offiziell über HBM und nennt seine Gründe für den baldigen Wechsel der Speichertechnologie für den Grafikspeicher.

Gleich mehrere Gründe sorgen dafür, dass GDDR5 bald an seine Grenzen kommen wird bzw. schon an diesen arbeitet. Sowohl Samsung wie auch SK Hynix bieten GDDR5-Speicher aktuell mit maximalen Taktraten von 2.000 MHz an. Diese sind in Kapazitäten von 4, 6 und 8 GBit pro Chip verfügbar, was 512, 768 und 1.024 MByte entspricht. Allerdings muss aufgrund des hohen Taktes auch eine Spannung von 1,35 bis 1,5 V angelegt werden und auch bei der Fertigung kommen die Hersteller an ihre Grenzen. Ändert sich an einigen Ausgangsparametern für GDDR5 nichts, erreicht dieser in Kürze einen Stand, an dem er nicht mehr effektiv eingesetzt werden kann. Die Balance aus Leistung der GPU und dem Potenzial, welches aus dem Grafikspeicher heraus zur Verfügung steht, gerät aus dem Gleichgewicht.

Eine Limitierung durch die Speicherbandbreite kann derzeit weder AMD mit den "Hawaii"-GPUs noch NVIDIA mit dem großen "Maxwell" alias GM200 nachgesagt werden. Allerdings gehen beide Hersteller inzwischen auch unterschiedliche Wege, um eine eventuelle Limitierung zu umgehen. Bei AMD hat man sich für ein äußerst komplexes Speicherinterface auf "Hawaii" entschieden, dass mit 512 Bit größer als bei allen anderen GPUs ist. NVIDIA hingegen hat von 384 auf 256 Bit den Rückwärtsgang eingelegt, implementiert aber auch eine Speicherkomprimierung, um dies etwas auszugleichen.

AMD: High Bandwidth Memory (HBM)

Es ist nicht nur die Speicherbandbreite, die zum Wechsel von GDDR5 auf HBM animiert, dies macht AMD klar, in dem man einen Größenvergleich präsentiert. Um eine möglichst hohe Bandbreite zu erreichen, werden möglichst viele Speicherchips gleichzeitig angesprochen. Die Stromversorgung des Speichers ist neben dem Platzbedarf der eigentlichen Speicherchips inzwischen auch ein ausschlaggebendes Argument. Um eine möglichst gleichmäßige Signallaufzeit zu den Speicherchips zu haben, platzieren die Hersteller die Chips gleichmäßig um die GPU – auch dies ist aus verschiedenen Aspekten nicht ideal.

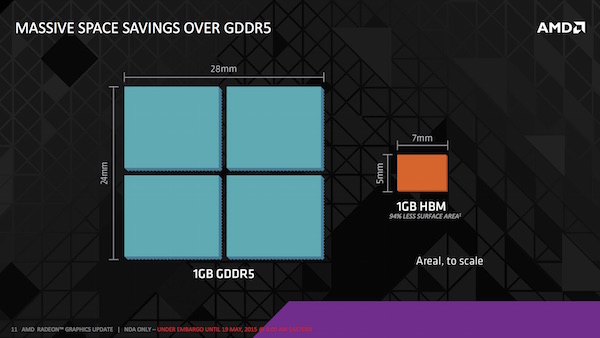

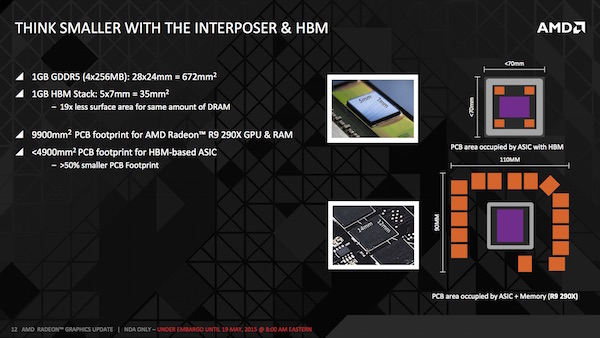

Vergleicht man jedoch die konkreten Zahlen für den Platzbedarf, wird dieser Aspekt besonders deutlich. 1 GB an Speicherkapazität bestehend aus GDDR5-Speicher misst 24 x 28 mm, also 672 mm2. Durch das Stapeln von bis zu vier Ebenen belegen 1 GB HBM nur 5 x 7 mm, also 35 mm2. Dies entspricht einer Platzeinsparung von 94 %.

Noch deutlicher werden die Verhältnisse aber, wenn man moderne High-End-GPUs mit 4, 8 oder gar 12 GB an Speicher bestückt. So kommt eine Radeon R9 290X mit ihren 4 GB GDDR5-Speicher auf 9.900 mm2 Fläche auf dem PCB. Die gleiche GPU auf einem Interposer zusammen mit HBM kommt auf weniger als 4.900 mm2. Die Rechenbeispiele aus dem obigen Fall lassen sich also nicht ohne die technischen Voraussetzungen von HBM durch das Trägermaterial vergleichen, dennoch sprechen wir von einer Einsparung von 50 %.

AMD: High Bandwidth Memory (HBM)

Laut AMD eignet sich DRAM bzw. GDDR auch nicht für eine Integration auf einer Logikeinheit – auch wenn andere Hersteller dies in gewisser Weise genau so machen. So packt Intel DRAM zusammen mit der CPU oder SoC in ein Package. So zum Beispiel beim eDRAM der "Crystalwell"-GPU alias Iris Pro Graphics. Ein ähnliches Verfahren kommt auch bei den APUs in der Xbox 360 und der Nintendo Wii U zum Einsatz.

Auf die Beschränkungen der zukünftigen Entwicklung von GDDR5 durch den immer höheren Bedarf an Spannung und damit eine immer höhere Leistungsaufnahme sind wir bereits eingegangen. GDDR5 bewegt sich aktuell in einem noch machbaren Bereich, doch die Grenzen des möglichen oder besser gesagt sinnvollen sind erreicht.

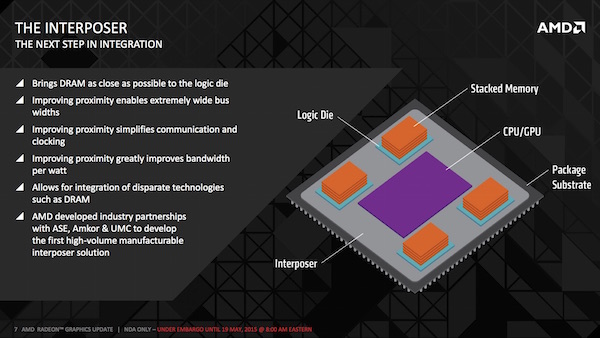

Allerdings gelingt die Integration von HBM nicht einfach so und bedarf einiger technischer Kniffe. Dazu gehört auch der Interposer, der als Träger für CPU/GPU und HBM dient. Der Interposer dient dabei als Schnittstelle zwischen den verschiedenen Chips sowie einem notwendigen Interface zwischen diesen und dem PCB. Viele Chips mit Ball Grid Array (BGA) verwenden einen Interposer. Der Pentium II von Intel ist eines der frühesten Beispiele und einige mehr sind in der Zwischenzeit dazu gekommen.

Die räumliche Nähe von HBM zur GPU auf dem Interposer ist eine Voraussetzung für ein breites Speicherinterface. Die Verdrahtung erfolgt nicht mehr über Leiterbahnen auf dem PCB, sondern direkt durch den Interposer. Auch wird das Ansprechen des Speichers über das Speicherinterface damit einfacher, da die Timings nicht mehr derart exakt abgestimmt werden müssen. Hier bietet HBM ohnehin eine größere Flexibilität, wie wir in einem weiteren Artikel bereits erläuterten.

Allerdings musste sich AMD bei der Fertigung auch neue Partner suchen, um die eigenen GPUs zusammen mit HBM auf einem Interposer unterbringen zu können. Diese hat man mit ASE, Amkor und UMC gefunden.

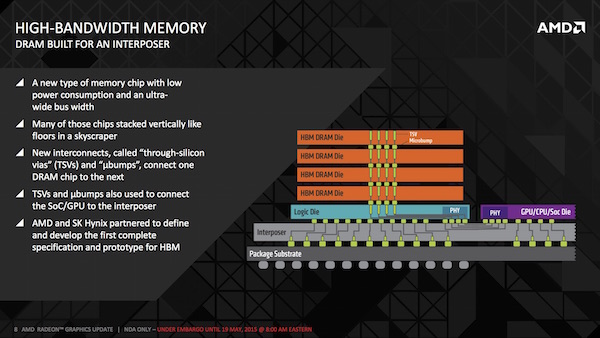

Wie genau der Aufbau von HBM auf dem Interposer zusammen mit einer GPU aussieht, zeigt AMD ebenfalls. In diesem Beispiel ist ein HBM mit vier Schichten zu sehen, die mittels TSVs (Through Silicon Vias) miteinander verbunden sind. Zur direkten Verbindung ebenfalls zum Einsatz kommen sogenannte µBumps, die auch dazu verwendet werden die Abwärme aus den dazwischenliegenden Schichten abzuführen. Auch dazu haben wir bereits vor einigen Tagen einige Details veröffentlicht.

Die physikalische Schnittstelle zwischen Speicher und GPU befindet sich direkt unterhalb des Speichers. Auch hier werden die Verbindungen zu den Speicherstacks wie TSVs realisiert. Durch den Interposer laufen wiederum die Verbindungen zum Package-Substrat, auf dem die komplette Konstruktion sitzt und das wiederum beispielsweise über ein BGA die Verbindung zum PCB herstellt. Über diese Verbindungen wird auch die Stromversorgung von HBM und GPU erfolgen.

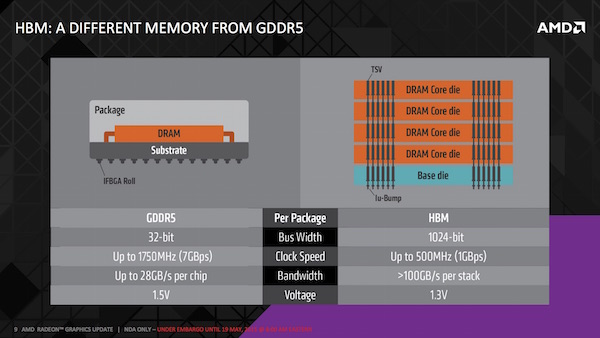

Noch einmal ein direkter Vergleich der technischen Daten von DRAM und HBM: Während GDDR5 pro Chip auf eine Breite des Speicherinterfaces von 32 Bit kommt, sind es bei HBM 1.024 Bit. Bei Taktraten von gerade einmal 500 MHz (effektiv 1.000 MHz) für HBM erreicht AMD so eine Speicherbandbreite von mehr als 100 GB/s pro Stack. Bei vier Stacks kommen wir so auf 512 GB/s für einen HBM-Chip. GDDR5 kommt aktuell bei 1.750 MHz auf 28 GB/s pro Chip. Die Spannung von GDDR5 liegt bei 1,5 V, während HBM mit 1,3 V auskommt.

An dieser Stelle kommen wir auch gleich zu einem Detail der ersten HBM-Implementation seitens AMD, das bisher noch weitestgehend unbekannt war. Während aufgrund der bisher verfügbaren Informationen davon ausgegangen wurde, dass AMD seine ersten Karten mit HBM mit 4 und/oder 8 GB Speicherkapazität ausliefern wird, sieht es nun so aus, als würden zunächst einmal nur 4 GB verbaut werden können. Grund hierfür ist die Planung seitens AMD in den ersten Varianten vier HBM-Chips zu verbauen. Bei vier Stacks je HBM-Chip, die so von AMD bestätigt wurden, kommen wir auf maximale 4 GB Grafikspeicher in der ersten Version.

AMD spricht allerdings auch davon, dass die Speicherkapazität nur eine der aktuellen Limitierungen ist. Man müsse sich auch auf die bessere Nutzung dieses Speichers konzentrieren und habe dazu Mittel und Wege entwickelt. Vermutlich wird auch AMD eine Speicherkomprimierung einsetzen. GDDR5 verschenke hier laut AMD viel Potenzial, dass mit HBM wieder frei werde - damit seien auch 4 GB Grafikspeicher zunächst einmal wieder mehr als ausreichend. Ob dies auch den Tatsachen entspricht, werden wir spätestens zum Start der ersten GPUs mit HBM sehen.

Der genaue Wortlaut von AMDs CTO, Joe Macri lautete wie folgt:

"You're not limited in this world to any number of stacks, but from a capacity point of view, this generation-one HBM, each DRAM is a two-gigabit DRAM, so yeah, if you have four stacks you're limited to four gigabytes. You could build things with more stacks, you could build things with less stacks. Capacity of the frame buffer is just one of our concerns. There are many things you can do to utilise that capacity better. So if you have four stacks you're limited to four GB, but we don't really view that as a performance limitation from an AMD perspective.

If you actually look at frame buffers and how efficient they are and how efficient the drivers are at managing capacities across the resolutions, you'll find that there's a lot that can be done. We do not see 4 GB as a limitation that would cause performance bottlenecks. We just need to do a better job managing the capacities. We were getting free capacity, because with GDDR5 in order to get more bandwidth we needed to make the memory system wider, so the capacities were increasing. As engineers, we always focus on where the bottleneck is. If you're getting capacity, you don't put as much effort into better utilising that capacity. 4GB is more than sufficient. We've had to go do a little bit of investment in order to better utilise the frame buffer, but we're not really seeing a frame buffer capacity [problem]. You'll be blown away by how much capacity is wasted."

AMD: High Bandwidth Memory (HBM)

Zusammenfassender Überblick HBM

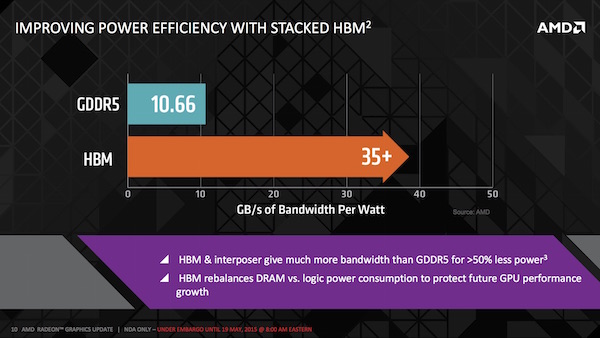

HBM ist mehr als die höhere Speicherbandbreite. HBM liefert natürlich das Potenzial die Speicherbandbreite bereits zum Start dramatisch zu erhöhen und dieser Trend wird sich mit den weiteren Ausbaustufen von HBM weiter fortsetzen. HBM bietet aber auch weitere Vorteile. Dazu gehören der geringere Platzbedarf, ein geringerer Verbrauch und damit verbunden eine weniger aufwendige Versorgung sowie größere Möglichkeiten für die Hersteller wie AMD und NVIDIA, den zur Verfügung stehenden Speicher besser zu nutzen. Der geringere Verbrauch bei gleichzeitig höherer Leistung sorgt natürlich auch für ein deutlich besseres Performance/Watt-Verhältnis. AMD misst hier in GB pro Sekunde/Watt und dieses Verhältnis ist für HBM dreimal höher als bei GDDR5

Noch immer sprechen wir hier aber von viel Theorie und können die Auswirkungen in der Praxis daher kaum abschätzen. Wird werden uns aber nicht mehr allzu lange gedulden müssen, bis wir Hand an Grafikkarten mit HBM legen dürfen. AMD wird eine baldige Veröffentlichung sowie eine Verfügbarkeit im Laufe des Junis nachgesagt. Zumindest aber konnte AMD noch einige weitere Aspekte im Zusammenhang mit HBM aufzeigen bzw. diese etwas tiefergreifend behandeln. Jetzt sind wir gespannt auf die Hardware-Umsetzungen!