Werbung

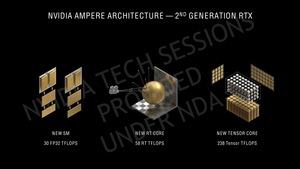

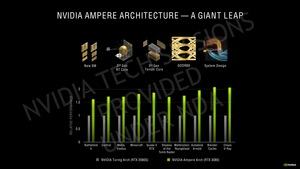

Beginnen wir mit der Basis einer jeden neuen GeForce-RTX-Karte - und das ist die GPU. Diese basiert auf der Ampere-Architektur, die sich wiederum von der Datacenter-Variante unterschiedet, wie sie in der GA100-GPU zum Einsatz kommt.

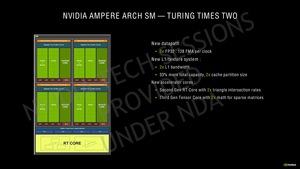

Der Ampere Streaming Multiprocessor (SM) verzichtet auf die FP64-Recheneinheiten, die in der GA100-GPU für den HPC-Einsatz noch wichtig sind, im Endkundenbereich aber keine Rolle spielen. Stattdessen hat man die Anzahl der FP32-Recheneinheiten verdoppelt. Statt 64 der FP32-Einheiten pro SM gibt es nun 128. Hinzu kommen 64 INT32-Einheiten. Es gibt nun zwei Datenpfade, die teilweise parallel angesprochen werden können. Einer der Datenpfade besteht aus 16 FP32-Einheiten. Hier können also 16 FP32-Berechnungen pro Takt bearbeitet werden. Ein zweiter Datenpfad besteht aus jeweils 16 FP32- und INT32-Einheiten. Jeder der SM-Quadranten kann entweder 32 FP32-Operationen ausführen oder jeweils 16 FP32- und INT32-Operationen pro Takt. Für den gesamten SM bedeutet dies die mögliche Ausführung von 128 FP32-Operationen oder jeweils 64 FP32- und INT32-Operationen pro Takt.

Um die nun doppelten FP32-Einheiten mit Daten versorgen zu können, hat NVIDIA den L1-Data-Cache von 96 kB auf 128 kB vergrößert. Die Datenrate zum L1-Cache wurde abermals verdoppelt. Diese Maßnahme hatte NVIDIA schon einmal von Pascal zur Turing vollzogen. Der Register bleibt mit 16.384 Einträgen zu jeweils 32 Bit identisch. Dies gilt auch für die Anzahl der Load- und Store-Einheiten.

Bei den speziellen Hardware-Einheiten wie den Tensor und RT Cores gibt es eine Änderung in deren Anzahl – zumindest bei den Tensor Cores, von denen nur noch vier pro SM (bei Turing sind es acht) vorhanden sind. Allerdings ist die dritte Generation der Tensor Cores schneller und effektiver. Dies gilt auch für die RT Cores, für die es bei einem RT Core pro SM bleibt.

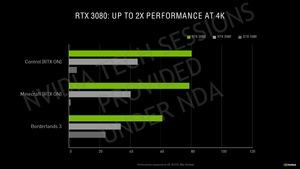

Die Verdopplung der FP32-Recheneinheiten ist sicherlich einer der Gründe, warum die GA10x-GPUs über bis zu 28 Milliarden Transistoren verfügen. Die TU102-GPU kommt auf 18,6 Milliarden Transistoren. Die Anzahl der Transistoren der GA104-GPU belaufen sich auf 17,4 Milliarden. Die GA102-GPU kommt bei der GeForce RTX 3090 und der GeForce RTX 3080 zum Einsatz. Die GA104-GPU wird für die GeForce RTX 3070 verwendet.

Dafür aber kennen wir die Größe der Chips. Die GA102-GPU kommt auf 628,4 mm², die GA104-GPU auf 392,5 mm². Durch die Fertigung in 8 nm und die Anzahl von 28 Milliarden Transistoren sprechen wir also von einer Transistordichte der GA102-GPU von 44,6 Millionen Transistoren pro Quadratmillimeter (44 MT/mm²). Für die GA104-GPU sind es 44,3 MT/mm².

| GA100 | GA102 | GA104 | TU102 | |

| Fertigung | 7 nm (TSMC) | 8 nm (Samsung) | 8 nm (Samsung) | 12 nm (TSMC) |

| Anzahl der Transistoren | 54 Milliarden | 28 Milliarden | 17,4 Milliarden | 18,6 Milliarden |

| Chipgröße | 826 mm² | 628,4 mm² | 392,5 mm² | 754 mm² |

| Transistordichte | 65,37 MT/mm² | 44,56 MT/mm² | 44,33 MT/mm² | 24,67 MT/mm² |

Die in 7 nm bei TSMC gefertigte GA100-GPU kommt auf eine Transistordichte von 65,37 MT/mm², die Transistoren sind also um 47 % enger gepackt. Im Vergleich zur Turing-Generation mit in 12 nm bei TSMC gefertigten GPUs sind die Ampere-Modelle also kleiner und dichter gepackt, Samsungs Fertigung in 8 nm kann mit den modernsten Fertigungsverfahren nicht mithalten – muss sie aber auch nicht.

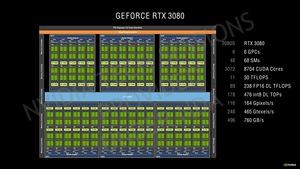

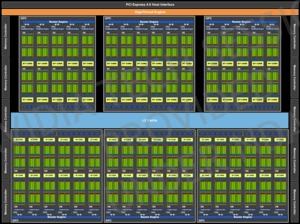

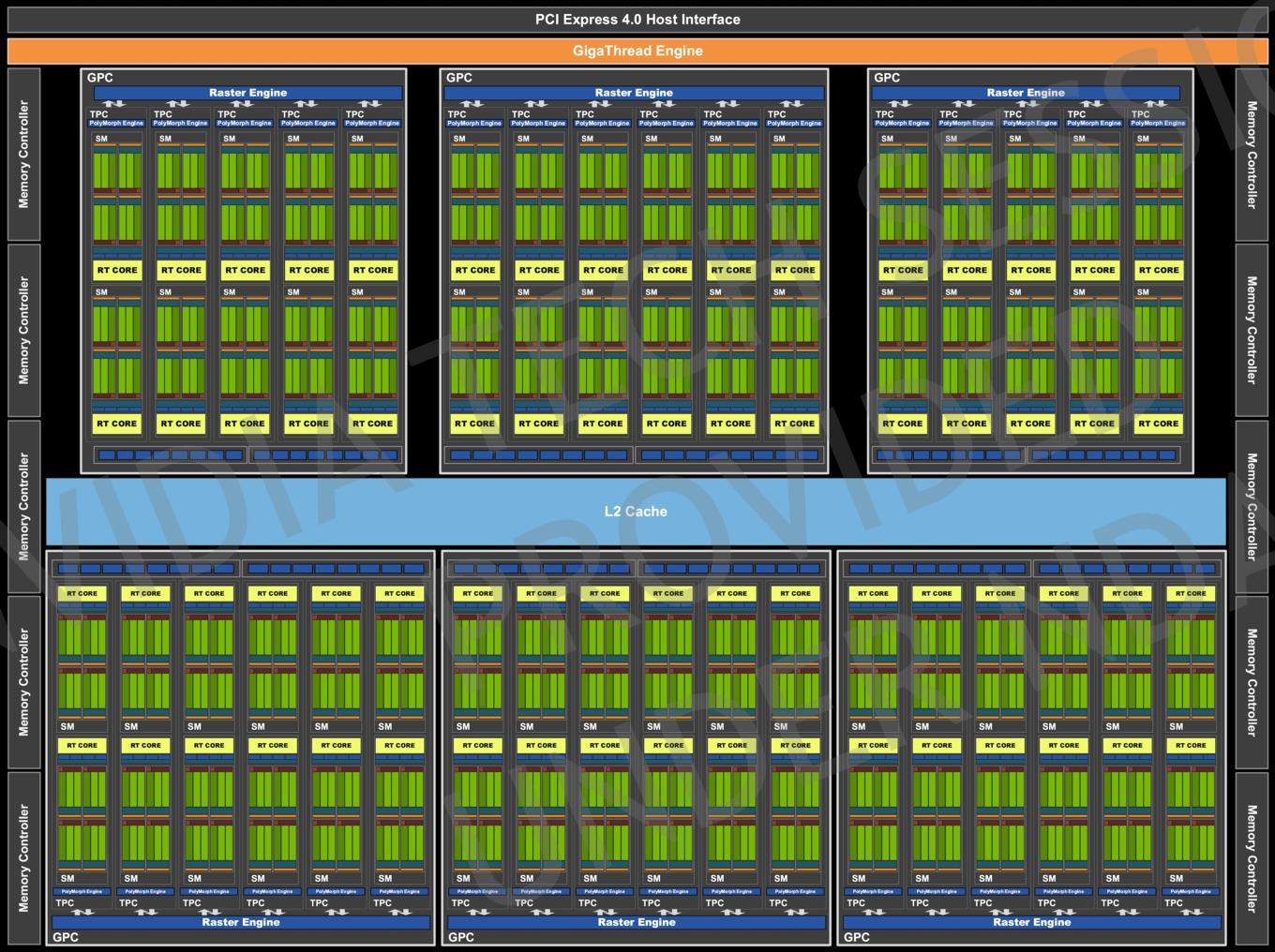

Aufbau der GA102-GPU

Die GA102-GPU besitzt sechs GPCs (Graphics Processing Clusters) und fünf oder sechs TPCs (Texture Processing Clusters) pro GPC. Pro TPC sind wiederum zwei SMs (Streaming Multiprocessor) vorhanden. Eine GA102-GPU der GeForce RTX 3080 verwendet 34 TPCs x 2 SMs also 8.704 CUDA-Kerne – 128 CUDA-Kerne pro SM. Die GA102-GPU für die GeForce RTX 3090 kommt auf 82 SMs und somit 10.496 Shadereinheiten

Pro SM sind zudem vier Tensor Cores und ein RT Core vorhanden. Zu diesen überarbeiteten Funktionseinheiten kommen wir gleich noch. Obiges Bild zeigt die GA102-GPU, wie sie auf der GeForce RTX 3080 zum Einsatz kommt. Daher sehen wir hier auch weniger TPCs und dementsprechend "nur" 68 SMs plus zehn Speichercontroller mit jeweils 32 Bit. Damit kommen wir auf die 320 Bit, die 10 GB an GDDR6X anbinden.

Für die GeForce RTX 3090 sind dann zwölf Speichercontroller vorhanden, um auf 384 Bit zu kommen. Zudem kommt die GA102-GPU hier dann mit 82 SMs und entsprechend mehr bzw. voll bestückten TPCs.

Entsprechend der Ausbaustufe gibt es unterschiedliche Größen des L2-Caches. Für die GeForce RTX 3080 beläuft sich dieser auf 5.120 kB, bei der GeForce RTX 3070 sind es 4.096 kB. Zum Vergleich: Die TU102-GPU brachte es auf 6.144 kB.

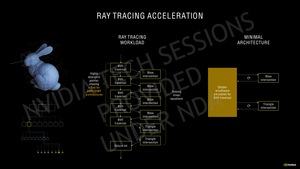

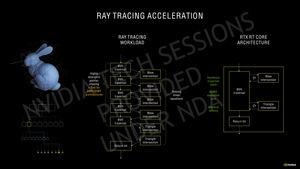

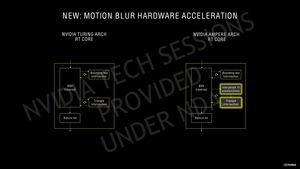

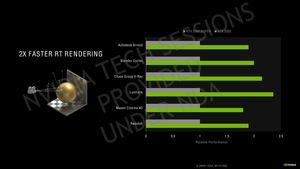

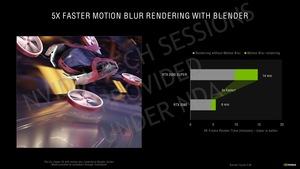

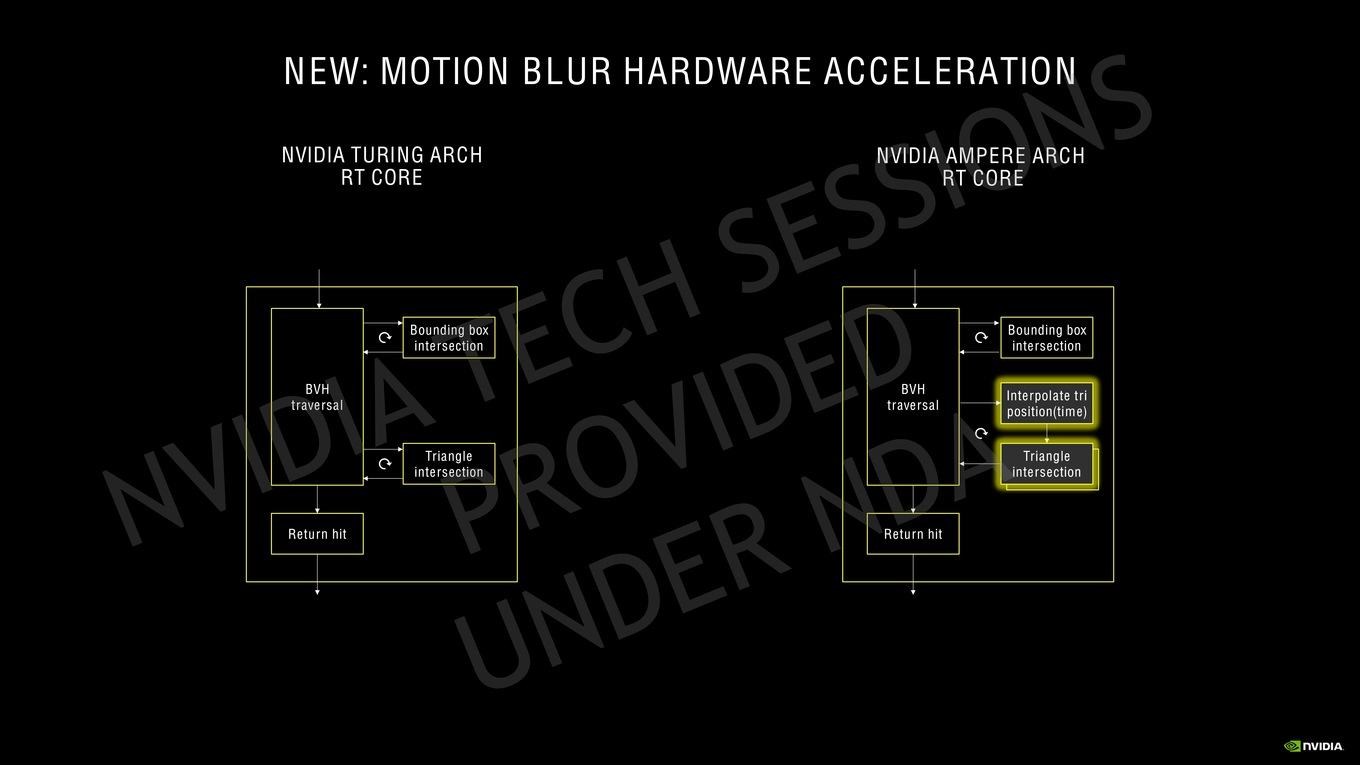

Zweite Generation der RT Cores

Die zweite Generation der RT Cores sollen doppelt so viele Intersection-Berechnungen durchführen können wie ihre Vorgänger. Da NVIDIA die Anzahl der RT Cores pro SM belässt, ergibt sich eine theoretische Skalierung der RT-Leistung um den Faktor zwei. Bei mehr SMs für die einzelnen Modelle ist die Leistung natürlich entsprechend höher.

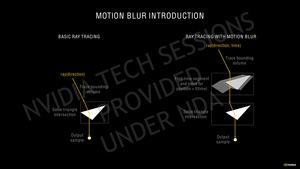

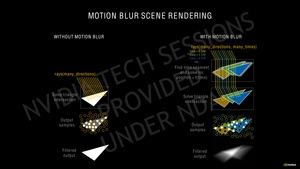

Eine Herausforderung in der Berechnung der Intersections ist ein Raytracing auf Objekte, die sich bewegen und auf die auch ein Motion Blur angewendet wird. Für Turing-GPUs bzw. deren RT Cores konnte dies zu einem Flaschenhals in der Raytracing-Leistung werden. Die zweite Generation der RT Cores bietet nun parallel arbeitende Einheiten, die eine bessere Annäherung durch Interpolation in Mution Blur Effekten ermöglicht. Über eine zeitabhängige Funktion werden die Intersections vorausberechnet und das Raytracing nur noch auf Bereiche angewendet, die auch wirklich notwendig sind.

Dritte Generation der Tensor Cores

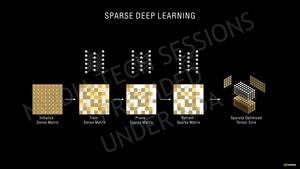

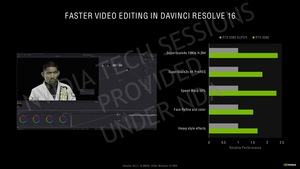

Erwartungsgemäß baut NVIDIA die Tensor Cores in der dritten Generation weiter aus und lässt diese neben INT16 und FP16 als Datensätze mit der bisher höchsten Genauigkeit nun auch FP32- und FP64-Berechnungen durchführen. Dies ist vor allem für die höheren Genauigkeiten im HPC-Segment wichtig. Für die GeForce-GPUs aber spielen geringere Genauigkeiten eine wesentlich wichtigere Rolle.

So können die Tensor Cores der Turing-Architektur 64 FP16 Fused Multiply–Add (FMA) pro Tensor Core durchführen. Für Ampere sind es in voll gepackten Matrizzen 128 für die GA102-GPU und sogar 256 für die GA100-GPU. Kommt die Sparsity/Sparse Matrix oder die dünnbesetzte/schwachbesetzte Matrix hinzu, sind es sogar 256 FP16 FMA für die GA102-GPU und 512 für die GA100-GPU. Die Tensor Cores der Turing-Architektur unterstützen keine Sparsity.

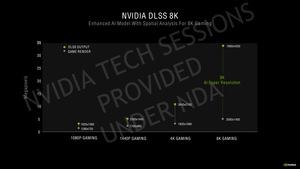

Damit erhöht sich die Tensor-Rechenleistung also mindestens um den Faktor zwei. Vor allem die DLSS-Leistung soll davon profitieren, aber theoretisch trifft dies auf alle Anwendungen zu, die AI-Berechnungen verwenden.

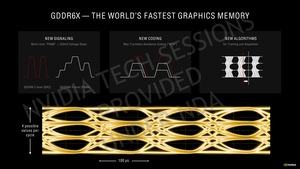

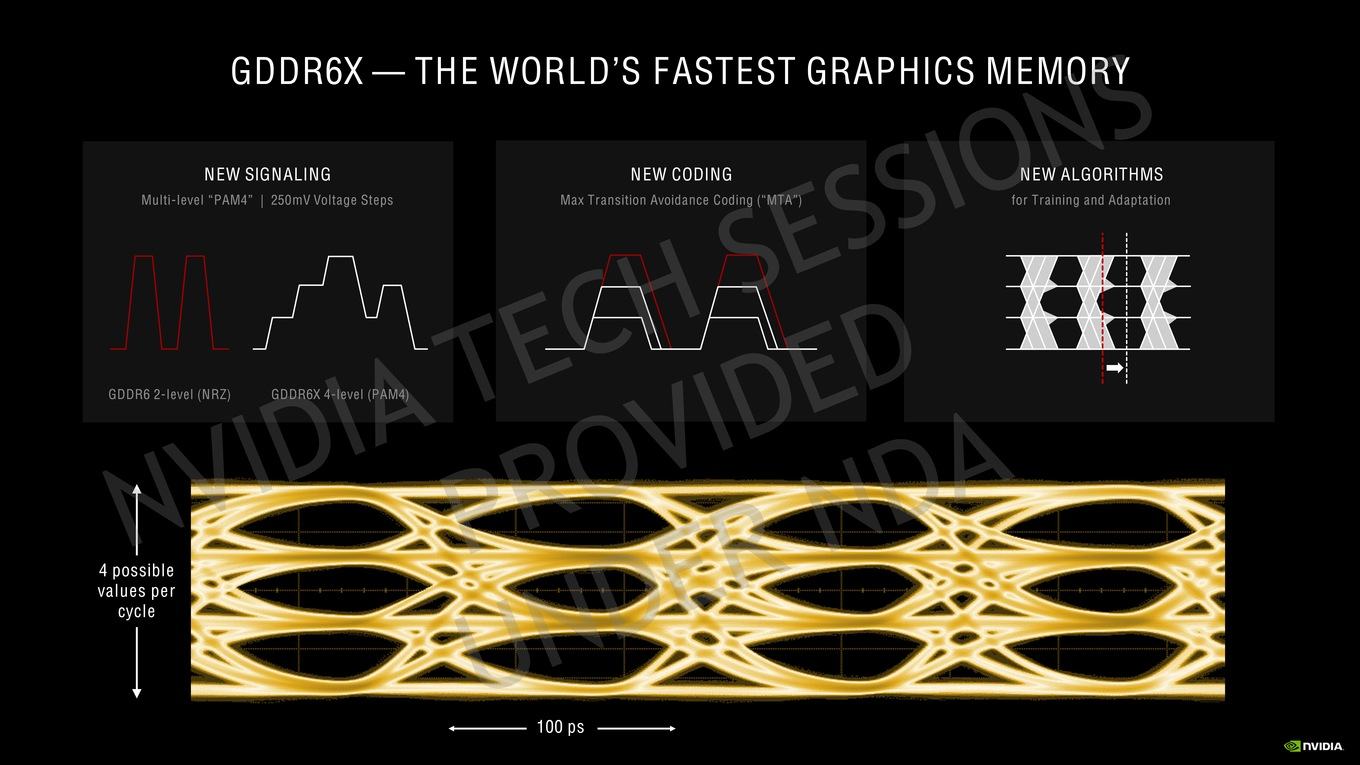

GDDR6X

Eine immer höhere Speicherbandbreite ist bei der Vielzahl an Shadern von entscheidender Bedeutung. Die Cache-Hierarchie wird schneller und so muss auch der Speicher immer schneller werden. GDDR6 hätte nur noch über einen höheren Takt eine höhere Speicherbandbreite ermöglicht. Eine Alternative wäre die Verbreitung des Speicherinterface gewesen. HBM besitzt ein extrem breites Speicherinterface, ist in der Integration und Fertigung aber einfach zu teuer – und kommt daher entsprechend noch nicht zum Einsatz.

NVIDIA hat sich also mit Micron zusammengetan und GDDR6X entwickelt. GDDR6X arbeitet in etwa mit dem gleichen Takt wie GDDR6 und arbeitet auch mit vergleichbarer Spannung.

Für den bisherigen GDDR6-Speicher wird eine Non-Return-to-Zero (NRZ) Pulsamplitudenmodulation verwendet. Zwischen "0" und "1" wird durch einen Unterschied in der High- und Low-Spannung unterschieden. GDDR6X wechselt auf ein PAM4, für die das Trägersignal in vier Spannungslevel pro Taktzyklus unterteilt wird. Die einzelnen Schritte betragen gerade einmal 250 mV. Das PAM4 kommt bei immer mehr Übertragungsstandards zum Einsatz. Auch PCI-Express 5.0 und DDR6 werden auf PAM4 setzen.

NVIDIA und Micron wenden zudem ein paar Tricks an, um eine derartige Übertragung bei den gewünschten Taktraten noch gewährleisten zu können. Das sogenannte Max Transition Avoidance Coding (MTA) sorgt dafür, dass das Signal nur in bis zu zwei Spannungslevel wechselt. Würde der Wert vom niedrigsten auf das höchste Spannungslevel springen können, währen die "Augen" im Signal nicht mehr deutlich zu unterscheiden und eine Signalübertragung nicht möglich. Mit MTA setzt sich NVIDIA in die Codierung des Signals und sorgt dafür, dass eine entsprechend kompatible Kodierung vorgenommen wird.

Zuletzt ermöglicht NVIDIA dem System auch eine gewisse Dynamik, denn selbst kleine Unterschiede in der Fertigung von PCB und Speicher sorgen für Unterschiede in der Signallaufzeit. Algorithmen können die Signalübertragung entsprechend anpassen.

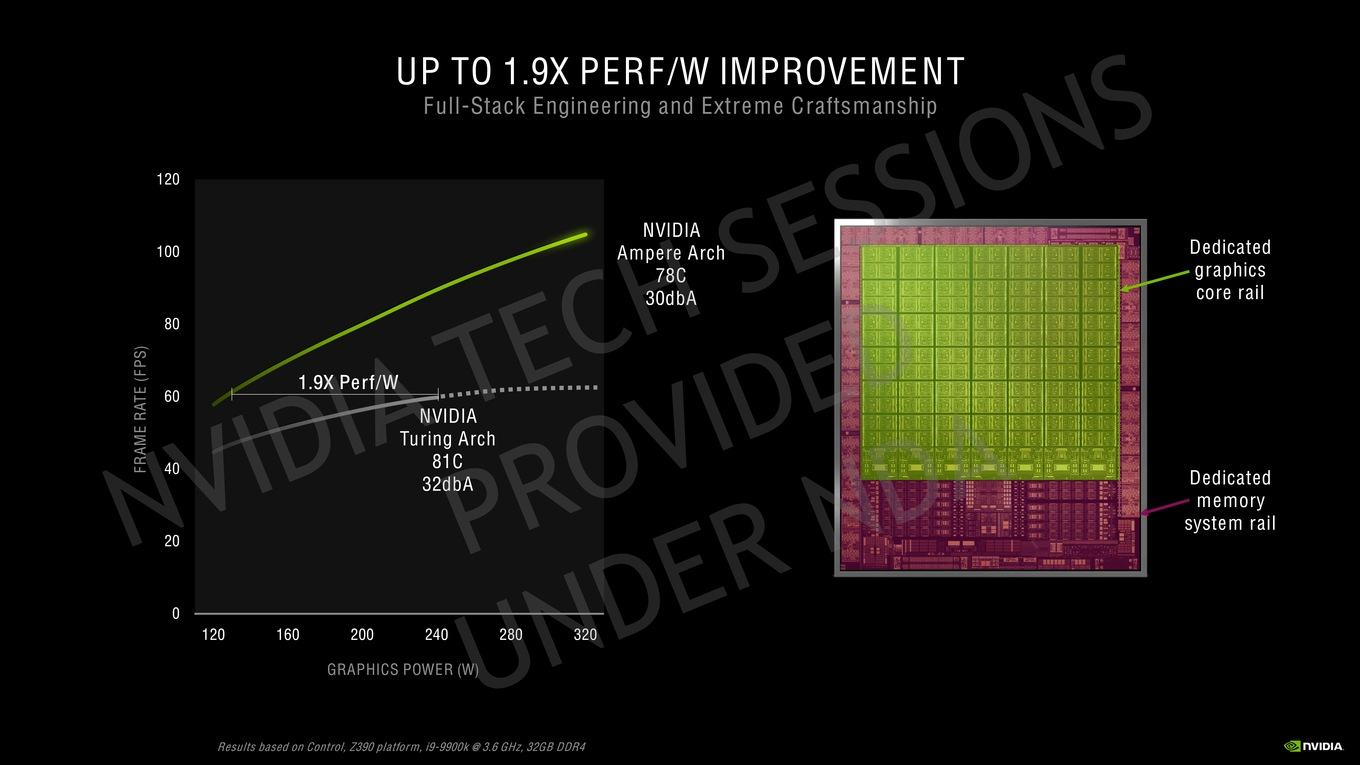

Effizienz

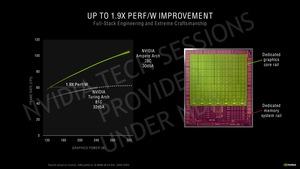

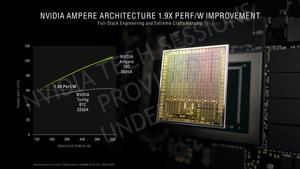

Die Fertigung in 8 nm durch Samsung hat einen Einfluss auf die Effizienz der Ampere-GPUs. NVIDIA hat aber auch noch weitere Änderungen vorgenommen. Etwas verwirrend sind die Angaben NVIDIAs, die neuen GeForce-RTX-Karten seien um den Faktor x1,9 effizienter als die Turing-Vorgänger. Das entsprechende Diagramm dazu muss man sich ganz genau anschauen, um zwischen den von NVIDIA veröffentlichten Angaben und der tatsächlichen Effizienzsteigerung unterscheiden zu können.

NVIDIA nimmt eine Framerate von 60 FPS als Basiswert und übernimmt die dazu notwendigen 240 W für eine Turing-Karte. Dies vergleicht man dann mit der notwenigen Leistungsaufnahme für 60 FPS einer Ampere-Karte und landet bei etwa 130 W. 240 zu 130 W ergeben in etwa die um den Faktor x1,9 höhere Effizienz.

Eigentlich müsste NVIDIA allerdings die Leistung bei einer bestimmten Leistungsaufnahme miteinander vergleichen. Nehmen wir also wieder die 240 W für 60 FPS bei Turing, kommen wir bei 60 FPS für Ampere auf etwa 90 FPS. Wir sprechen hier also von einem um 50 % höheren Verhältnis der Leistung pro Watt. Dies ist noch immer sehr viel, entspricht jedoch nicht dem Faktor x1,9 wie ihn NVIDIA verkündet.

Was NVIDIA gemacht hat, ist schlicht und ergreifend ein Vergleich, der Turing außerhalb des idealen Effizienzfensters mit Ampere innerhalb des idealen Effizienzfensters gegeneinander stellt. Bei 240 W wird eine Karte mit Turing-GPU nicht im idealen Spannung/Takt-Verhältnis betrieben, während die Ampere-GPU mit 130 W noch im Bereich der guten Effizienz arbeiten kann.

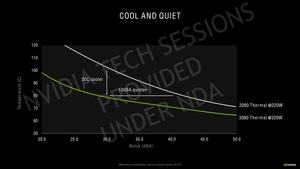

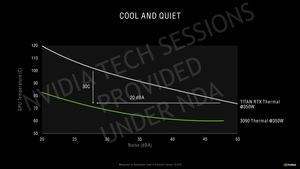

Ja, die neuen GeForce-RTX-Karten bieten ein deutlich höhere Leistung, NVIDIA benötigt dazu aber auch eine GPU mit 28 Milliarden Transistoren und setzt die GeForce RTX 3090 auf eine TDP von 350 W und selbst die GeForce RTX 3080 genehmigt sich noch 320 W. Dies muss natürlich bei der Effizienz der Karten mit bedacht werden und spielt eine Rolle. Dem setzt man zwei dedizierte Spannungsschienen der GPU entgegen. Eine ist für die Shadereinheiten verantwortlich, eine weitere für das Speicher-System. Die beiden Spannungsschienen können getrennt voneinander angesteuert werden, was die Effizienz verbessert.

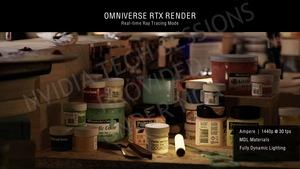

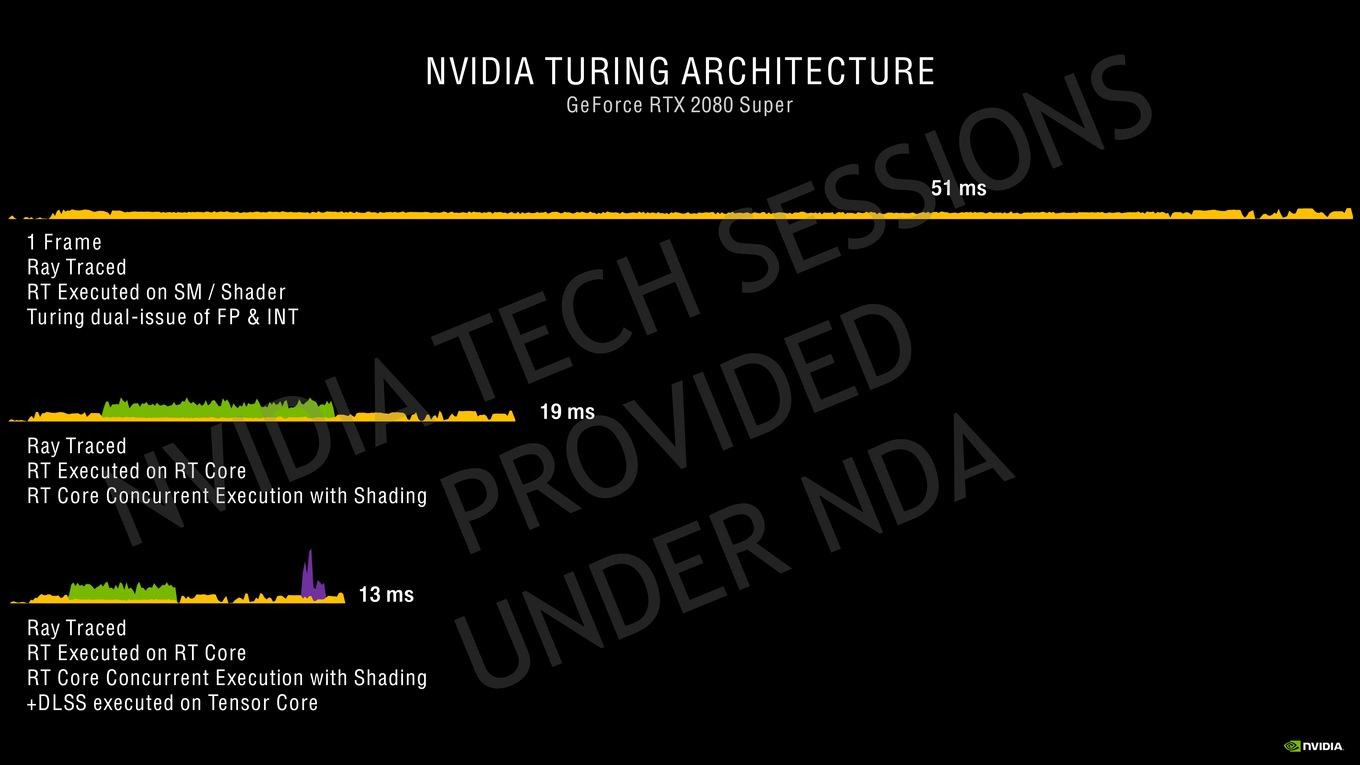

Nächster Schritt der Hybrid Rendering Pipeline

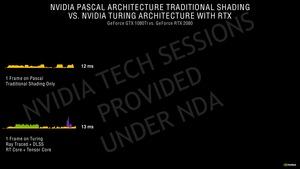

Mit der Turing-Architektur und der Möglichkeit, ein Raytracing per RT Cores und ein AI-Upscaling mittels DLSS bzw. der Tensor Cores anzuwenden, sprach NVIDIA erstmals über die Hybrid Rendering Pipeline. Dies beschreibt den Umstand, dass neben einem klassischen Shader-Rendering, ein Raytracing angewendet wird und noch ein DLSS hinzukommt.

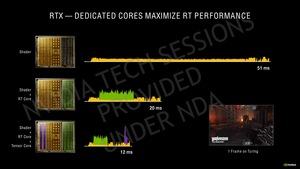

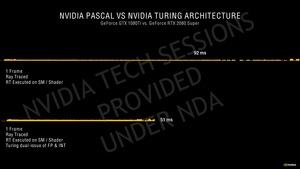

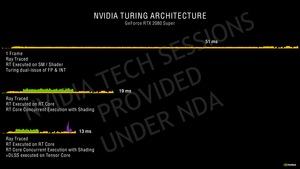

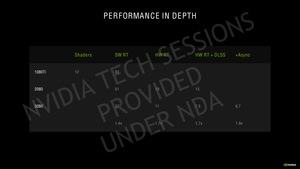

Für ein Frame in Wolfenstein Youngblood nimmt NVIDIA für eine Turing-GPU ein Renderzeit von 51 ms an. Dies beinhaltet auch die Raytracing-Berechnungen auf den Shadereinheiten durchzuführen. Wird das Raytracing auf die RT Cores ausgelagert, reduziert sich die Renderzeit auf 19 ms. Kommt nun auch noch ein AI-Upscaling hinzu, kann die Renderzeit sogar auf 13 ms reduziert werden.

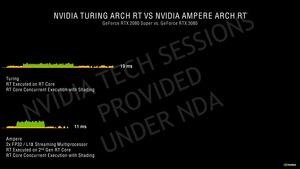

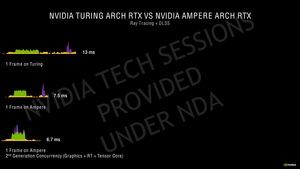

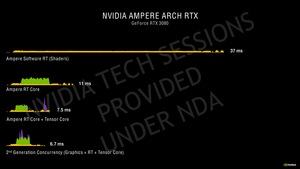

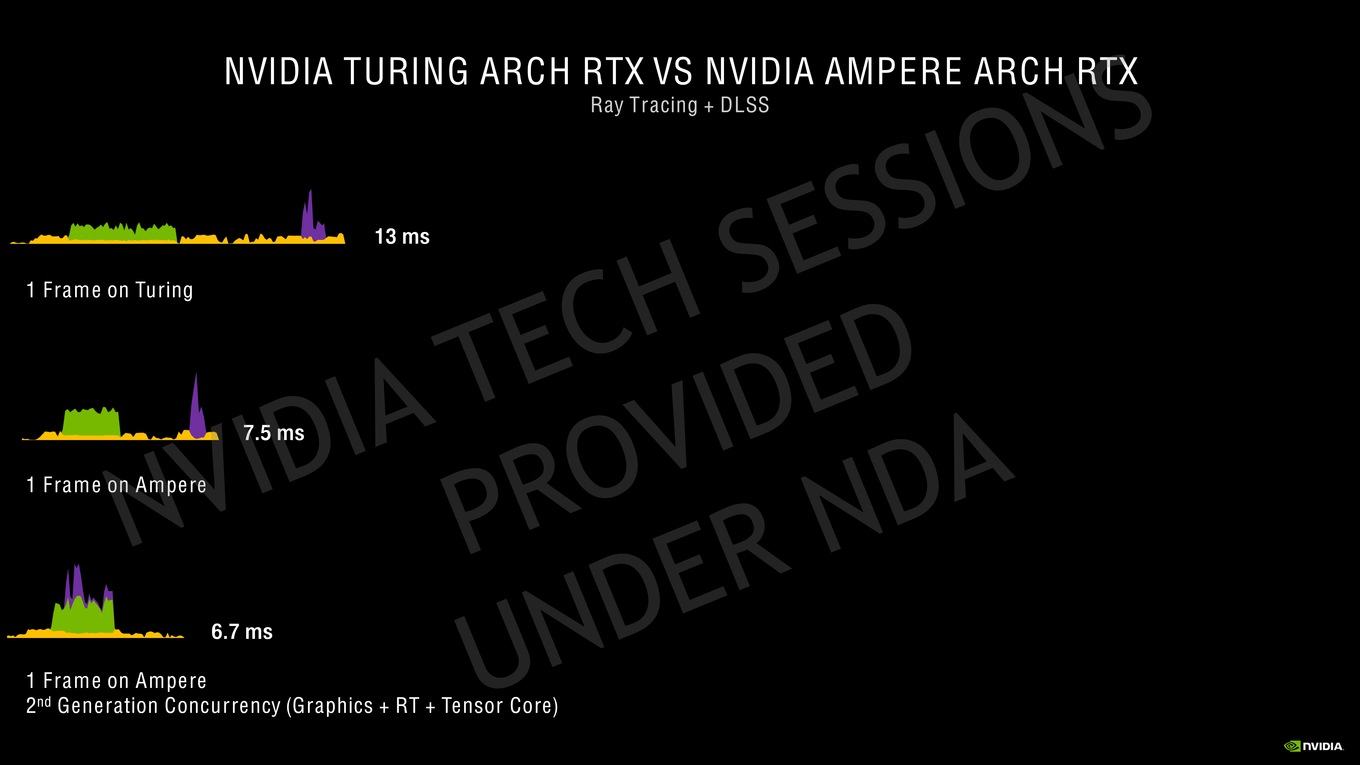

Für eine Ampere-GPU mit einer höheren Shaderleistung reduziert sich die Renderzeit von 13 ms ausgehend auf 7,5 ms. Dies liegt vor allem an der höheren Shaderleistung. Aber auch die Raytracing- und DLSS-Berechnungen werden schneller, was einen Einfluss auf die Reduzierung hat. Für Ampere wendet NVIDIA nun noch einen weiteren Trick an und kann die DLSS-Berechnungen bereits vor dem finalen Rendering ausführen. Dabei spielt ein temporales Feedback eine Rolle – es werden also die vorherigen Frames mit in die Berechnung einbezogen, was man in DLSS 2.0 schon für die Verbesserung der Bildqualität getan hat. Mit Ampere nutzt man dies auch für eine Reduzierung der Renderzeit.

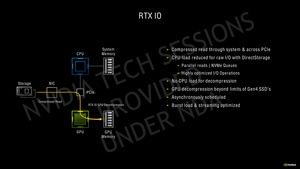

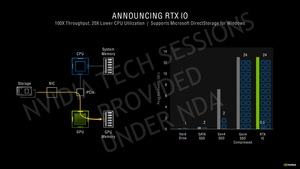

RTX IO

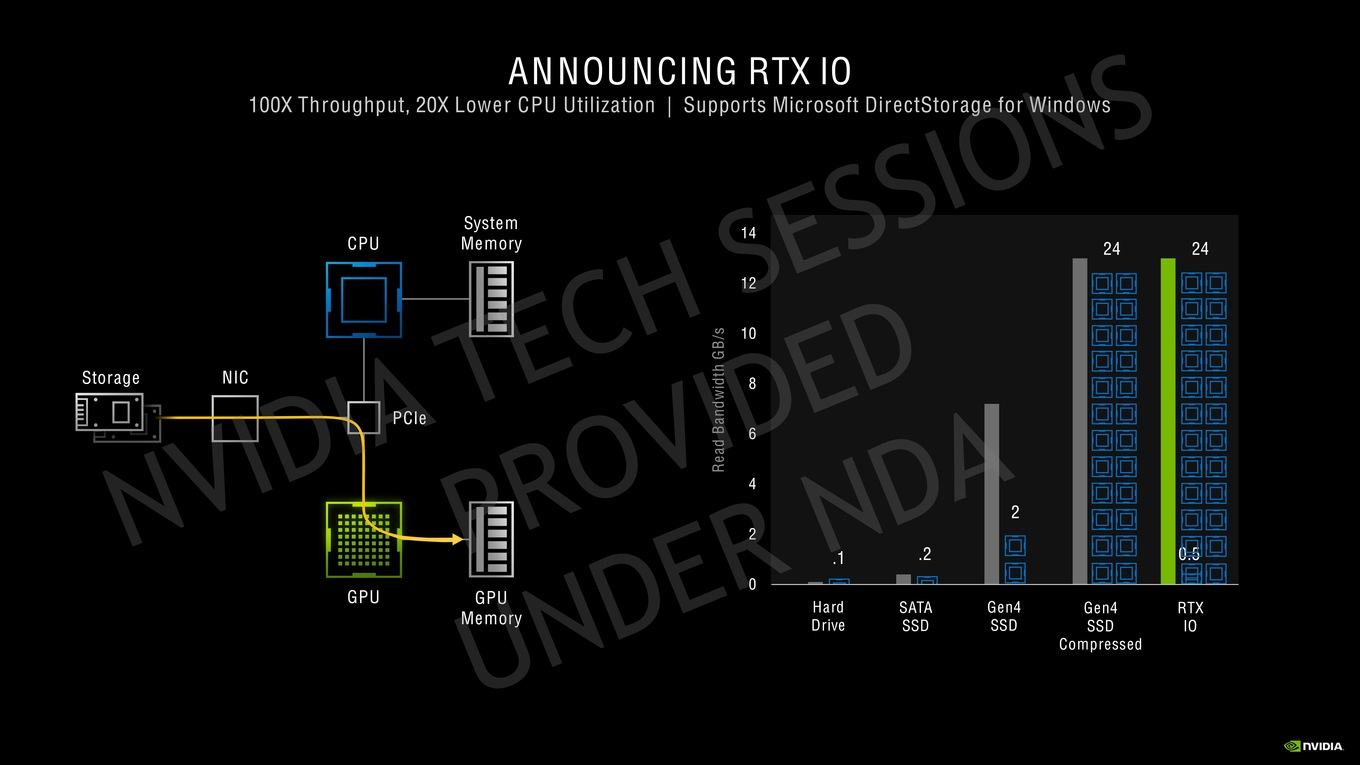

NVIDIA RTX IO arbeitet mit Microsofts kommender DirectStorage-API zusammen, die ab 2021 von Spielen unterstützt werden wird. Dabei handelt es sich um eine Speicherarchitektur der nächsten Generation, die speziell für Gaming-PCs mit NVMe-SSDs ausgelegt wurde. DirectStorage-API bzw. RTX IO sind optimierte und parallelisierte APIs, die speziell auf Spiele zugeschnitten wurden, was eine drastische Reduzierung des IO-Overhead bedeuten soll.

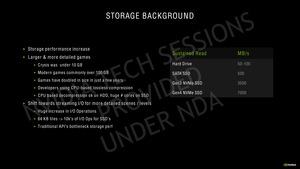

Ein Grund für die Notwendigkeit einer schnelleren IO-Schnittstelle sind Spiele, die immer größer werden und deren Assets auch an Komplexität zugenommen haben.

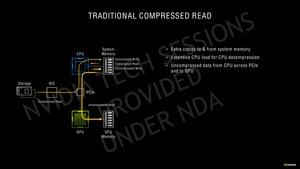

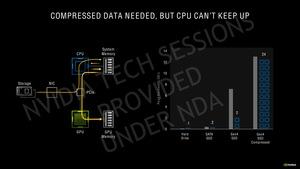

Klassischerweise werden die Spieldaten von einer SSD/HDD gelesen und per SATA oder PCI-Express an den Prozessor übertragen. Bei schnellen PCIe-4.0-SSDs sprechen wir hier von bis zu 7 GB/s. Der Prozessor verschiebt die Daten in den Arbeitsspeicher, von dort geht es wieder über die CPU und das PCI-Express-Interface zur GPU, welche die Daten dann im Grafikspeicher ablegt. Dies belastet vor allem den Prozessor unnötig und bei 7 GB/s ist ohne weitere Limitierung auch das Ende der Fahnenstange erreicht.

Es gibt auch die Möglichkeit, die Daten komprimiert zum Prozessor zu übertragen. Entpackt werden sie dann im Arbeitsspeicher und unkomprimiert via PCI-Express zur GPU in deren Speicher übertragen. Zwar können hier bis zu 14 GB/s erreicht werden, allerdings sind dann 24 Kerne mit der Dekomprimierung beschäftigt.

RTX IO bzw. DirectStorage ermöglicht die Übertragung der Daten von einer schnellen SSD direkt über das PCI-Express-Interface in die GPU und dort in den Grafikspeicher. Der Prozessor und Arbeitsspeicher wird komplett ausgelassen. Auch hier können 14 GB/s für komprimierte Daten (Kompressionsverhältnis von 2:1) erreicht werden – allerdings ohne dass der Prozessor belastet wird.

Die Dekomprimierung von der GPU erledigt, dass dies einen Einfluss auf die restliche Leistung hätte. Derartige Bedenken räumt NVIDIA selbst für das Arbeiten am PCIe-4.0-Limit aktueller SSDs aus. Sind die Spiele per DirectStorage-API optimiert, werden von der SSD nur die Daten abgerufen, die auch wirklich benötigt werden. Dies soll auch den Grafikspeicher entlasten.

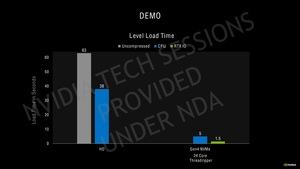

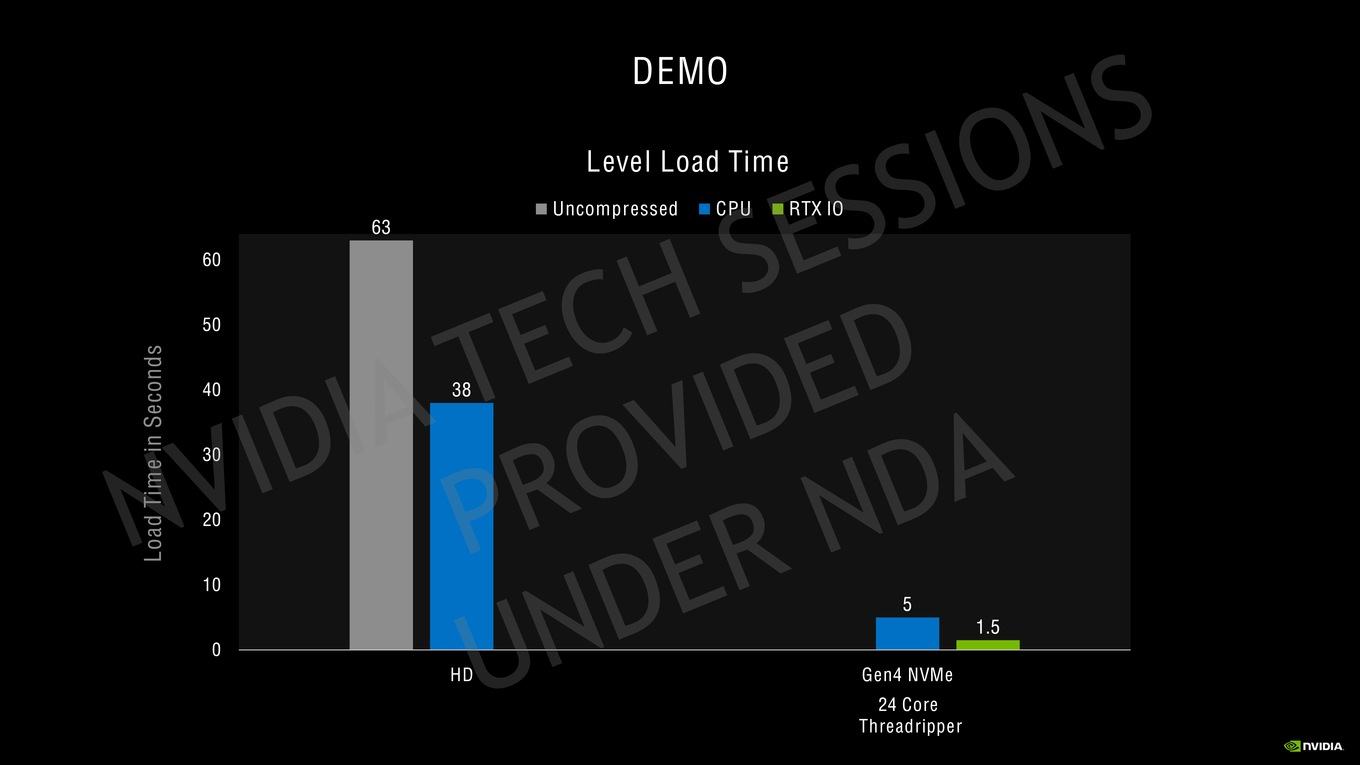

NVIDIA nennt auch gleich einige Leistungsdaten und verwendet dafür die eigene Marbles-Techdemo. Diese benötigt unkomprimiert eine Ladezeit von mehr als 60 s mit einer Festplatte. Mit komprimierten Daten über die CPU sind es etwa 37 s. Kommt eine NVMe-SSD zum Einsatz, beträgt die Ladezeit nur noch 5 s - die Daten müssen aber über den Prozessor entpackt werden und benötigen dazu 24 Kerne unter Volllast. Per RTX IO sollen es nur 1,6 s sein.

Die DirectStorage-API spielt für die Xbox Series X von Microsoft ebenso eine Rolle wie ähnliche Konzepte für die PlayStation 5. Mit RTX IO sollen 14 GB/s von der SSD in den Grafikspeicher übertragen werden können. Zum Vergleich: Sonys PlayStation 5 kommt auf 8 bis 9 GB/s und die Microsoft Xbox Series X auf 4,8 GB/s. Man darf gespannt sein, ob AMD für Big Navi ebenfalls an einer Unterstützung von DirectStorage arbeitet.