Werbung

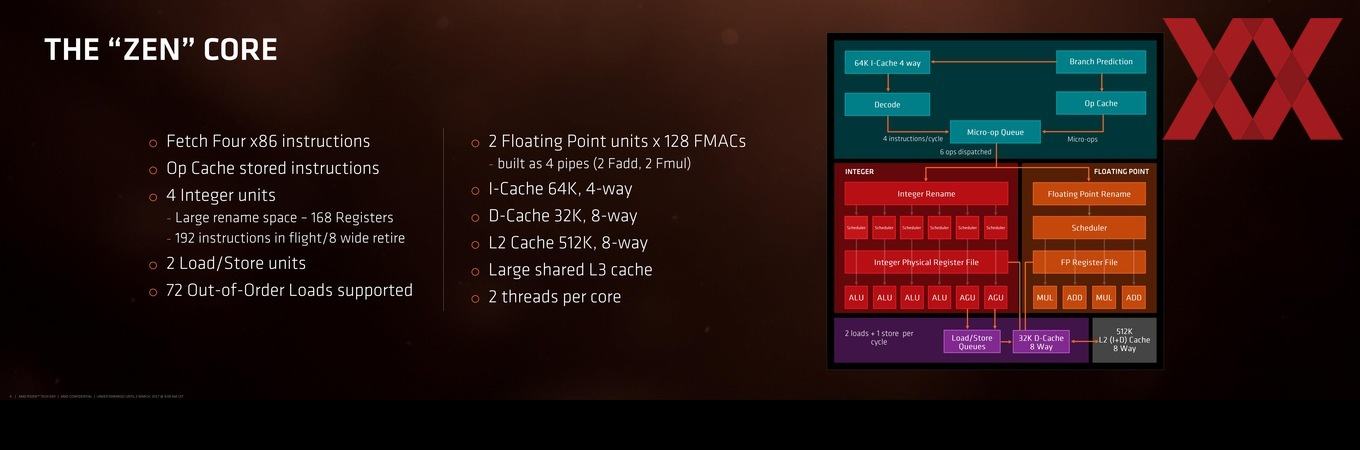

Eine der größten Änderungen innerhalb der Zen-Architektur ist, dass jeder Kern wieder mehr für sich allein steht. In der Bulldozer-Architektur wurde eine Sharing zahlreicher Komponenten vorgesehen – FPU, SIMD und der L2-Cache waren eine Ressource, die zwischen zwei CPU-Kernen aufgeteilt wurde. All dies steht nun einem CPU-Kern exklusiv zur Verfügung, teilt sich aber bei Bedarf auf zwei Threads auf – ähnlich wie bei Intels Hyper Threading.

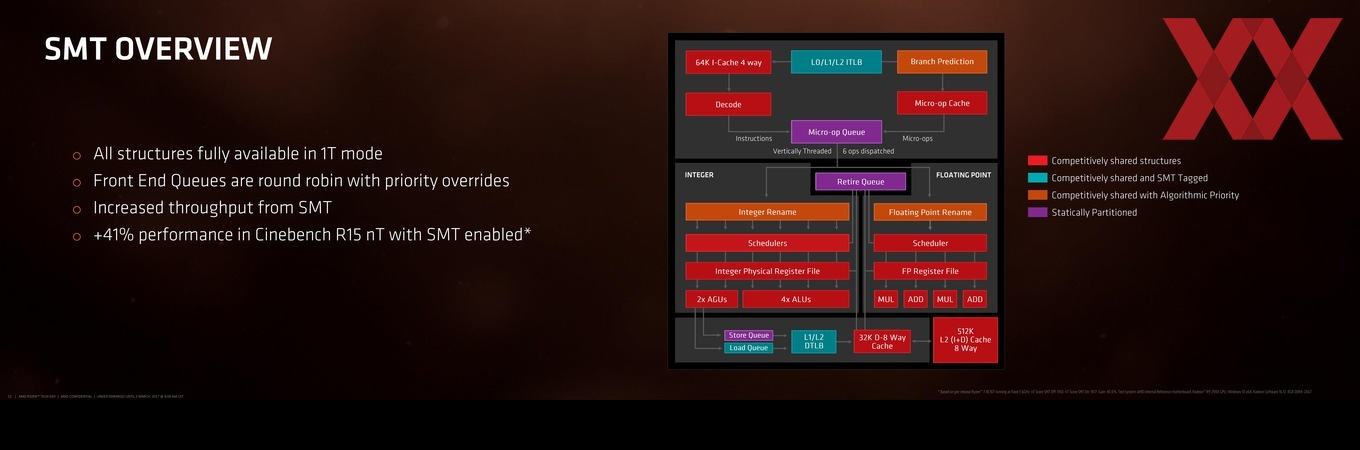

Eine wichtige Neuerung bei AMD ist der Micro-Op-Cache. Intel verwendet diesen bereits seit der Sandy-Bridge-Architektur. Der Micro-Op-Cache beschleunigt das x86-Decoding und wird vom Instruction Fetch und der Decode Pipeline gefüttert. Die Instructions und die Branch Prediction erfolgen in 64 Byte großen Blöcken, teilen sich im Instruction Fetch auf 2x 32 Byte auf. Die Branch Prediction selbst funktioniert dynamisch und kann Branches, die fehlerhaft zugeordnet wurden, erneut zuteilen und priorisieren.

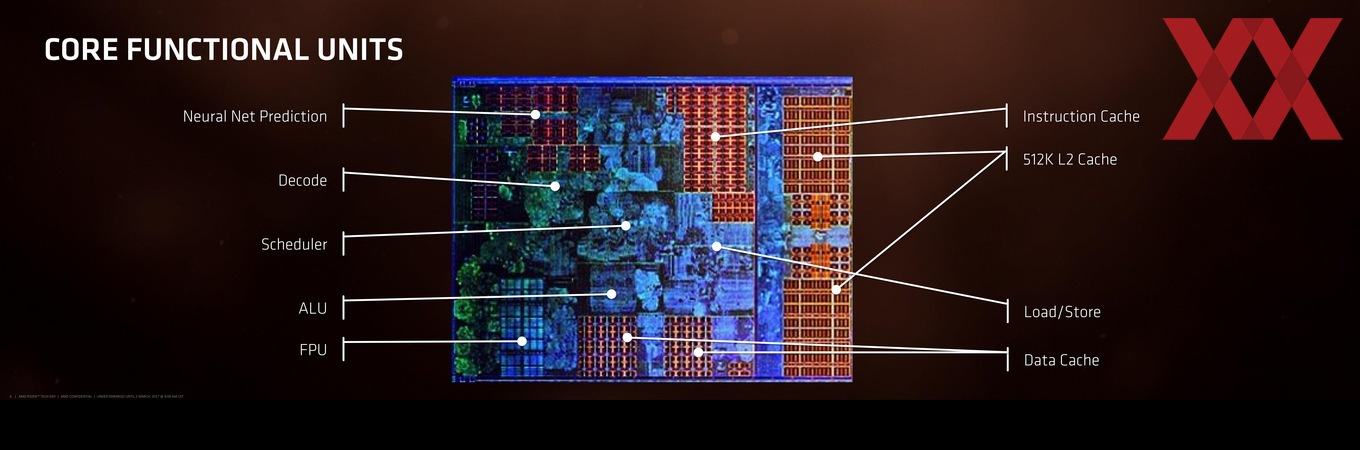

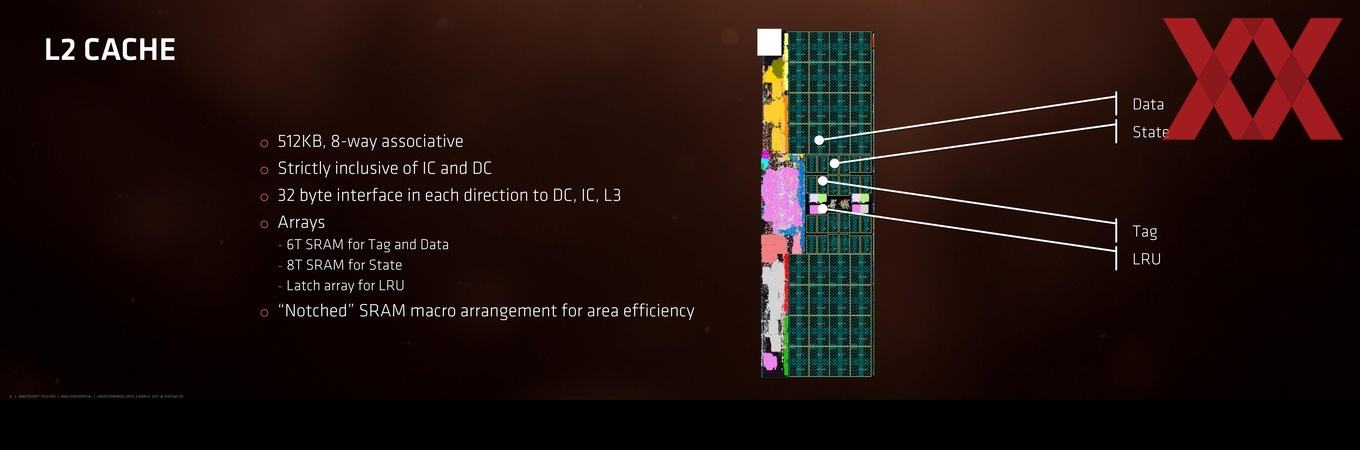

Der Zen-Kern als solches verfügt über vier Integer-Einheiten, die über 168 Register verfügen und die 192 Instruktionen in Flight bearbeiten können. Zwei Load/Store-Einheiten kümmern sich darum, die Daten nach der Bearbeitung wieder in die Caches zu schreiben. Ebenfalls zur Verfügung stehen zwei Fließkomma-Einheiten mit jeweils 128 Floating Point Multiply Accumulatoren. Der Instruktion-Cache ist 64 kB groß und kann vierfach beschrieben und gelesen werden, der Data-Cache fasst 32 kB und auf diesen kann achtfach zugegriffen werden. Der dazugehörige L2-Cache misst 512 kB und kann ebenfalls achtfach beschreiben oder gelesen werden. Hinzu kommt ein Shared-L3-Cache.

Auf drei Standsäulen baut sich der neue Zen-Kern hauptsächlich auf: Ein optimierter und schnellerer Kern als solcher, ein verbessertes Caching-System und eine niedrigere Leistungsaufnahme. Zur Leistungssteigerung trägt hauptsächlich die Unterstützung von Multi Threading bei. Damit lässt sich der größte Sprung bewältigen. Hinzu kommen aber auch eine verbesserte Vorhersage und Zuteilung der Rechenaufgaben, sodass es weniger Fehler und fehlerhafte Zuteilungen gibt, was weniger Durchläufe notwendig macht. Ein großer Op-Cache hilft an dieser Stelle und ist neu in der Zen-Architektur.

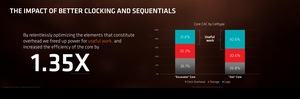

Der Micro-Op-Dispatch wurde von sechs auf vier erweitert. Der Instruction Scheduler ist mit 84 gegenüber 48 Integer- und 96 gegenüber 60 Floating-Point-Operationen ebenfalls deutlich größer. Potenziell fehlerhafte Instruktionen können nun in einer Anzahl von acht anstatt vier zurückgezogen werden, bevor sie überhaupt in die Pipeline gelangen. Allesamt sind auch die Queues größer geworden und bemessen nun 192 für das Retiring, 72 für die Load- und 44 für die Store-Unit.

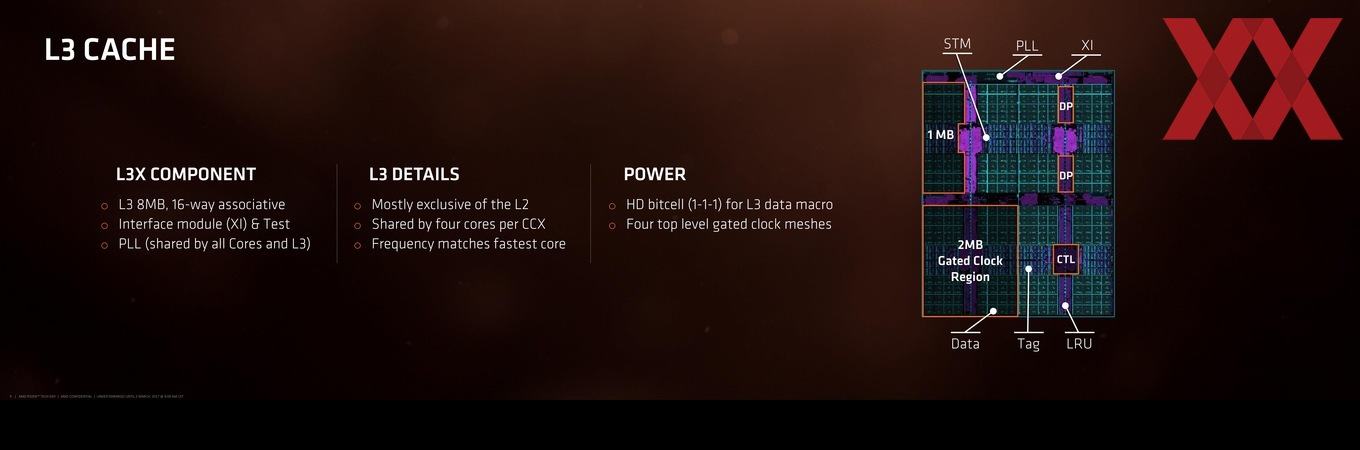

Der L1-Cache ist nun mit einer Writeback-Funktion versehen worden, was zu einem Großteil dafür sorgt, dass die einzelnen Kerne effizienter geworden sind. Der L2-Cache wurde ebenfalls deutlich beschleunigt und der L3-Cache taktet nun mit dem gleichen Takt, wie der schnellste Kern des CPU Complex. AMD konnte die Bandbreite des L1- und L2-Caches verdoppeln, der L3-Cache ist sogar bis zu fünfmal schneller angebunden.

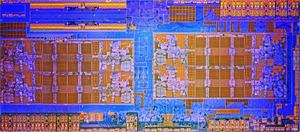

Schaut man sich den sogeannten Floor Plan eines CPU Complex der Zen-Architektur an, wird gleich deutlich, wie klein die eigenen Recheneinheiten in Form von ALU und FPU im Verhältnis zu den restlichen Komponenten sind. Die Caches, der Scheduler und die Prediction-Einheiten belegen etwa 80 % des Platzes.

Große Fortschritte hat AMD bei der Implementierung des L2-Caches gemacht. Dies gilt für die Fertigung, die 512 kB auf 1,5 mm² packt, während Intel auf 0,9 mm² nur 256 kB unterbringen kann. AMD wählt die Bandbreite des L2-Caches aber auch etwas ausgewogener als Intel, die viel Fläche für die Anbindung opfern, was im Serverbereich ein Vorteil ist, bei den Desktop-Prozessoren aber keine allzu große Rolle spielt. AMD kann hier in dieser Hinsicht also eine gewisse Ausgewogenheit nachgesagt werden.

Diesen zunächst einmal auf dem Papier vorhandenen Vorteil hat sich AMD auch beim L3-Cache erarbeitet. Dieser kann 16-fach assoziiert werden und die 8 MB teilen sich bis zu vier Kerne eines CPU Complex. Die Frequenz des L3-Caches passt sich der des schnellsten Kerns im CPU Complex an. Um Strom zu sparen teilt sich der L3-Cache in vier Bereiche auf, die getrennt voneinander mit Spannung versorgt werden können, sodass nur die Bereiche versorgt sind, die auch wirklich gebraucht werden.

Einen Großteil der Multi-Threaded-Leistung bezieht AMD natürlich aus der Unterstützung von Simultaneous Multithreading – also der Möglichkeit zwei Threads pro Kern zu verarbeiten. Im Falle eines Threads pro Kern stehen diesem natürlich alle Ressourcen zur Verfügung. Sollen aber zwei Threads verarbeitet werden, sind bestimmte Priorisierungen notwendig. Hinzu kommt der Umstand, dass bestimmte Ressourcen nur noch geteilt zur Verfügung stehen. Im Schaubild sind diese exklusiven und geteilten Bereiche markiert.

[h3]Zen-Architektur nicht zwangsläufig auf Server ausgelegt[/h3]

AMD plant die Zen-Architektur in Form der Naples-Prozessoren auch auf dem Servermarkt anzubieten. Ob AMD hier eine Chance gegen Intel haben wird, ist die Frage. Mit Naples konzentriert man sich zunächst auf die Single- und Dual-Sockel-Systeme. Um sich nicht in allen Bereichen des Server-Segments zu verlieren, plant AMD offenbar eine gezielte Ausrichtung von Naples auf einen bestimmten Markt. Server mit einem Sockel sollen in Kürze Dual-Sockel-Systeme ersetzen – aber auch diese werden noch eine Weile eine große Rolle spielen. Mit Naples deckt AMD beide Märkte nach eigenen Angaben sehr gut ab.

Forrest Norrod von AMD dazu: „Single Socket CPU Platforms Rising. Thanks to the move to more advanced chip manufacturing processes and the availability of more transistors, a single SoC (1P) server can now fill the need for many of today’s 2P server platforms. This is great news for both on-premises and off-premises customers of IT hardware."

Mit 32 Kernen und 64 Threads pro SoC zielt AMD aber natürlich auch auf die Notwendigkeit von mehr und mehr Kernen ab, die gleichzeitig verarbeitet werden können. „Processor Cores Matter. In a world of cloud computing, being able to deliver more useful work across more cores and their supporting resources equals more efficient provisioning of services to more users and lower TCO. Simple as that", so Norrod.

AMD hat aber auch eine Gesamtstrategie in der Hinterhand, denn schnelle SoCs bzw. Prozessoren decken nur einen Teil der Bedürfnisse ab. In fast allen Compute-Bereichen spielen GPUs eine immer wichtigere Rolle und mit den Radeon-Instinct-Karten plant AMD hier auch die passende Hardware auf den Markt zu bringen. Auf dem Tech Summit 2016 zeigte AMD erstmals einen Naples-Server mit den dazu passenden GPU-Beschleunigern. Rein auf die Rechenleistung der Prozessoren bezogen wird man mit Intels Haswell- und Skylake-Architektur im Serverbereich nicht mithalten können. Mit AVX-FMA-Instruktionen bietet Intel die doppelte Anzahl an FLOPS pro Takt und auch die doppelte Cache-Bandbreite für die Floating-Point- und SIMD-Einheiten. Die Nutzung von AVX512-Instruktionen wird diesen Vorsprung für Intel noch vergrößern. Im HPC-Bereich wird es AMD daher auch mit Naples gegen Intel schwer haben und daher auch die Konzentration von AMD auf bestimmte Bereiche.

„Heterogeneous Systems go Mainstream. GPUs and other accelerators supporting the CPU will become fundamental building blocks of computing. A host of new applications incorporating deep neural networks and machine learning, artificial intelligence, virtual and augmented reality will be supported in the datacenter by combinations of GPUs, CPUs and FPGAs", so Forrest Norrod dazu.

Neben der reinen CPU-Leistung spielen im Server-Segment aber auch Dinge wie die Speicheranbindung, I/O-Fähigkeiten und Sicherheitsfunktionen eine wichtige Rolle. Unter anderem können bestimmte Bereiche des Arbeitsspeichers für einzelne virtuelle Instanzen verschlüsselt werden – Secure Memory Encryption (SME) und Secure Encrypted Virtualization (SEV) heißen die dazugehörigen Technologien. Ziel beider ist die Verschlüsselung der Daten im Arbeitsspeicher. Dazu verwendet AMD eine AES128-Verschlüsselung mit einem geheimen Schlüssel. Dieser soll nicht ausgelesen oder manipuliert werden können. SME und SEV arbeiten aber auf unterschiedlichen Ebenen der Verschlüsselung.

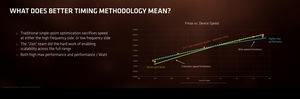

AMD opfert den Server-Bereich aber auch teilweise, um Chipfläche einsparen und die Effizienz hochhalten zu können. Auf der International Solid State Circuits Conference 2017 (ISSCC) verglich AMD die eigenen Anstrengungen gegenüber Intel.