Werbung

Die Sunny-Cove-Architektur bedeutete für Intel die erste grundlegende Neustrukturierung einer Prozessor-Mikroarchitektur seit Skylake aus dem Jahre 2015. Das, was wir als Comet Lake-S aktuell noch auf dem Desktop sehen, basiert eben noch auf Skylake. Erst mit Rocket Lake-S findet nun ein Wechsel statt, der aber von dem Umstand begleitet wird, dass die Prozessoren weiterhin in 14 nm gefertigt werden. Bis heute, also Frühjahr 2021, hat es Intel also nicht geschafft, die Fertigung in 10 nm in den Griff zu bekommen.

Sunny Cove ist gleichzeitig nur der erste Schritt gewesen. Denn mit Willow Cove und den Tiger-Lake-Prozessoren ist Intel im mobilen Segment schon den nächsten Schritt gegangen und hat gleichzeitig die Fertigung in 10 nm derart verbessert, dass nun zumindest eben diese Mobilprozessoren gefertigt werden können. Die Ausbeute soll trotz 10 nm dank der "10nm SuperFin Technology" zwar noch nicht an einem Punkt sein, den sich Intel gewünscht hat, zumindest aber die mobilen Prozessoren können in dieser Form ihre Leistungsziele erreichen.

Doch Cypress Cove bringt nun den Wechsel auf eine völlig neue Architektur. Diese besitzt ein breiteres Front-End und ein tieferes Back-End.

Intel führt mit Cypress Cove eine 5-Wide-Out-of-Order-Architektur-Pipeline ein. Hier gibt es nun vier Unified Reservation Station (RS), was es Intel ermöglicht, die Instruktionen paralleler einfließen zu lassen, als bei Skylake. Womöglich auch um den Spectre-Mitigierungen entgegen zu wirken, hat Intel der AGU (Address Generation Unit) vier feste Ports zugewiesen. Jeweils zwei AGUs wird eine Load/Store-Unit zugewiesen. Für VEC- und INT-Berechnungen gibt es nun weitere Recheneinheiten in den jeweiligen Ports. All diese Maßnahmen sollen zur Beschleunigung der Architektur beitragen.

Weiterhin wird Cypress Cove neue ISA-Befehlssätze unterstützen. Dazu gehören Vector-AES und SHA-NI, aber auch AVX512. Bei den beiden erstgenannten handelt es sich um Algorithmen zur Hardwarebeschleunigung von Ver- und Entschlüsselungen. Generell soll der Fokus auf der Beschleunigung von Krypthografie-Algorithmen liegen, was wiederum die von Intel angesprochenen Optimierungen bei den speziellen Anwendungen betrifft.

Besonders die AVX512-Erweiterungen stehen bei Rocket Lake-S im Fokus, denn hier kann die ein oder andere Anwendung durchaus umfangreich profitieren:

- AVX512VPOPCNTDQ: AVX512 Vector Population Count Doubleword and Quadword

- AVX512VNNI: AVX512 Vector Neural Network Instructions

- AVX512GFNI: AVX512 Galois Field New Instructions

- AVX512VAES: AVX512 Vector AES

- AVX512VBMI2: AVX512 Vector Bit Manipulation, Version 2

- AVX512BITALG: AVX512 Bit Algorithms

- AVX512VPCLMULQDQ: AVX512 Vector Vector Carry-less Multiply

Im Rahmen des Vorab-Tests des Core i7-11700K war die Unterstützung von AVX512 besonders im Y-Cruncher-Benchmark zu erkennen.

Aufgrund der Erweiterung des Linear Adress Space auf 57 Bit, bzw. des Physical Adress Space auf 52 Bit wird ein Prozessor auf Basis der Cypress-Cove-Architektur bis zu 4 TB an Arbeitsspeicher pro Sockel ansprechen können. Diese Anleite der Sunny-Cove-Architektur wird allerdings nur bei den Xeon-Prozessoren (Ice Lake-SP) eine Rolle spielen.

Änderungen gibt es auch in der Cache-Hierarchie. Der L1-Data-Cache wird um 50 % von 32 auf 48 kB vergrößert. Der L2-Cache gar auf 512 kB pro Kern verdoppelt. Der Translation Lookaside Buffer (TLB) wächst ebenfalls an, bietet zudem die Möglichkeit, größere Adresstabellen anzulegen. Auch der µOP-Cache wächst an.

| Skylake | Sunny Cove | Cypress Cove | Willow Cove | |

| L1-Data Cache | 32 KByte pro Kern | 48 KByte pro Kern | 48 KByte pro Kern | 48 KByte pro Kern |

| L1-Instruction Cache | 32 KByte pro Kern | 32 KByte pro Kern | 32 KByte pro Kern | 32 KByte pro Kern |

| L2-Cache | 256 kByte pro Kern | 512 kByte pro Kern | 512 kByte pro Kern | 1.280 kByte pro Kern |

| L2-Cache TLB | 1.536 | 2.048 | 2.048 | 2.048 |

| L3-Cache | 20 MB bei 10 Kernen | 8 MB bei 4 Kernen | 16 MB bei 8 Kernen | 12 MB bei 4 Kernen |

| µOp-Cache | 1.500K µOps | 2.250K µOps | 2.250K µOps | - |

| OoO Window | 224 | 352 | 352 | - |

| In-Flight Loads | 72 | 128 | 128 | 128 |

| In-Flight Stores | 56 | 72 | 72 | 72 |

| Speichercontroller | DDR4-2933 | DDR4-3200 LPDDR4-3744 | DDR4-3200 | DDR4-3200 LPDDR4-3744 LPDDR5-5400 |

Von Skylake zu Sunny Cove zeigen sich deutliche Veränderungen in der Größe des L1-Data- und des L2-Cache. Dessen Kapazität hat sich pro Kern in diesem Schritt verdoppelt – beim L1-Data-Cache um 50 % erhöht. Die Kapazität des L3-Cache hat sich hingegen nicht verändert. Alle Angaben zu den Caches können von Sunny Cove zu Cypress Cove übernommen werden.

Mit den Tiger-Lake-Prozessoren hat Intel in der Willow-Cove-Architektur einen weiteren Schritt gemacht, den wir aber erst gegen Ende des Jahres mit Alder Lake außerhalb des ultramobilen Bereichs sehen werden – sprich auch auf dem Desktop. Hier wurde die Größe des L2-Caches mehr als verdoppelt (im Vergleich zu Cypress/Sunny Cove). Pro Kerne wächst der L3-Cache um 50 % an.

Außerdem hat Intel die Branche Prediction hinsichtlich der Genauigkeit verbessert – interessanterweise ist genau hier (mindestens) eine der Lücken in der Skylake-Architektur vorhanden gewesen, die zu den Side-Channel-Attacken geführt hat.

Rocket Lake-S und die Fertigung in 14 nm

Intel fertigt die Rocket-Lake-S-Prozessoren also weiterhin in 14 nm. Anders als beim Comet-Lake-S-Vorgänger fertigt Intel nur noch einen Chip, der immer acht Kerne plus eine integrierte Grafikeinheit vorzuweisen hat. Die Unterscheidung eines 10-Kern-Chip und eines 6-Kern-Chips gibt es bei Intel hinsichtlich der Fertigung von Rocket Lake-S also nicht.

Hinsichtlich der Fertigung stellt sich die Frage, warum Intel von Comet Lake-S mit bis zu zehn Kernen nun bei Rocket Lake-S mit maximal acht Kernen einen Schritt zurück macht. Auf unsere Nachfrage hin erbrachte die Antwort das zu erwartende Ergebnis: Durch die größeren Caches und die angewachsene GPU ist es Intel nicht möglich, mehr als acht Kerne auf dem Chip unterzubringen. Die CPU- und GPU-Architektur war auf eine Fertigung in 10 nm hin ausgelegt und ist in 14 nm eben deutlich größer geworden, sodass es wirtschaftlich für Intel sinnvoller war, auf acht Kerne zu limitieren.

Auf die Frage hin ob es nicht denkbar gewesen wäre, die integrierte Grafikeinheit wegzulassen und somit einen Chip mit zehn oder gar zwölf Cypress-Cove-Kernen zu realisieren, verwies Intel auf die Abwägung in der weiteren Nutzung der Rocket-Lake-S-Prozessoren. So sei die integrierte Grafikeinheit für die meisten Spieler zwar nicht wichtig, im OEM-Geschäft hingegen schon und die RKL-S-Dies kommen eben nicht nur im Gaming-Segment zum Einsatz. Insofern hat man sich in der Auslegung des Chips auf acht Kerne plus integrierte Grafikeinheit festgelegt.

Intel macht üblicherweise keinerlei Angaben zur Größe seiner Chips. Da auch schon der erste Core i7-11700K geköpft wurde, können wir dessen Größe nun anderweitig ermitteln. Das gesamte LGA1200-Package mit Abmessungen von 37,5 x 37,5 mm herangezogen, kommt der Chip auf eine Größe von 11,37 mm x 23,71 mm und damit eine Gesamtfläche von 269,58 mm².

| Größe | Maximale Anzahl Kerne | Anzahl Transistoren | |

| Rocket Lake-S | 269,6 mm² | 8 | ? 6 Milliarden |

| Comet Lake-S | 206,1 mm² | 10 | - |

| Coffee Lake-S (Refresh) | 180,3 mm² | 8 | ? 4 Milliarden |

| Coffee Lake-S | 153,6 mm² | 6 | - |

| Ryzen 5000 (2x CCD + IOD) | 286,4 mm² | 16 | 10,39 Milliarden |

Vergleicht man dies mit dem Vorgänger Comet Lake-S, der auf 206,1 mm² kommt, wächst der neuen Chip mit acht Cypress-Cove-Kernen um etwa 30 % an. Noch einmal sei erwähnt, dass die 11. Core-Generation nur acht Kerne anzubieten hat, der Vorgänger allerdings derer zehn und dennoch wird der Chip größer. Dies ist der Grund dafür, warum wir letztendlich keine 10-Kern-Modelle der Rocket-Lake-S-Prozessoren sehen. Die Chips wären einfach zu groß geworden und die Fertigung weniger wirtschaftlich.

Überraschenderweise nannte Intel die Anzahl der Transistoren und gab diese mit etwa 6 Milliarden an. Ein Ryzen 5800X mit acht Kernen, also einem CCD und einem IOD, kommt auf 6,24 Milliarden Transistoren. Der doppelte CCD-Ausbau bringt es auf 10,4 Milliarden Transistoren und eine Gesamtfläche von 286,4 mm².

| Transistordichte | |

| TSMC 16 nm | 28,2 MT/mm² |

| TSMC 14 nm | 52,5 MT/mm² |

| TSMC 7 nm | 91 MT/mm² |

| TSMC 5 nm | ? 170 MT/mm² |

| TSMC 3 nm | ? 300 MT/mm² |

| Intel 14 nm | 37,5 MT/mm² |

| Intel 10 nm | 101 MT/mm² |

| Intel 7 nm | ? 200 bis 250 MT/mm² |

Da Intel nun zum gefühlt x-ten Mal auf die Fertigung in 14 nm setzt, stellt sich natürlich die Frage wie schlagkräftig Intel damit im Vergleich noch ist. Einzelne Kerne und 5,3 und alle Kerne auf bis zu 5,1 GHz heben zu können, zeigt schon einmal, wie ausgereift Intels Prozess geworden ist. Natürlich aber kann Intel im Hinblick auf die Transistordichte nicht mehr mithalten und letztendlich ist Rocket Lake-S mit etwa 270 mm² schlichtweg auch zu groß. AMD realisiert auf dieser Fläche 16 Kerne.

Aber die 14 nm von Intel gegen die 14 nm von TSMC zu vergleichen (analog dazu 10 vs 10 nm und 7 vs 7 nm) ist auch nicht so ohne weiteres möglich. Vielmehr sollte man auf die Transistordichte schauen. Intels Fertigung in 10 nm liegt hier in etwa auf Niveau von 7 nm bei TSMC. Wenn Intel 2022/23 mit 7-nm-Chips um die Ecke kommt, haben diese eine Transistordichte die über dem liegt, was TSMC in 5 nm fertigt. Aber das Thema bekommt zusätzliche Komplexität, wenn man mit einbezieht, dass ein Chip nicht homogen mit einer Transistordichte gefertigt wird, sondern es Bereiche gibt, die dichter gepackt sind und solche, die weniger dicht bleiben müssen, um beispielsweise größere Ströme und Spannungen zu ermöglichen.

Neue Chipsätze, alter Sockel

Die Bereits im vergangenen Jahr vorgestellte LGA1200-Plattform ist grundsätzlich zu den neuen Rocket-Lake-S-Prozessoren kompatibel. Auch haben die meisten Mainboard-Hersteller bereits mit den 400-Series-Mainboards (vor allem aber denen mit Z490-Chipsatz) sichergestellt, dass diese PCI-Express 4.0 unterstützen. PCI-Express 4.0 ist eine der wichtigsten Funktionen der neuen Prozessoren. Zugleich erhöht Intel die Anzahl der Lanes von 16 auf 20, sodass neben einer Grafikkarte auch eine NVMe-SSD direkt an den Prozessor angebunden werden kann.

Aber man muss hier eben genau schauen, welcher Hersteller welches seiner Modelle schon im vergangenen Jahr auf PCI-Express 4.0 ausgelegt hat. Hinzu kommt, dass auch dann genau prüfen muss, welcher der verfügbaren M.2-Slots derjenige ist, welcher direkt an den Prozessor angebunden ist.

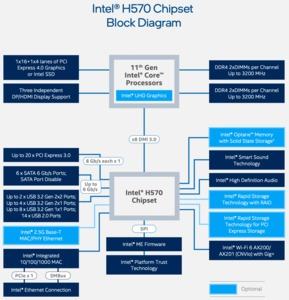

Eine weitere Neuerung der Plattform ist die Anbindung zwischen Prozessor und Chipsatz. Diese erfolgt beim Z590- und H570-Chipsatz über nun acht statt nur vier DMI-3.0-Links. Die Transferrate verdoppelt sich demnach auf 8 GT/s (7,86 GB/s), was den Flaschenhals in der Anbindung von Prozessor und Chipsatz aufheben soll. Alle Rocket-Lake-S-Prozessoren unterstützen die x8-DMI-3.0-Anbindung, aufseiten der Chipsätze sind es eben der Z590 und H570, während der B560 und H510 dies nicht bieten.

Kompatibilität 10/11. Core / 400/500-Series Chipsätze

Ein wichtiger Punkt der Plattform und für die Chipsätze ist, dass Intel das Overclocking für den Speicher nun für alle Prozessoren und auch alle Chipsätze freigibt. Allerdings gibt es auch hier einige Einschränkungen in Form des integrierten Speichercontrollers der Rocket-Lake-S-Prozessoren (IMC), auf die wir noch genauer eingehen werden.

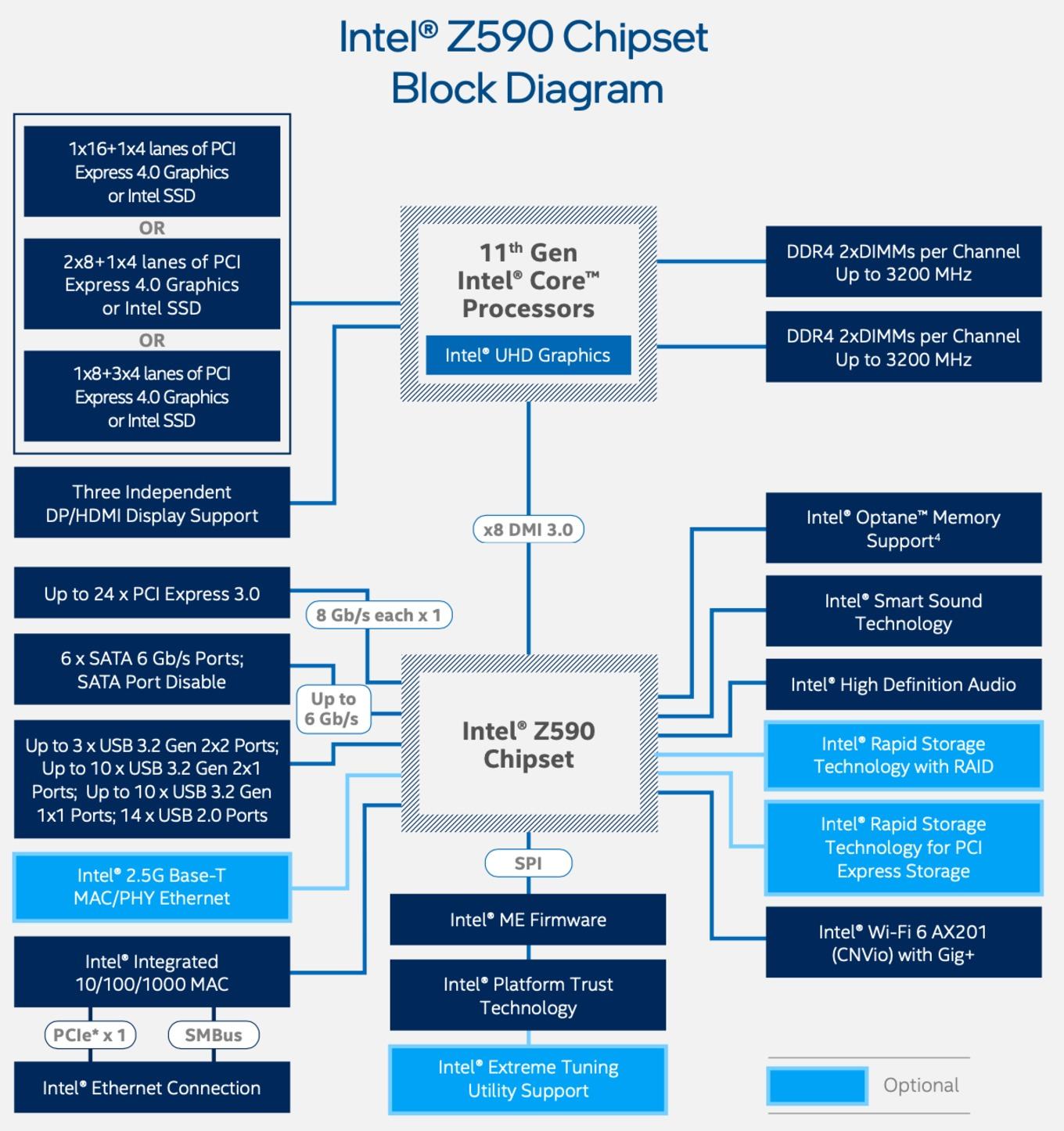

Für die meisten Spieler dürfte der Z590-Chipsatz der interessanteste sein, wenn der Kauf eines neuen LGA1200-Mainboards ins Haus steht. Die 20 PCI-Express-Lanes des Prozessors können vom Mainboard-Hersteller in 1x 16 + 1x 4, 2x 8 + 1x 4 oder 1x 8 + 3x 4 Lanes aufgeteilt werden. Der Chipsatz selbst bietet bis zu 24 PCI-Express-3.0-Lanes. Intel hat die Unterstützung von PCI-Express 4.0 also nicht so konsequent umgesetzt, wie dies bei AMD aktuell der Fall ist. Weiterhin bietet der Z590-Chipsatz bis zu 6x SATA, 3x USB 3.2 Gen 2x2, 10x USB 3.2 Gen 2x1, 10x UDB 3.2 Gen 1x1 und 14x USB 2.0. Hinzu kommen 2.5G Base-T, Wi-Fi 6 und Funktionen wie die Unterstützung von Optane Memory, Smart Sound, Rapid Storage und das neue Intel Extreme Tuning Utility.

Der H570-Chipsatz bietet eine fixe Konfiguration der PCI-Express-Lanes in Form von 1x 16 + 1x 4. Auch hier findet die Anbindung zwischen Chipsatz und Prozessor über x8 DMI 3.0 statt. Der Chipsatz selbst bietet dann 20 PCI-Express-3.0-Lanes – vier weniger als der Z590. Mit 2x USB 3.2 Gen 2x2, 4x USB 3.2 Gen 2, 8x USB 3.2 Gen 1 und 14x USB 2.0 stehen ein paar Anschlussmöglichkeiten weniger zur Verfügung. Dies gilt nicht für 6x SATA und das 2.5G Base-T Ethernet. Ist ein entsprechender PHY auf dem Mainboard verbaut, steht auch hier Wi-Fi 6 zur Verfügung – ebenso wie einige weitere Intel-Funktionen (Rapid Storage, Optane Memory, Smart Sound, etc.). Ein Overclocking des Prozessors wird von Mainboards mit H570-Chipsatz nicht unterstützt.

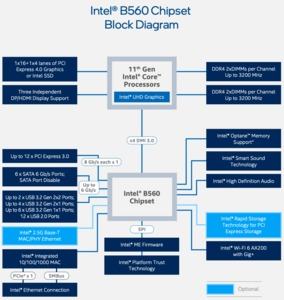

Der dritte Chipsatz-Kandidat, den wir uns genauer anschauen wollen, hört auf den Namen B560. Hier werden die Anschlussmöglichkeiten noch einmal etwas weiter eingeschränkt. Der Chipsatz stellt nur noch 12 PCI-Express-3.0-Lanes zur Verfügung und ist auch nur noch per x4 DMI 3.0 an den Prozessor angebunden. Auch bei den USB-Anschlüssen müssen weitere Abstriche gemacht werden, nicht aber bei den Netzwerkanbindungen.