Werbung

Während TSMC derzeit vor allem für Apple zahlreiche Chips in 5 nm fertigt, werden nun Probleme ins Samsungs V1-Produktionsline am Hwasung Campus bekannt. Ein Insider berichtet über eine schlechtes Ausbeute in der durch EUV-Lithografie unterstützten Fertigung. Bereits mehrfach gab es solche Meldungen, die nun durch einen Bericht bei Business Korea noch einmal erneuert werden. Weniger als die Hälfte der Chips auf einem Wafer sind demnach vollständig funktionsfähig. In der Massenproduktion werden Werte von 95 % angepeilt.

Welche Produkte betroffen sind und wo das Problem genau liegt, darüber macht der Bericht allerdings keine Angaben und bleibt nur ein diffuses Gesamtbild. Fertiger wie Samsung, TSMC und Intel sprechen aber auch nicht gerne über konkreten Zahlen zur Ausbeute, schon gar nicht über Probleme oder erst dann, wenn es kein zurück mehr gibt – siehe Intels Probleme mit der Fertigung in 10 nm. Insofern verwundert es nicht, dass die Informationslage recht dünn ist.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Aber zumindest die Kunden scheinen schon umzusteuern: Qualcomm ist einer der Großkunden bei Samsung und lässt unter anderem den Snapdragon 888 in 5LPE fertigen. Die Nachfolger 895 und 895+ soll Qualcomm nun auf Samsung und TSMC aufgeteilt haben.

Bei TSMC hingegen scheint es besser zu laufen. Bereits im Sommer des vergangenen Jahres, also mitten in der Massenproduktion der ersten in 5 nm gefertigten Chips, gab man eine Defektrate an, die geringer als die der Fertigung in 7 nm zum gleichen Zeitpunkt gewesen sein soll. Etwa 0,1 bis 0,11 Defekte pro Quadratzentimeter gab TSMC damals an und erwartete, dass diese Zahl in den kommenden Monaten weiter sinken würde.

Inzwischen dürfte man auf einem deutlich niedrigeren Niveau sein. Zum TSMC Technology Symposium Anfang Juni sprach man wieder über die Defektrate der N5-Fertigung, nannte allerdings keine konkreten Zahlen. Offenbar kann man die Ausbeute weiterhin deutlich über dem Niveau halten, was man jemals mit der Fertigung in 7 nm erreichen konnte, bzw. erreicht hat. Zurückgeführt wird dies auf den erhöhten Einsatz der EUV-Lithografie, die weniger Schritte in der Fertigung notwendig macht, was das Risiko für Defekte reduzieren sollte.

Solche Schlussfolgerungen sind allerdings immer schwierig, denn eigentlich wollte auch Samsung genau dies durch den vermehrten Einsatz der EUV-Lithografie bewerkstelligen, scheiterte aber offenbar auf dem Weg dahin. Die Komplexität im Aufbau einer neuen Fertigung ist nicht unerheblich. Samsung eröffnete das besagte Werk im Februar 2020 und begann damit die Fertigungsstraße für 5 nm einzurichten. Es dauert Monate, bis alle Fertigungsschritte entsprechend eingerichtet sind. Irgendwann sollte die Fertigung dann jedoch den Punkt erreichen, in dem die Ausbeute einen gewissen Schwellwert überschreitet – idealerweise mit der Massenproduktion der ersten Chips für die Endkunden. In der Folge sorgen kleinere Verbesserungen dann dafür, dass eine Ausbeute von 90+ % erreicht wird.

Die Entscheidung für eine bestimmte Technik oder Materialen kann aber auch dafür sorgen, dass diese Hürde niemals genommen wird. Intels 10-nm-Probleme der ersten Generation (pre SuperFin Technology / 10nm+) sollen auf eine solche Einbahnstraße in der Entwicklung zurückzuführen gewesen sein.

Vermeintliche Probleme in der 5-nm-Fertigung sind nicht die einzige Hiobsbotschaft, die uns von Samsung erreicht. Auch die eigentlich schon für 2022 geplanten Multi Bridge Channel FETs, bzw. GAA-Transistoren (Gate all Around) verschieben sich offenbar auf 2024.

Update:

Es gibt weitere Details zur verschobenen Fertigung mit GAA-Transistoren. Offenbar wurde die geplante Massenproduktion von 3GAE (3 nm Gate All Around Early) komplett eingestellt und ist von der Roadmap verschwunden. Stattdessen wird ab 2023 das HVM (High Volume Manufacturing) für 3GAP (3 nm Gate All Around Plus) aufgeführt.

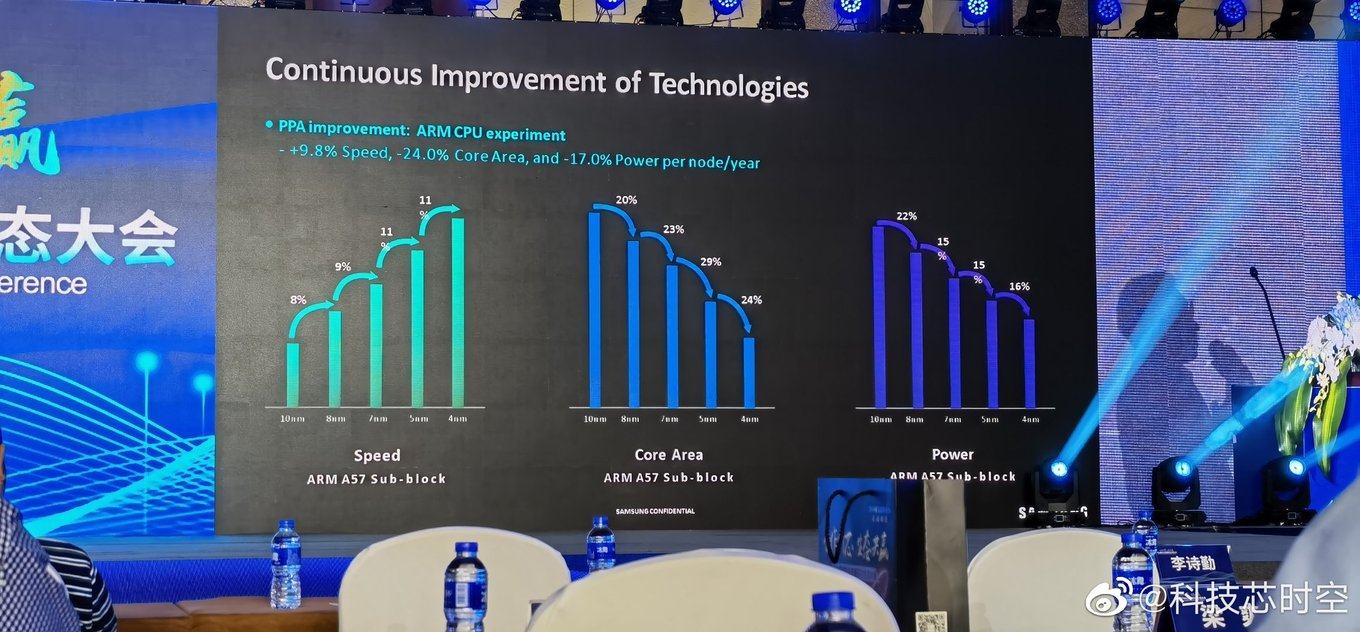

Samsung veröffentlichte auch ein paar Zahlen zur Fertigung in 4LPP (4 nm Low Power Plus). So soll die Leistung bei gleicher Leistungsaufnahme um 11 % steigen, die gleichem Takt die Leistungsaufnahme aber auch um 16 % reduziert werden können. Zugleich können gewisse Strukturen im Vergleich zur Fertigung um 5 nm um 24 % kleiner gefertigt werden.