Werbung

Bereits in der vergangenen Woche sind wir auf die zukünftigen Entwicklungen bei TSMC in der Fertigung eingegangen. So wird der weltweit größte Auftragsfertiger die rückseitige Versorgung bei den Chips erst mit der Fertigung in A16 in Produktion bringen und der 2-nm-Prozess soll durch NanoFlex effizienter werden.

Doch es gibt auch Neuigkeiten aus anderen Bereichen. In den letzten zwei Jahren spielte vor allem das Packaging eine zunehmend wichtigere Rolle, denn neben der Anbindung von schnellem HBM gehen die Chiphersteller vermehrt dazu über, mehr als einen Compute-Chip im Package unterzubringen, um die Rechenleistung weiter zu steigern. In der Komplexität steht das Packaging mit seinen diversen Verfahren der Wafer-Belichtung in nichts nach.

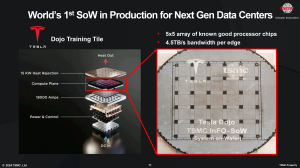

Sytem on Wafer heißt eine Technik, bei der die einzelnen Chips auf dem Wafer nicht mehr getrennt und auf einem Package untergebracht werden, sondern hier ist der komplette Wafer bereits der Chip. Cerebras hat vor einigen Wochen die dritte Generation seiner Wafer Scale Engine vorgestellt, die genau das ist: 84 Chips auf einem Wafer, die weiterhin zusammenarbeiten. Tesla hat mit dem D1-Chip etwas sehr ähnliches entwickelt. Beide Unternehmen setzen dabei auf TSMC als Fertiger.

Einen Nachteil haben die Systeme auf Basis von InFO-SoW (Integrated Fan-Out) und System on Wafer jedoch: Sie sind maßgeblich auf den SRAM angewiesen, der sich mit auf dem Wafer befindet, wenngleich Cerebras auch eine externe DRAM-Erweiterung ermöglicht. Aber dieser Speicher befindet sich eben nicht mit auf dem Wafer.

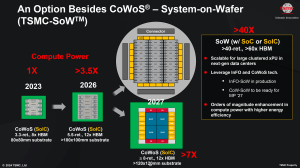

Eben diese Limitierung soll ab 2027 eine Technik namens CoW-SoW umgehen. Nicht nur wird TSMC hier komplette System auf Wafer-Ebene fertigen können, auch wird es möglich sein, 3D-Komponenten wie eben HBM zu integrieren. Laut TSMC werden Techniken wie (SoIC) System on Integrated Chips in den kommenden zwei Jahren an ihre Grenzen kommen. Compute-Chips mit zusammengenommen fast der sechsfachen Größe der einzelnen Chips zusammen mit 12 HBM-Chips lassen sich wohl noch realisieren, danach aber muss über anderen Lösungen nachgedacht werden.

Große Compute-Dies, welche das aktuelle Limit bei der Größe einzelner Chips ausnutzen (wir reden hier von 25x 800 mm²) und die Integration von HBM4 will TSMC ab 2027 anbieten können. Dies würde das Limit beim On-Die-Speicher deutlich anheben, denn hier sprechen wir aktuell von etwa 44 GB die beispielsweise Cerebras für die WSE-3 umgesetzt hat. HBM4 wird schon mit einem Chip eine höhere Kapazität bieten können.

Bis 2027 wird TSMC die technische Umsetzung von CoW-SoW sicherlich noch etwas genauer ausführen. Da es eben noch einige technische Einschränkungen gibt, waren bisher auch nur zwei Kunden an einer konkreten Umsetzung von SoW interessiert. Diese beiden haben wir mit Cerebras und Tesla bereits genannt.