Werbung

Auf dem Samsung Foundry Forum hat der südkoreanische Großkonzern und Chiphersteller einige Details zu seinen Plänen hinsichtlich der Fertigung in den kommenden Jahren verkündet. Unter anderem wurden zwei neue Prozess-Nodes SF2Z und SF4U angekündigt.

Mit SF2Z wird Samsung auf ein Backside Power Delivery Network (BSPDN) setzen. Bei Intel wird man diesen Schritt mit Intel 20A gehen und TSMC hat seine Pläne für eine BSPDN-Technik auf die A16-Fertigung verschoben. Allerdings ist BSPDN nicht gleich BSPDN. So geht TSMCs Super Power Rail (SPR) in der Integration einen Schritt weiter, als dies bei Intels PowerVia der Fall ist. Welche Umsetzung Samsung für SF2Z plant, ist nicht bekannt. Gegenüber SF2 soll SF2Z aber noch einmal eine deutliche PPA-Verbesserung (Power, Performance und Area) zu bieten haben. Vor allem HPC-Chips sollen davon profitieren. Die Massenproduktion in SF2Z ist für 2027 geplant.

Die zweite neue Prozess-Node ist SF4U. Es handelt sich dabei laut Samsung um eine 4-nm-Variante, die auf besonders hohe Volumina ausgelegt ist. Unter Einbeziehung einer optisches Shrinks sollen hier aber auch PPA-Verbesserung einfließen. Die Massenproduktion in SF4U ist bereits für 2025 angesetzt.

SF1.4, die erste Prozess-Node im Sub-2nm-Segment, liegt laut Samsung weiter im Zeitplan. Leistung und Ausbeute lägen innerhalb des erwarteten Bereichs und man geht weiterhin davon aus, dass die Massenproduktion in 2027 starten kann.

Für dieses Jahr steht zunächst einmal die Massenproduktion der zweiten Generation des SF3-Prozesses an. Diese soll in der zweiten Jahreshälfte beginnen. SF3 ist der erste Prozess bei Samsung, der auf GAA-Transistoren (Gate-all-around) setzt. Grundsätzlich fertigt man diesen bereits seit drei Jahren. SF3E/3GAE wurde aber zunächst für wenig komplexe Mining-Chips verwendet. Lange hielt sich zudem das Gerücht, dass die Ausbeute bei Samsungs SF3-Prozessen nur sehr gering ist. Erst in den letzten Monaten soll sich dieser Umstand deutlich gebessert haben, so dass Samsung auch immer wieder als Alternative zu TSMC genannt wurde.

Auf SF3 folgen wird im kommenden Jahr SF2 und SF2P. Auch hier richtet sich Samsung zunächst einmal eine kleinere SoCs für Smartphones und dergleichen. SF2X soll dann auch größere Chips für HPC- und AI-Beschleuniger fertigen können. Die Massenproduktion ist für 2026 geplant.

SF2Z mit BSPDN wird dann wie gesagt 2027 folgen und zeitgleich mit der Automotive-Variante SF2A an den Start gehen.

Packaging konzentriert sich auf AI-Beschleuniger

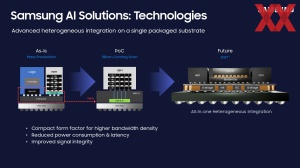

Ob Samsung in seinem Foundry-Business demnächst wieder einen Großkunden wird begrüßen können, hängt nun sicherlich davon ab, wie sich SF2Z und die weiteren Prozesse entwickeln. Aber auch beim Packaging will man sich nicht abhängen lassen und neben der aktuellen Methode mehrere Chips vertikal auf einem Substrat zu integrieren sowie auf neue Techniken setzen.

Als nächsten Schritt sieht man hier die Integration einzelner Komponenten, beispielsweise eines Speicher-Chips, direkt in das Substrat. Damit ließe sich die Signalintegrität und Leistungsdichte, sprich Bandbreite, noch einmal deutlich erhöhen. Für die entferntere Zukunft plant man dann auch ein Packaging mit komplexer Integration in diversen 2.5- und 3D-Ausprägungen.