Werbung

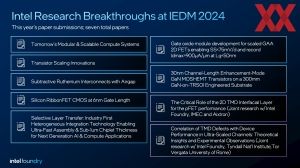

Auf dem diesjährigen IEEE International Electron Devices Meeting (IEDM) hat Intel über zahlreiche Neuentwicklungen in der Chipentwicklung in den Bereichen Advanced Packaging, der Skalierung der Transistordichte und bei den Interconnects gesprochen. Insgesamt hält Intel fast ein Dutzend Vorträge auf dem IEDM 2024, die sich mit den verschiedenen Bereichen beschäftigen.

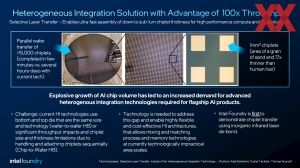

Eine der gezeigten Arbeiten beschäftigt sich mit dem sogenannten Hybrid Bonding einer Wafer auf der anderen. Dabei können kleine Chiplets mit der Größe von gerade einmal 1 mm² auf einen weiteren Chip aufgetragen und miteinander verbunden werden. Der Prozess dauert für mehr als 15.000 kleine Chiplets nur wenige Minuten und würde in einem klassischen "Face to Back"-Verfahren mehrere Stunden wenn nicht Tage dauern.

Auch im Handling ist ein Wafer to Wafer Hybrid Bonding flexibler, da hier die beiden Chiplets, die aufeinander positioniert werden, nicht die gleiche Größe haben müssen.

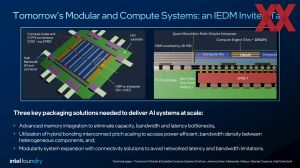

Darüber hinaus sieht Intel einen zunehmenden Trend nach hochmodularen Packages, bei denen verschiedene Komponenten im Package zusammengefasst werden. Bisher sind Compute-Chiplets gemeinsam mit I/O und Speicher im Einsatz, werden aber noch eher selten mit schnellen Netzwerkschnittstellen kombiniert. Dabei ist eine Speichererweiterung mit hoher Bandbreite und niedrigen Latenzen ebenso wichtig, wie dies auf Seiten der I/O-, bzw. Netzwerkanbindung der Fall ist. Dabei dürfte auch oben genanntes Wafer to Wafer Hybrid Bonding eine Rolle spielen.

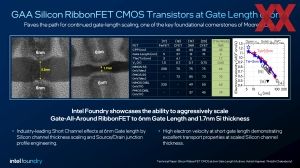

Fortschritte macht Intel auch bei den GAA RibbonFET, also den zugrundeliegenden Transistoren. Diese sollen inzwischen eine Gate-Länge von 6 nm erreichen. Die Channel-Breite konnte Intel auf 1,7 nm reduzieren. Wichtig ist dabei der Vergleich zu dein FinFETs, zu deren Gate-Länge man inzwischen aufgeschlossen hat, in der Channel-Breite aber sogar schon vorgelegt hat. An dieser Stelle der Vergleich zu den konkurrierenden CFETs:

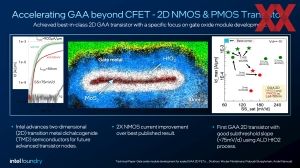

Complementary FETs (CFET) sind gefaltete N&P-MOS-Transistoren, die den Platzbedarf ebenfalls reduzieren sollen, ohne dabei jedoch in der Komplexität an GAA-Transistoren heranreichen zu müssen. Besonders High-Density SRAM-Zellen sollen davon profitieren und eine hohe Packdichte erreichen. Allerdings sind die CFET in anderen Charakteristika den GAA-Transistoren unterlegen.

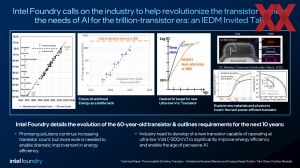

Geht man einen Schritt weiter, wird interessant was nach den CFET und GAA-Transistoren zu erwarten ist. Intel arbeitet hier an neuartigen 2D-Transistoren mit neuartigen Materialien und einmal mehr zeigt sich, dass in der Chipfertigung fast der komplette Baukasten der Elemente verwendet wird.

Während sich beim Advanced Packaging aktuell alles auf das Hybrid Bonding mittels Kupfer konzentriert, ist Intel schon auf der Suche nach neuen Methoden. Dabei zum Einsatz kommen soll Ruthenium als neues Material. Auch hier sei wieder der Baukasten der Elemente erwähnt, den man inzwischen fast vollständig ausschöpft. Es müssen aber auch nicht immer neuartige Materialien sein, denn bereits heute kommen in der Chipfertigung auch Luftspalte als konstruktives Element zum Einsatz.

Mit den entsprechenden Präsentationen auf dem IEDM werden wir gegebenenfalls noch weitere Details nachreichen – auch aus den Vorträgen anderer Hersteller.