Werbung

Auf der Hausmesse Direct Connect kündigt Intel einige Neuerungen aus dem Foundry-Geschäft an. Einmal mehr liegt der Fokus dabei auf der etablierten Prozess-Technik, die in Form von Intel 18A bereits seit Jahren im Raum steht und durchaus gute Vorzeichen vorzuweisen hat. Aber auch beim Packaging will Intel ein Big Player für externe Kunden werden – ebenfalls etwas, was über die vergangenen Monate beinahe wie ein Mantra immer wiederholt wurde.

Die nun folgenden Informationen haben wir Vorab von Intel erhalten. Heute und morgen wird Intel auf der Keynote und weiteren Sessions über einige weitere Details sprechen, auf die wir dann noch einmal genauer eingehen werden.

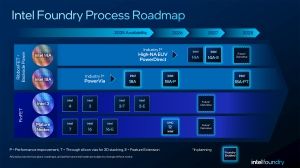

Intel 14A mit PowerDirect als nächster Schritt

Konkret auf der Direct Connect angekündigt wird, dass Intel 14A, der nächste Prozessschritt nach Intel 18A, bereits aktiv gegenüber potentiellen Kunden beworben wird. Vorgestellt wurde dieser Fertigungsschritt Intel 14A sowie Intel 10A und die Optimierungsschritte E (Enhanced), P (Performance) und T (TSV-optimiert) bereits im vergangenen Jahr. Eine frühe Version des Process Design Kit (PDK) für Intel 14A steht nun zur Verfügung und kann von Kunden genutzt werden, um Chipdesigns entsprechend anzupassen. Laut Intel haben einige Kunden bereits ihr Interesse bekundet, Test-Chips in Intel 14A fertigen zu lassen.

Intel 14A wird neben einer höheren Transistordichte mit PowerDirect eine Weiterentwicklung der PowerVia-Technologie (Intels Name für eine Umsetzung eines Backside Power Delivery Networks, BSPDN) zu bieten haben. Zu den genauen Details erhoffen wir uns weitere Informationen im Rahmen der Veranstaltung, bei der wir zugegen sind.

Intel 18A weiterhin im Plan und erweitert um Intel 18A-PT

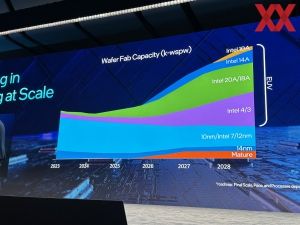

Aktuell befindet sich Intel in der sogenannten Risk Production erster Chips in Intel 18A. Diese hatte man bereits vor einigen Wochen auf der Vision-Konferenz prominent bekundet. Die Massenproduktion erster (eigener) Chips erfolgt in Form des Compute Tiles für Panther Lake später in diesem Jahr – vermutlich der zweiten Jahreshälfte.

Die ersten Chips in Intel 18A werden in der Fab D1 bei Portland, US-Bundesstaat Oregon, gefertigt und hier läuft auch die erwähnte Risk Production. Bereits vor einigen Wochen wurde bekannt, dass auch in der Fab 52 in Arizona ein sogenannter Hot-Lot vollzogen wurde. Dabei handelt es sich um eine Fertigung auf Wafern, die priorisiert die einzelnen Fertigungsschritte durchlaufen. Nach Portland wird dann später auch Arizona in die Fertigung von Chips in Intel 18A einsteigen.

Noch immer aber fehlt es an einem Großkunden für die Fertigung in Intel 18A. Custom-Designs der Xeon-Prozessoren für Amazon sind zwar ebenso wie das Departement of Defense bereits offiziell genannt worden, ein Kunde wie Broadcom, Marvell oder gar NVIDIA wäre für das Foundry-Geschäft aber sicherlich der Korkenöffner.

Intel hat aber auch bereits eine Weiterentwicklung zu Intel 18A zu bieten. Analog zu den P-Schritten bei TSMC (N5P, N4P, N3P) will man mit Intel 18A-P eine auf verbesserte Leistung ausgelegte Variante von Intel 18A auflegen. Damit will Intel neue Kunden für die Fertigung gewinnen. Erste Wafer, welche Intel 18A-P verwenden sollen bereits die Fabs durchlaufen. Ob bisher nur eigene Produkte und wenn ja welche Intel 18A-P verwenden werden, ist nicht bekannt. Die EDA-Partner (Electronic Design Automation) arbeiten bereits an der Anpassung ihrer Designs auf das neue Angebot.

Neu ist Intel 18A-PT. Dieser angepasste Prozess soll einerseits die Verbesserungen in der Leistung beinhalten, kann aber auch mit Foveros Direct 3D und damit einem Hybrid Bonding mit einem Bump Pitch von 5 µm kombiniert werden. Intel 18A-PT wird allerdings erst 2027 zur Verfügung stehen, während Intel 18A und 18A-P noch in diesem bzw. nächstem Jahr selbst verwendet und externen Kunden angeboten werden können.

Im Hinblick auf die Zusammenarbeit mit UMC verkündet Intel zudem, dass ein erstes Tape-Out im 16-nm-Prozess erfolgt ist und man mit Kunden bereits am 12-nm-Prozess arbeite.

Zum Packaging soll es im Verlaufe der Veranstaltung noch genauere Informationen geben. In der Keynote genannt wurden EMIB-T als schon bekannte Lösung für die Anbindung von HBM sowie die neuen Varianten Foveros-R und Foveros-B.