Werbung

Einen Prozessor und eine GPU in ihren Aufgaben und Ressourcen in mehrere Chips aufzuteilen hat AMD aus technologischer Sicht sicherlich einen Vorteil verschafft. Mit dem aufgestapelten SRAM (3D V-Cache) des Ryzen 5 5800X3D und den Milan-X-Prozessoren wurde dann der nächste Schritt in dieser Chiplet-Strategie gemacht. Die nächste Ryzen- und EPYC-Generation mit dem zusätzlichen Cache steht ebenfalls schon in den Startlöchern.

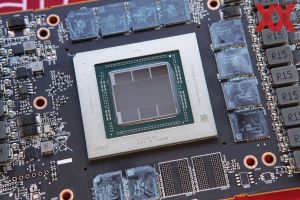

Dass sich Chiphersteller auch die Lösungen der Konkurrenz anschauen, ist in dieser Branche normal, denn schließlich will man wissen, auf welchem technologischen Stand die Konkurrenz ist. Der für IBM tätige Halbleiteringenieur Tom Wassick hat sich eine Radeon RX 7900 XT einmal genauer angeschaut und dabei in einer ersten Stufe auf ein 3D-Röntgengerät zurückgegriffen. Mit der Radeon-RX-7900-Serie ist AMD auch bei den GPUs im Endkunden-Segment erstmals auf eine Chiplet-Strategie umgestiegen und hat ein Package entwickelt, welches aus einem zentralen Graphics Chiplet Die (GCD) und mehreren Memory Chiplet Dies (MCD) besteht.

Offenbar gibt es auf den MCDs ähnliche "keep out zones" (KOZ) wie auf den CCDs der Prozessoren. Diese KOZ werden dann für die internen Verbindungen genutzt, wenn auf den CCD das SRAM-Chiplet aufgesetzt wird.

Die Ähnlichkeiten der KOZ sind aber nicht nur in deren Dimensionen vorhanden, sondern offenbar auch im Abstand der dort vorhandenen Kontakte (Pitch). Dieser liegt laut Wassick bei 17 bis 18 µm und entspricht somit dem Abstand, den wir von den CCDs der Prozessoren kennen.

Dass AMD auch bei den Grafikkarten an einer Möglichkeit arbeitet, den Speicher bzw. Cache in seiner Kapazität weiter zu erhöhen dürfte nicht sonderlich überraschend sein. Alle Hersteller arbeiten daran, eine möglichst große Speichermenge möglichst nahe und damit schnell an den eigentlichen Recheneinheiten zu platzieren. Die nach dem Grafikspeicher aktuell wohl einfachste Lösung (sowohl in der technischem Umsetzung sowie den Kosten) ist der Einsatz von HBM. Ein Cache verfügt aber noch einmal um eine um ein Vielfaches höhere Bandbreite. Für den zukünftigen Instinct-MI300-Beschleuniger will AMD 128 GB an HBM3 einsetzen. Die aktuellen Instinct-MI250-Beschleuniger kommen mit ihren 128 GB HBM2e auf eine Speicherbandbreite von 3.276,8 GB/s.

Vergleicht man dies mit dem Infinity Cache der RDNA-3-Architektur, so realisiert AMD hier mehr als 5 TB/s an Speicherbandbreite zwischen dem zentralen GCD und den sechs MCDs. Diese bieten auf einer Chipfläche von 37,5 mm² jeweils 16 MB an Speicher. Mittels eines zusätzlichen SRAM-Chips könnte AMD dies auf 70 MB pro MCD aufstocken. Bei den Radeon-Karten stellt sich aber die Frage nach der Sinnhaftigkeit. Denn die Effektivität der Hit Rate nimmt ab einer gewissen Kapazität nicht mehr signifikant zu und lässt eine solch teure Technik daher nur schwer rechtfertigen. Im Datacenter-Umfeld können derart große und vor allem schnelle Caches aber gefragter sein und womöglich hat AMD an dieser Stelle bereits heute eine Technik getestet, die man aber erst viel später einsetzen wird.

Mittlerer MCD ist nur ein Dummy

Darüber hinaus ist nun auch bekannt, welcher der sechs MCDs bei der Radeon RX 7900 XT abgeschaltet ist.

Das Package besteht natürlich bei beiden Karten, sowohl der Radeon RX 7900 XTX wie auch der Radeon RX 7900 XT, aus einem GCD und sechs MCDs, bei der Radeon RX 7900 XT ist einer der MCDs aber nur ein Stück blankes Silizium, also kein vollwertiger Speicher-Chiplet. Im Falle der von Wassick untersuchten GPU war einer der mittleren Chips nur der Dummy. Dieser wird in dieser Form verbaut, damit der Kühler weiterhin eine möglichst große und plane Oberfläche hat, auf der er aufliegen kann.