Werbung

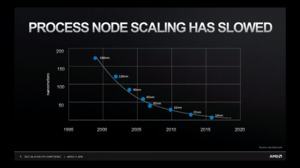

Auf der High Performance Computing Conference gab Forrest Norrod, Senior Vice President und General Manager der Datacenter-Gruppe bei AMD, eine interessante Präsentation. Dabei ging er zunächst einmal auf die aktuellen Herausforderungen im Chipdesign ein. Diese liegen laut AMD in der Fertigung immer kleinerer Strukturen bei gleichzeitig immer größeren Anzahl an Transistoren und damit einer erhöhten Komplexität sowie der Tatsache, dass die Leistung aktueller Prozessoren kaum noch auf Steigerungen des Taktes zurückzuführen sind, sondern vielmehr auf spezielle Hardwarefunktionen, die bestimmte Berechnungen beschleunigen, eine drastische Erhöhung der Anzahl der Kerne pro Die und schlussendlich auch eine bessere Software-Unterstützung.

Natürlich lässt sich Norrod dabei nicht die Gelegenheit entgehen, auf die aktuellen Ryzen-Prozessoren mit bis zu acht Kernen (und zukünftig womöglich bis zu 16 Kernen) sowie die EPYC-Prozessoren der 3. Generation alias Rome mit bis zu 64 Kernen im Chiplet-Design, zu verweisen.

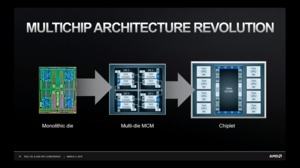

Dabei stellt Norrod die Vorteile eines Chiplet- und MCM-Designs noch einmal heraus: Anstatt eines einzelnen Dies mit 700 - 800 mm², besteht ein günstigeres und einfacher zu fertigendes MCM-Design aus bis zu vier kleineren Chips und bringt damit ebenfalls 800 mm² in einem Package unter – das Chiplet-Design macht schlussendlich sogar mehr als 1.000 mm² in einem Package möglich, was mit klassischen monolithischen Chips wirtschaftlich nicht umzusetzen wäre.

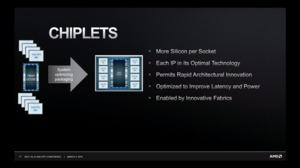

Zudem beschreibt AMD die Vorteile des Chiplet-Designs, wie es Intel für die Foveros getaufte Strategie bzw. Technik ebenfalls vorsieht. Jeder Chip im Chiplet-Design, wird in der für das Design idealen Fertigung ausgeführt. Im Falle der EPYC-Prozessoren der 3. Generation sieht dies eine Fertigung der CPU-Chiplets in 7 nm vor, während der I/O-Die in 14 nm gefertigt wird.

3D-Speicher soll direkt an die CPU angebunden werden

Hinsichtlich der Rechenleitung soll das Chiplet-Design die technische Grundlage für weitere Entwicklungen sein. Neben immer schnelleren und mehr CPU-Kernen sowie schnelleren Interconnects spielt aber auch der Speicher eine bzw. dessen Anbindung eine entscheidende Rolle. AMD verweist an dieser Stelle an die bis zu 32 GB HBM2, die bei den GPUs bereits im 2,5D-Verfahren angebunden werden. Man selbst arbeitet aber bereits an technischen Verfahren, um DRAM und SRAM per 3D-Verfahren direkt auf der Compute-Hardware (AMD bleibt hier wohl bewusst sehr vage) unterzubringen.

Doch bis dies in der Praxis eine Rolle spielen wird, wird man noch einige Hürden nehmen müssen. Vor allem wäre da die Abwärme ein Problem, denn mehrere hundert Watt an Abwärme lassen sich in 3D-gestapelten Chips nur schwer abführen. Aus diesem Grund plant Intel den Einsatz von Foveros zunächst nur im Lakefield-SoC mit einem Sunny-Cove-Kern sowie vier Atom-Kernen mit eine Standby-Leistung von gerade einmal 2 mW.

Eine konkrete Ankündigung hat AMD aber nicht zu machen, was wohl auch daran liegt, dass bis wir ein echtes 3D-Design im HPC-Segment sehen werden, noch einige Hürden zu nehmen sind. Stattdessen verweist AMD auf die vorrangige Notwendigkeit nach schnelleren (und offenen) Interconnects sowie eine besseren Software-Unterstützung der aktuell verfügbaren Hardware.

Die ganze Präsentation gibt es bei YouTube zusehen:

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen