Werbung

Die Zukunft scheint den Chiplet-Designs zu gehören. AMD wird dazu mit den Ryzen-Prozessoren der dritten Generation und den EPYC-Prozesoren der zweiten Generation erste Produkte auf den Markt bringen und die Erfahrungen, die AMD bei den Zen-Prozessoren gemacht hat, will man in zukünftigen RDNA-Architekturen für die Grafikkarten umsetzen. Auch Intel arbeitet bei den Prozessoren in diese Richtung und das, was Intel bisher zur Xe-Architektur gezeigt hat, spricht ebenfalls für einen modularen Aufbau des Chips. Zuletzt veröffentlichte NVIDIA ein Forschungspapier zu einem MCM-basierten AI-Beschleuniger.

Auf dem VLSI-Symposium in Kyoto, Japan, zeigte nun auch TSMC seine Umsetzung für ein Chiplet-Design. WikiChip war vor Ort und hat die dort erhaltenen Informationen aufgearbeitet. Dabei sollten auch einige konkrete Vorgaben mit einbezogen werden, die im Fokus stehen sollen und die zeigen, dass ein Chiplet-Design auch im HPC-Segment sinnvoll umgesetzt werden kann:

- es sollten vier ARM-Kerne mit einem Takt von 4 GHz oder mehr verwendet werden

- es sollte ein bidirektionaler Interconnect in Mesh-Topologie verwendet werden, der ebenfalls 4 GHz und mehr erreichen sollte

- die eigene Chip-on-Wafer-on-Substrate (CoWoS) Packaging-Technologie und der Low-voltage-In-Package-Interconnect sollten verwendet werden und 8 GT/s bei < 1 pJ/Bit erreichen

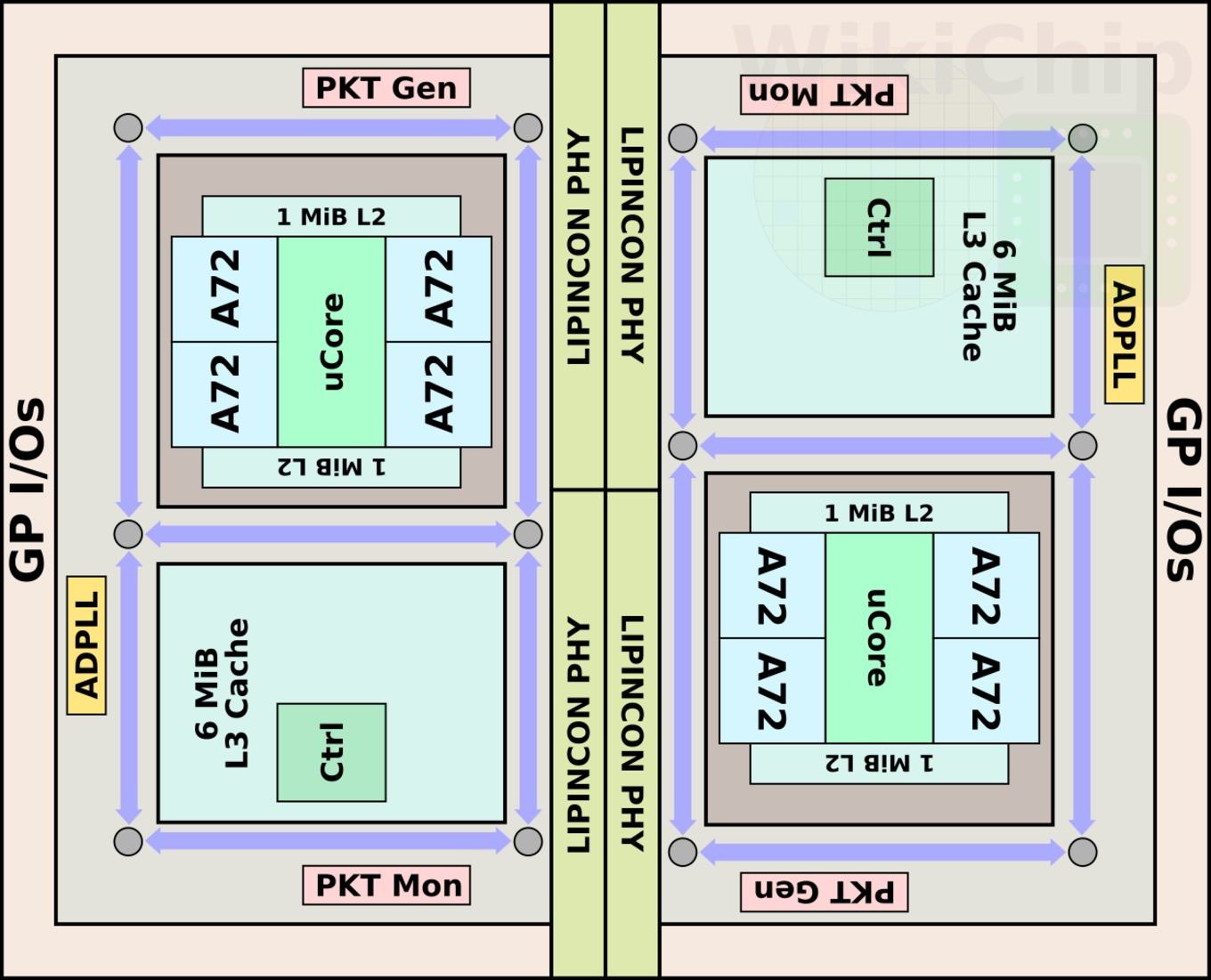

TSMC hat sich für einen Dual-Chiplet-Prozessor entschieden. Dieser verwendet pro Chiplet jeweils vier ARM Cortex-A72-Kerne, die in 7 nm gefertigt werden. Das Design wurde derart ausgelegt, dass die beiden ARM-Kerne einen Takt von 4 GHz oder mehr erreichen. Den vier ARM-Kernen stehen 2x 1x MB L2-Cache zur Verfügung. Hinzu kommen 6 MB L3-Cache. Das gesamte Package besteht aus 15 Layern. Zwei dieser Chiplets sollten letztendlich auf einem Substrat in wiederum einem größeren Package untergebracht werden. Dieser Aufbau beschreibt dann auch die Herausforderungen an die On-Chip- und Off-Chip-Interconnects.

Doch zunächst konzentrierte sich TSMC auf eine möglichst hohe Leistung der ARM-Kerne und eine gute Skalierung des Taktes über die Spannung. Mit der 7-nm-Fertigung hat TSMC schon gute Erfahrungen gemacht und mit AMD hat man auch einen Kunden, der große CPUs und GPUs hier in 7 nm fertigen lässt.

| Frequenz | 2,8 GHz | 3,0 GHz | 3,5 GHz | 4,0 GHz | 4,2 GHz |

| Takt | 0,775 V | 0,825 V | 0,95 V | 1,20 V | 1,375 V |

Beim Takt wurden bis zu 4,2 GHz erreicht, allerdings waren dazu auch 1,375 V notwendig. Bei 2.8 GHz reichten 0,775 V aus.

Die Interconnects und das Packaging

TSCM verwendet einen bidirektionalen Interconnect in Mesh-Topologie für die Verbindung innerhalb des Chiplets für vier ARM-Kerne und den L3-Cache. Sechs verteilte Flip-Flop-Mesh-Stations kümmern sich um diese Interconnect-Struktur. Realisiert wird darüber ein 1.968 Bit breiter Bus, der mit Taktraten zwischen 2,0 und 5,2 GHz arbeiten kann. Damit ist eine Datenrate von 1,2 TB/s möglich.

Die zwei Chiplets kommunizieren über ein den Low-voltage-In-Package-Interconnect (LIPINCON) miteinander. Dazu verfügt jedes Chiplet über jeweils zwei PHYs (physikalische Ebene im OSI-Modell). Die einzelnen Verbindungen sind unidirektional realisiert. Eine stellt den Master für die CPU-Kommunikation zum L3-Cache während die zweite als Slave in die andere Richtung arbeitet. Jeder PHY kann dann 2:1 Multiplexing eine Datenrate von 8 GB/s erreichen.

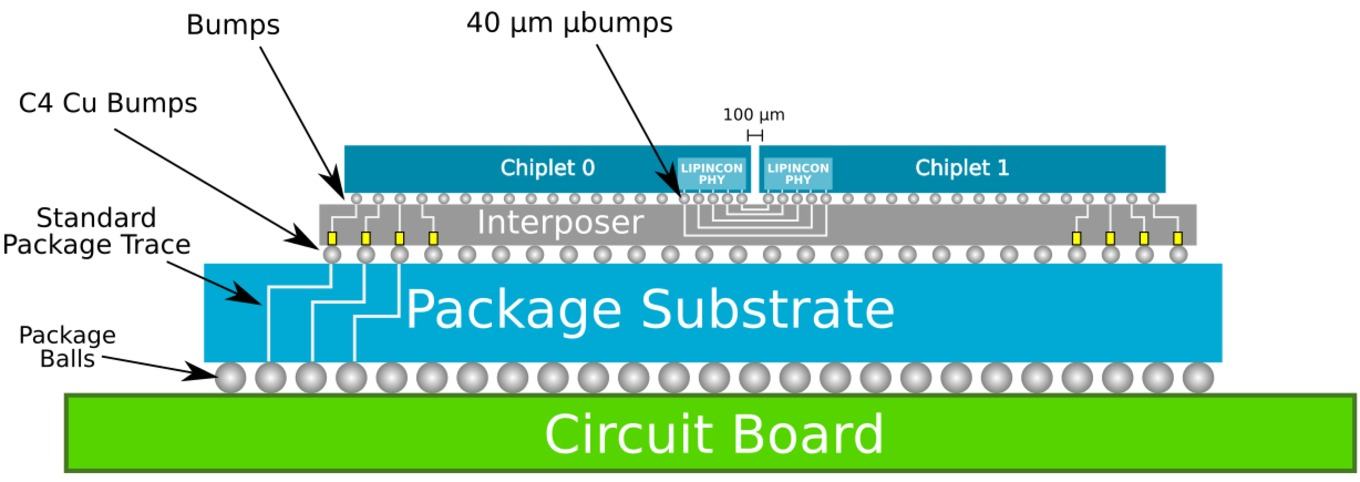

Das Packaging ist für ein Chiplet-Design ebenfalls wichtig. TSMC beschreibt hier die eigene Chip-on-Wafer-on-Substrate (CoWoS) Packaging-Technologie. Ein Package-Substrat stellt die Verbindung zwischen dem Package und dem Logicboard her. Hier kommen die vergleichsweise großen BGAs (Ball Grid Array) zum Einsatz. Auf dem Substrat sitzt der Silizium-Interposer, der über sogenannte C4-Bumps aus Kupfer eine Verbindung zum Substrat herstellt.

Die zwei Chiplets sitzen auf dem Interposer und haben einen Abstand von gerade einmal 100 µm zueinander. Über Micro-Bumps mit einem Abstand von gerade einmal 40 µm werden die LIPINCON-PHYs miteinander verbunden. Zum Vergleich: AMD setzt für seine neuen 7-nm-Dies bei den RYZEN- und EPYC-Proezssoren auf Bumbs mit einem Abstand von 130 µm zueinander.

| AMD | Intel | TSMC | |

| Packaging | MCM | EMIB | CoWoS |

| Channel | - | 1 mm | 500 µm |

| Chiplet-Bumbs | 130 µm | 55 µm | 40 µm |

| Interconnect | Infinity Fabric (IF) | Advanced Interface Bus (AIB) | LIPINCON |

| Datenrate | 10,6 GT/s | 2 GT/s | 8 GB/s |

| Leistungsaufnahme | 2 pJ/Bit | 1,2 pJ/Bit | 0.56 pJ/bit |

| konkrete Umsetzung | Ryzen 3. Gen Ryzen Threadripper 3. Gen EPYC 2. Gen | Stratix 10 | - |

Der Vergleich der einzelnen Chiplet-Designs zueinander, zeigt die Unterschiede deutlich auf. Während AMD mit der höchsten Datenrate für den Interconnect aufwarten kann, sind Intel und TSMC scheinbar technologisch in der Lage, deutlich kompakter zu fertigen, was auch in der Auslegung der Produkte erkennbar ist. AMD konzentriert sich auf den Desktop-Markt, in dem Baugröße und Abstände keine allzu große Rolle spielen. Damit nimmt AMD auch eine etwas geringere Effizienz für den Interconnect in Kauf. Dafür kann AMD in diesem Jahr mit ersten konkrete Produkten für den Desktop- und Servermarkt aufwarten.

Intel spezialisiert sich hinsichtlich des Chiplet-Designs zunächst auf Spezialmärkte. In der breiten Massen wird es noch etwas dauern, bis wir EMIB und AIB in Kombination sehen werden. TSMC hat auf dem VLSI-Symposium zunächst eine reine Machbarkeitsstudie präsentiert. Konkrete Produkte sind noch nicht absehbar. AMD lässt seine CPU-Chiplets zwar bei TSMC fertigen, das Packaging findet aber an anderer Stelle statt und die Interconnect-Technologie basiert auf einer eigenen Technik.