Werbung

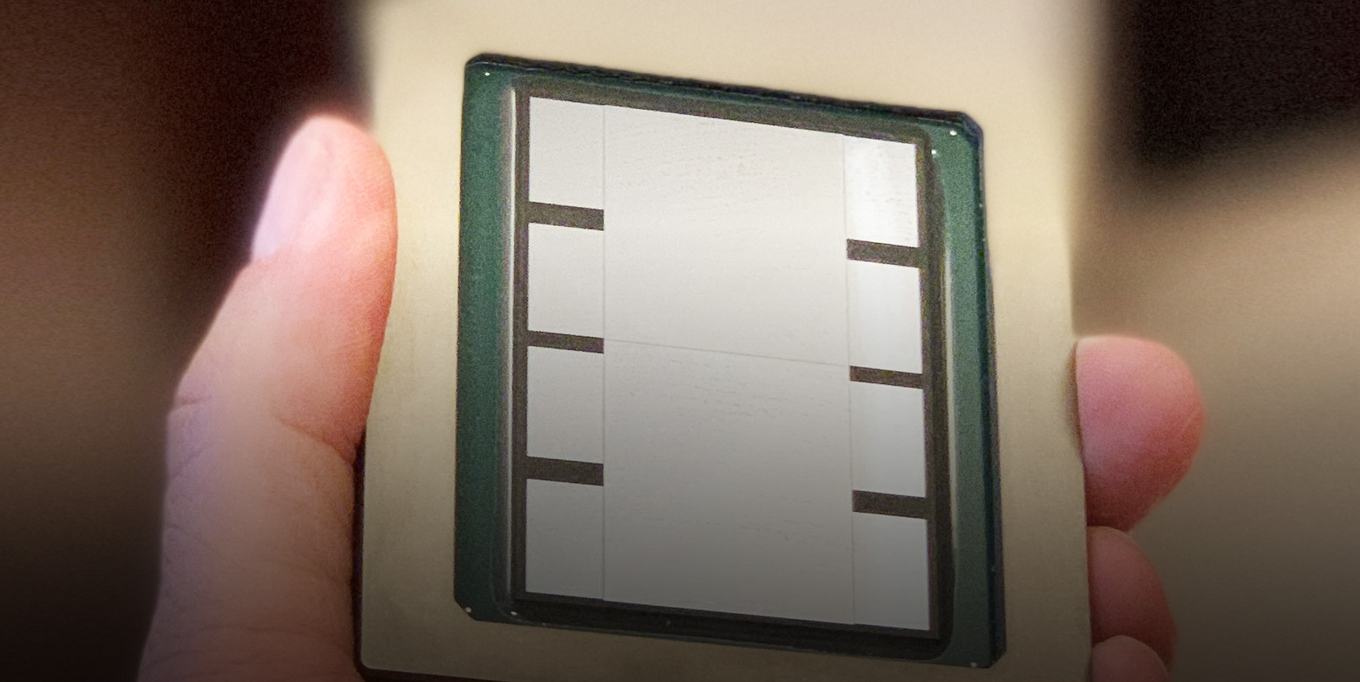

TSMC hat gemeinsam mit Broadcom die eigenen Interposer- und Interconnect-Technologie CoWoS (Chip-on-Wafer-on-Substrate) in die Produktionsreife gebracht und wird in dieser Zusammenarbeit wohl bald konkrete Produkte ankündigen. Die Besonderheit in der Zusammenarbeit liegt in der Größe des gemeinsam entwickelten Interposers. Dieser kommt auf eine Fläche von 1.700 mm² und soll neben in 5 nm (N5) gefertigten Chips schnellen HBM aufnehmen.

Mitte des vergangenen Jahres zeigte TSMC ein entsprechendes Konzept. In diesem kamen zwei 600 mm² großen Chips zum Einsatz, an die jeweils vier – also insgesamt acht – HBM-Chips angebunden waren. Die Chips kommen somit zusammengenommen auf 1.800 mm², die allesamt auf einem 2.500 mm² großen Interposer untergebracht sind.

Die nun konkretere Ausführung ist mit 1.700 mm² deutlich kleiner, jedoch vergleichsweise herausfordernd in der Fertigung. TSMC kombiniert zusammen mit Broadcom eine unbekannte Anzahl an SoC-Dies mit sechs HBM-Speicherchips. In diesem Zusammenhang ist die Rede von einer Maximalkapazität von 96 GB – was für den Einsatz von HBM2E mit bis zu 16-Hi-Stacks spricht. Die Speicherbandbreite wird mit bis zu 2,7 TB/s angegeben – entsprechend 460 GB/s pro HBM2E-Speicherstack. SK Hynix und Samsung haben bereits vor einiger Zeit die entsprechenden Speicherchips angekündigt.

Im Zusammenhang mit der Ankündigung sieht TSMC den Einsatz von CoWoS in Chips für HPC-, 5G- und Machine-Learning-Anwendungen. In welchem Bereich Broadcom hier zusammen mit TSMC nun ein konkretes Produkt vorstellen wird, ist unklar. Mit dem Tomahawk 4 (BCM56990) hat Broadcom Ende des vergangenen Jahres den laut eigenen Angaben größten und komplexesten Netzwerk-SoC vorgestellt. Dieser setzt jedoch nicht auf CoWoS und ein entsprechendes Packaging.

"Broadcom is happy to have collaborated with TSMC on advancing the CoWoS platform to address a host of design challenges at 7nm and beyond," sagt Greg Dix, Vice President des Engineering für ASIC-Produkte bei Broadcom. "Together, we are driving innovation with unprecedented compute, I/O and memory integration and paving the way for new and emerging applications including AI, Machine Learning, and 5G Networking."

TSMC ist nicht der einzige Hersteller, der an solchen technischen Umsetzungen arbeitet. Intel präsentierte erst kürzlich eine Weiterentwicklung von EMIB (Embedded Multi Die Interconnect Bridge) als Co-EMIB und ein Omni-Directional Interconnect (ODI) soll die Kommunikation zwischen den Chips beschleunigen. Mit der aktuellen Ryzen-Generation sprach AMD ausführlich über die Herausforderungen und Umsetzungen des Packaging.

| AMD | Intel | Intel | TSMC | |

| Packaging | MCM | EMIB | FOVEROS | CoWoS |

| Channel | - | 1 mm | - | 500 µm |

| Interconnect Chiplet-Bumps | 130 µm | 45 µm | 36 µm | 40 µm |

| Bump-Dichte | 60 / mm² | 560 / mm² | 828 / mm² | 625 / mm² |

| Interconnect | Infinity Fabric (IF) | Advanced Interface Bus (AIB) | - | LIPINCON |

| Datenrate | 10,6 GT/s | 2 GT/s | - | 8 GT/s |

| Leistungsaufnahme | 2 pJ/Bit | 0,3 pJ/Bit | 0,2 pJ/Bit | 0.56 pJ/bit |

| konkrete Umsetzung | Ryzen 3. Gen Ryzen Threadripper 3. Gen EPYC 2. Gen | Stratix 10 Kaby Lake-G | Lakefield | - |