Werbung

Aus dem Umfeld eines OEMs haben wir einen Schwung interner Folien erhalten. Diese zeigen unter anderem bereits bekannte Details zu AMDs zukünftigen EPYC-Prozessoren namens Milan, beinhalten aber auch bisher unbekannte Details zu den nächsten beiden Generationen Milan und Genoa. Die Folien selbst können wir nicht veröffentlichen, da sie Rückschlüsse auf die Quelle zulassen könnten.

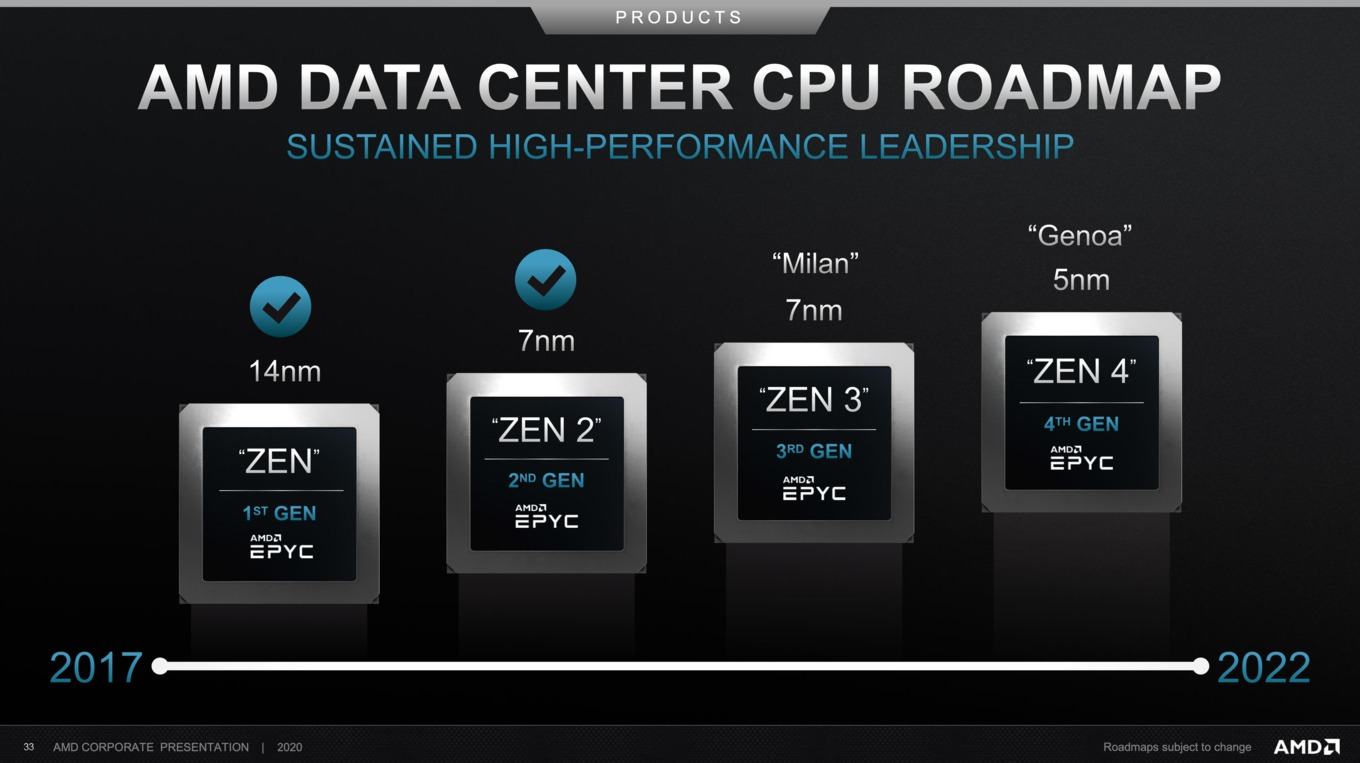

Aus dem vergangenen Jahr und aus aktuellen Verlautbarungen von AMD wissen wir, dass die EPYC-Prozessoren auf Basis des Milan-Designs in 7 nm gefertigt, bis zu 64 Zen-3-Kerne bieten und zudem DDR4 und PCI-Express 4.0 unterstützen werden.

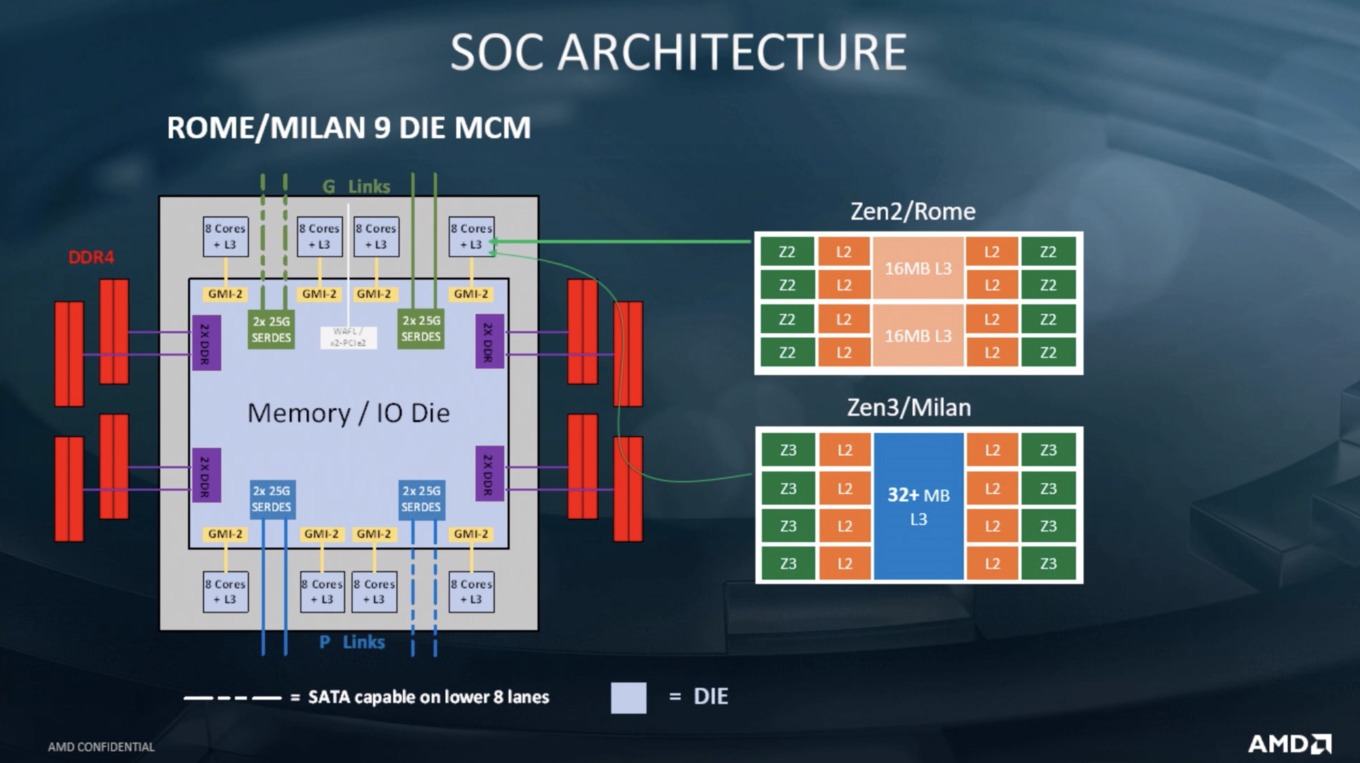

Darüber hinaus gibt es Änderungen im Aufbau des Core Compute Die (CCD) und damit des Core Compute Complex (CCX). Die aktuellen CCDs bestehen aus jeweils zwei CCX-Clustern, in denen auch der L3-Cache in zweimal 16 MB aufgeteilt ist. Dies war schon bei den Zeppelin-Dies der Fall. Für Zen 3 sieht dies nun anders aus. Eine schematische Darstellung zeigte den CCD mit einem gemeinsamen L3-Cache.

| Naples | Rome | Milan | Genoa | |

| Plattform | SP3 | SP3 | SP3 | SP5 |

| Kerne | 32x Zen | 64x Zen 2 | 64x Zen 3 | >64x Zen 4 |

| CCD / L3-Cache | 8 Kerne pro CCD 2x 16 MB L3-Cache | 8 Kerne pro CCD 2x 16 MB L3-Cache | 8 Kerne pro CCD 1x 32 MB L3-Cache | - |

| Fertigung | 14 nm | 7 nm | 7 nm | 5 nm |

| RAM | DDR4 | DDR4 | DDR4 | DDR5 |

| PCIe | PCIe 3.0 | PCIe 4.0 | PCIe 4.0 | PCIe 5.0 |

| TDP | 120 - 180 W | 120 - 225 W | 120 - 225 W | 120 - 240 W |

Soweit man aus den Folien erkennen kann, wird der L3-Cache für Zen 3 32 MB groß werden. AMD selbst sprach im Oktober noch von 32+ MB - es sind also offenbar nicht mehr als 32 MB geworden, sondern es bleibt bei 32 MB. Identisch ist die Anzahl an Kernen mit acht pro CCD, die CCX-Cluster in der bisherigen Form gibt es jedoch nicht mehr.

Einige Leistungswerte führen die Folien ebenfalls auf: Diese sprechen von einem IPC-Leistungsplus von +15 % für Integer-Workloads. Für EPYC-Prozessoren mit bis zu 32 Kernen will AMD ein Leistungsplus von +20 % gegenüber den Rome-Prozessoren mit Zen-2-Kernen erreichen – die Single-Treaded-Leistung soll ebenfalls um +20 % steigen. Für die größeren EPYC-Prozessoren mit bis zu 64 Kernen geht AMD von einem Leistungsplus in Höhe von etwa 10 bis 15 % aus. Offenbar kann AMD bei den Prozessoren mit weniger Kernen einen höheren Takt erreichen, so dass das Leistungsplus sich bei wenigen Kernen entsprechend höher auswirkt. Soweit ist dies nicht weiter verwunderlich. Große Sprünge beim Takt sind nicht zu erwarten, da es bei der Fertigung in 7 nm und dem gewohnten Chiplet-Aufbau bleiben wird.

Für Milan konzentriert sich AMD also auf eine Verbesserung der Leistung der einzelnen Kerne. Ein Leistungsplus von 10 bis 20 % über die zwei EPYC-Generationen ist durchaus beachtlich. Gegen Ende des Jahres wird AMD die nächste EPYC-Generation vorstellen. Perlmutter wird ein erster Supercomputer sein, der die neuen Prozessoren verwendet. Laut den letzten Informationen des Betreibers National Energy Research Scientific Computing Center (NERSC) wird die Phase 1a mit der Installation der ersten Milan-Systeme gegen Ende des Jahres beginnen.

Details zu Genoa

Wir können nun zudem die Lücke schließen, die es bisher nach Milan gibt, denn bis auf die Tatsache, dass für Genoa Zen-4-Kerne und eine Fertigung in 5 nm zum Einsatz kommen werden, ist bisher recht wenig bekannt und AMD hat sich noch nicht weiter zu Details geäußert.

Die Roadmap spricht nun von mehr als 64 Kernen für Genoa. Es bleibt bei zwei Threads pro Kern, also einem SMT2. Ob dies gleich eine Verdopplung gegenüber Milan bedeuten wird, bleibt abzuwarten. Außerdem ist die Rede von DDR5, der Unterstützung von Persistant Memory (NVDIMM-P) und PCI-Express 5.0.

Mit Genoa wechselt AMD von der SP3- auf die SP5-Plattform. Nominell spannt sich die Thermal Design Power von 120 bis 240 W auf, wenngleich es heute schon Sondermodelle gibt, die sich mehr als 225 W (offizielle TDP-Grenze für die normalen Modelle) genehmigen. Die TDP steigt also nach oben hin leicht an. Die Plattformkompatibilität gibt AMD mit Genoa nach drei Generationen auf. Aufgrund der Verwendung von DDR5 und PCI-Express 5.0 sowie weiterer Funktionen bleibt AMD an dieser Stelle jedoch nichts anderes übrig.

Die übernächste EPYC-Generation dürfte das erste Tape Out inzwischen hinter sich gebracht haben. Die Einführung, bzw. Vorstellung wird für die zweite Jahreshälfte 2021 erwartet.

AMD behält die Schlagzahl bei

Mit den EPYC-Prozessoren auf Basis des Rome-Designs sieht sich AMD bereits in der Lage, einen Großteil der Anforderungen im Datacenter-Segment abzudecken. Hohe Kernleistung, viele Kerne, schnelles Speicherinterface und gute Ausstattung in Form von schnellen I/O-Schnittstellen wie PCI-Express 4.0.

Mit Milan konzentriert sich AMD auf den Kernbereich der Rechenleistung in den Zen-3-Kernen. Die Verbesserungen in der Micro-Architektur spielen hier eine wichtige Rolle. Der gemeinsame L3-Cache für die acht Kerne des CCDs sind nur ein Baustein. Ein IPC-Plus von 15 % wurde schon häufiger genannt und ist in dieser Form dann auch von den Ryzen-Prozessoren zu erwarten. Hinsichtlich der Fertigung tut sich in diesem Schritt wenige bis nichts. Milan wird seine Verbesserungen nahezu ausschließlich aus der Core-Architektur beziehen.

Für Genoa wird der Schritt in der Plattform dann wieder etwas größer. Zen 4, 5 nm, PCI-Express 5.0, DDR5 und vieles mehr werden hier ineinander greifen. Intel wird dem mit Sapphire Rapids, bzw. der vierten Generation der Xeon-Scalable-Prozessoren begegnen. Hier ist ebenfalls die Rede von DDR5 und PCI-Express 5.0. Intel peilt für Sapphire Rapids ebenfalls die zweite Jahreshälfte 2021 an.