Werbung

Neben den neusten Fertigungstechnologien hat TSMC auf dem Technology Symposium über die weitere Entwicklung und Fortschritte in der Materialforschung und dem Packaging gesprochen. Neue Materialien und eine fortschreitende Weiterentwicklung in der Integration von mehreren Chips in 2.5D- und 3D-Stapeln sollen in den kommenden Jahren die Rechenleistung weiter anwachsen lassen.

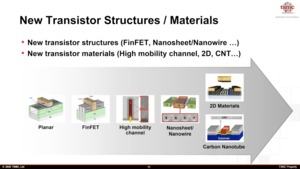

Eines der Zauberworte sind in der Materialforschung die Nanosheets und Nanoröhren. Samsung arbeitet an GAA-basierten FETs (GAAFETs) auf der Basis von Nanodrähten. Der GAAFET auf Basis von Nanosheets ist das, was Samsung einen Multi-Bridge Channel FET oder MBCFET nennt. Bei Intel arbeitet man an Nanoribbon-Gate-All-Around-Transistoren, die auf eine ähnliche Art und Weise aufgebaut sind. Zuletzt präsentierte Intel mit der 10nm SuperFin Technology die vermeintliche Rettung der Fertigung in 10 nm und auch hier spielen neue Materialen eine entscheidende Rolle.

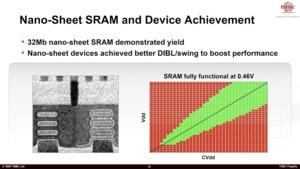

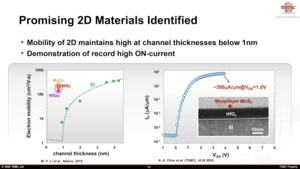

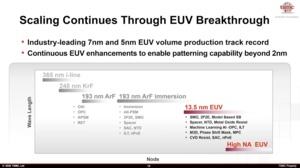

Bei TSMC arbeitet man ebenfalls an Nanoröhren und Nanosheets und hat mit einem 32 MBit großen SRAM mit Nanosheets sogar schon erste Tests gemacht, die erfolgreich verlaufen sind. Um die Mobilität der Ladungen selbst bei kleinen Strukturen hoch zu halten, forscht man bei TSMC an neuen Materialien. Über unterschiedliche Dotierungen und weitere Verfahren gelingt dies inzwischen für Kanalbreiten von gerade einmal 1 nm. Hier werden die Grundsteine für eine Fertigung gelegt, die auch über 3 nm hinaus noch skalieren soll. Dazu arbeitet man mit ASML, dem größten Hersteller für Maschinen zur Belichtung von Wafern, an neuen Technologien, um die Entwicklung von EUV-Beleuchtungstechniken weiter voranzutreiben.

Packaging mit riesigen Chips samt 12x HBM

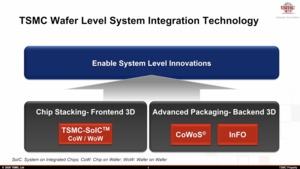

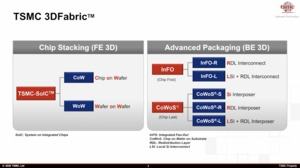

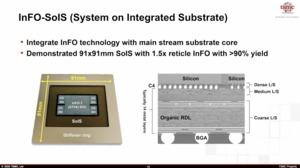

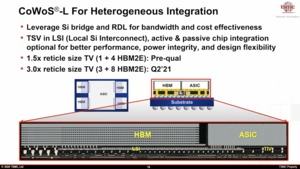

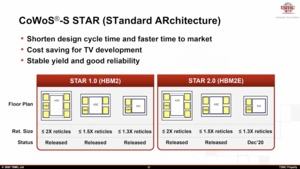

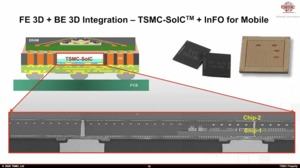

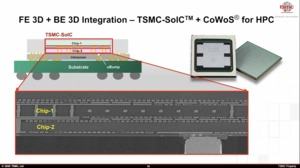

Bereits im Frühjahr zeigte TSMC die Weiterentwicklung seiner Interposer- und Interconnect-Technologie CoWoS (Chip on Wafer on Substrate). Hier vereint man die CoW- (Chip on Wafer) und WoW-Technik (Wafer on Wafer), die im Rahmen des 3D-Stackings verschiedener Chips (am Front End) direkt aufeinander verwenden. Alle Packaging-Technologien fasst man nun unter dem Namen 3DFabric zusammen.

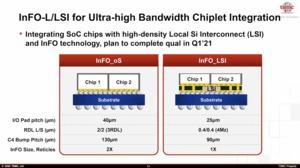

Es gibt verschiedene Ansätze für das Packaging, die TSMC in InFO (Chip First) und eben CoWoS (Chip Last) aufteilt. Zwischen diesen verschiedenen Techniken gibt es zahlreiche Unterkategorien, die beispielsweise Zwischenschichten vorsehen, um einen Chip auf einem Silicon Interposer unterzubringen.

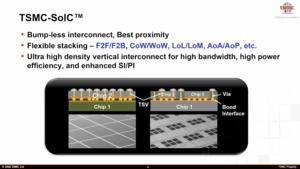

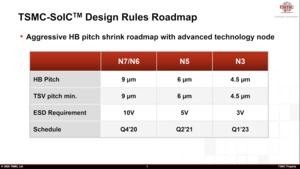

Für das SoIC, also die Verbindung zwischen mehreren Chips, sieht TSMC über die nächsten Generationen der Fertigungsgrößen ebenfalls große Fortschritte. Der Abstand zwischen den Bumps, bzw. der Through-silicon Via (TSV) soll von 9 µm für N7/N6 auf 6 µm für N5 und 4,5 µm für N3 zusammenschrumpfen. Im vierten Quartal 2020 will man erste Chips, die in N7/N6 gefertigt werden, in dieser Form zusammenbringen können. Im zweiten Quartal 2021 sollen dann Chips aus der N5-Fertigung folgen. Für das erste Quartal 2023 plant TSMC das Zusammenbringen von Chips aus der Fertigung in 3 nm (N3). Das Packaging der Chips und die Fertigung derselbigen sind immer leicht verzögert, da TSMC erst die Chips fertigen kann, um dann das dazugehörige Packaging zu entwickeln, bzw. testen zu können.

In der Chipfertigung gibt es für jede Fertigungsgröße bestimmte Grenzen für die Größe der Chips, die nicht überschritten werden können. Aktuell liegen diese bei etwa 850 mm² für einen in 7 nm gefertigten Chip. Sollen die Prozessoren also größer werden, müssen sie aus mehreren Chiplets gefertigt werden, die dann wieder zusammengebracht werden.

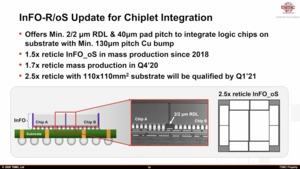

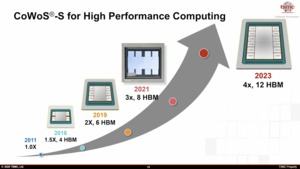

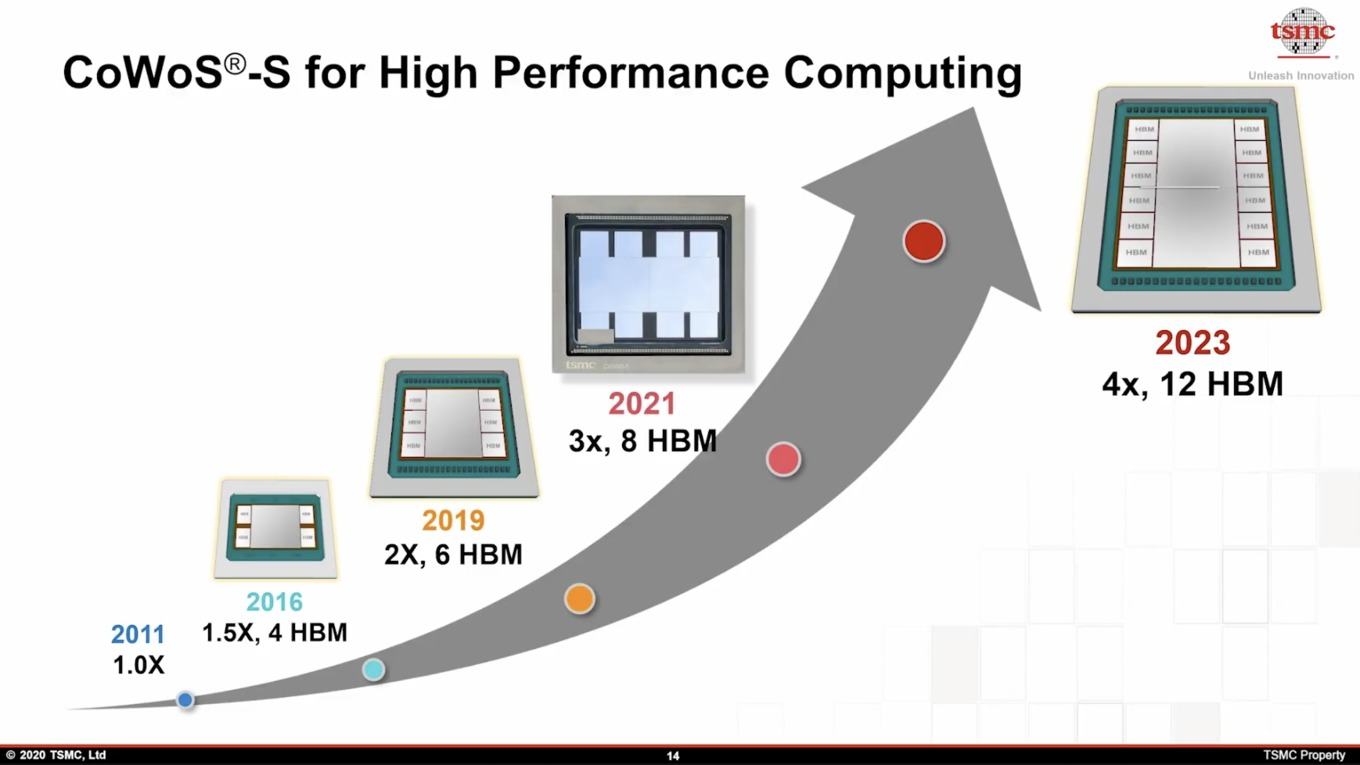

Solche Limits gibt es für das Packaging ebenfalls. Mitte des vergangenen Jahres zeigte TSMC ein Package, bei dem zwei 600 mm² große Chips zum Einsatz kamen, an die jeweils vier – also insgesamt acht – HBM-Chips angebunden waren. Die Chips kommen somit zusammengenommen auf 1.800 mm², die allesamt auf einem 2.500 mm² großen Interposer untergebracht sind. Diesen Stand der Technik will TSMC ab 2021 in die Praxis überführen und entsprechende Chips herstellen können.

Ab 2021 soll die Anzahl der Chips, deren Größe und die Größe des Substrats weiter ausgebaut werden. TSMC spricht hier von Substraten, die 12.100 mm² (110 x 110 mm) groß sind und gleich ein Dutzend Chips aufnehmen können. Die Packages sollen dabei die vierfache Größe dessen erreichen, was als monolithischer Chip technisch möglich wäre. Zwei schon 600 mm² große Chips sollen sich ab 2023 mit zwölf HBM-Chips kombinieren lassen.

TSMC und Intel setzen alles auf Packaging und Chiplet-Design

Das, was TSMC an zukünftigen Technologien zeigt, zeigt in eine Richtung, die auch Intel auf dem Architecture Day aufzeigte. Während Intel jedoch einige Schwierigkeiten in der Ausführung seiner Fertigungs-Roadmap hat, fährt TSMC mit Volldampf in eine Zukunft, die eine moderne Fertigung der einzelnen Chips im Zusammenspiel mit einer ebenso modernen Packaging-Technik vorsieht.

AMD ist mit den Ryzen- und EPYC-Prozessoren auf ein Chiplet-Design umgestiegen und einzig die mobilen Chips verwenden noch ein monolithisches Design. Die aktuellen und künftigen GPUs von AMD und NVIDIA werden ebenfalls noch kein Chiplet-Design sein, aber der Weg ist klar gezeichnet und eher früher als später werden Produkte im Endkundenbereich vermehrt auf moderne Packaging-Technologien setzen.