Werbung

Nachdem OpenFive in der vergangenen Woche eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte, folgte jetzt die Ankündigung, dass man nun High-Performance-SoCs bei TSMC in 5 nm fertigen könne. Ein Referenzdesign habe den Tape Out erfolgreich geschafft und mache damit den Weg frei, so dass Kunden ihrerseits Chips auf Basis der 5-nm-Fertigung entwickeln können.

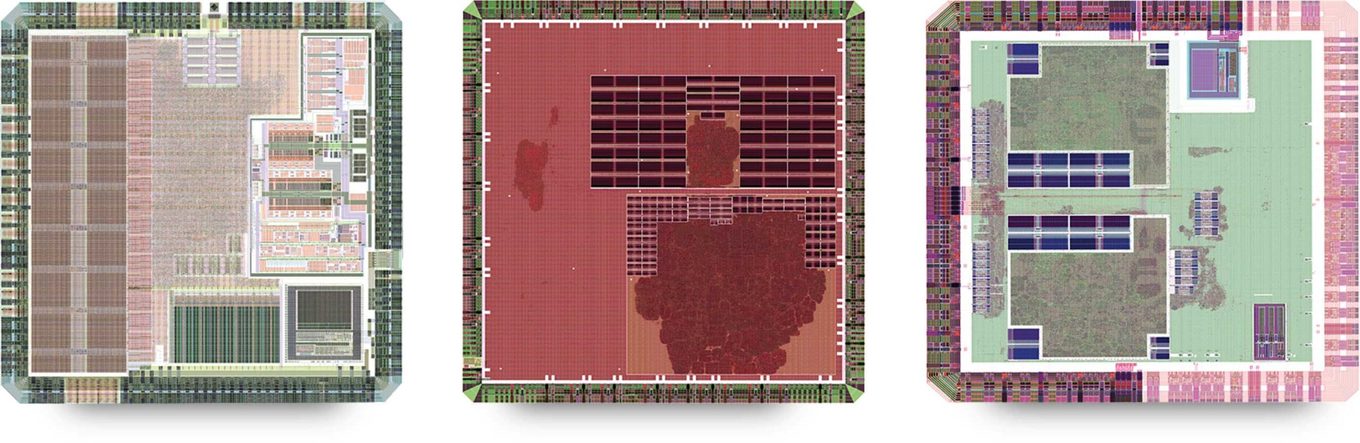

Nun ist eine Fertigung in 5 nm keine wirkliche Neuheit. Bereits Apples M1 und die aktuellen A-Series-SoCs werden in 5 nm gefertigt. In der zweiten Jahreshälfte dürften zahlreiche weitere Smartphone-Chips hinzukommen. OpenFive ist eine Tochter von SiFive. Die von OpenFive angebotenen IP-Blöcke basieren auf den Designs von SiFive und können entsprechend nach Kundenwunsch angepasst werden. Zum IP-Portfolio von OpenFive gehören neben D2D-Interfaces auch Ethernet-, USB- und Speicher-IP (HBM2/HBM2E). Core-IP, also die Designs der RISC-V-Kerne, werden hingegen bei SiFive entwickelt.

Der Referenz-SoC für die Fertigung in 5 nm verwendet einen SiFive-E76-Kern im 32-Bit-Design. Das dazugehörige HBM3-Interface kann bis zu 7,2 GBit/s erreichen. Zum Vergleich: Ein HBM2e kommt auf 3,6 GBit/s und ein HBM2 auf 2,5 GBit/s.

Die Chiplösungen für die Fertigung in 5 nm von OpenFive für HPC/AI-, Netzwerk- und Speicherlösungen können durch Kunden bereits entwickelt werden. Die ersten fertigen Chips sollen voraussichtlich ab dem zweiten Quartal ausgeliefert werden.

Für OpenFive stellt die Fertigung in 5 nm bei TSMC die aktuell beste Lösung dar. Das Verhältnis aus Power, Performance und Area (PPA) sei hier ideal. Zudem ließe sich dies mit einem 2.5D-Packaging kombinieren. Zusammen mit HBM3 ergäbe dies eine ideale AI- und HPC-Plattform.

Aktuell kommen RISC-V-Kerne hauptsächlich als Co-Prozessoren in diversen Chips zum Einsatz. Dies wären mobile SoCs, SSD-Controller, aber auch Prozessoren von AMD und GPUs von NVIDIA. SiFive und die Open-Source-Strategie für Hardware wollen jedoch eine ganzheitliche Lösung werden. Vom kleinen Co-Prozessor bis zum großen HPC-Chip sollen die Designs irgendwann reichen. Dazu sind eben neben der Entwicklung der eigentlichen Kerne auch ein 2.5D-Packaging und IP für Speicher, Netzwerk sowie vieles mehr notwendig.