News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

HBM3

-

HBM4 von Sk hynix: 2026 soll es mit 32 GB losgehen

Aktuell werden die ersten AI-Beschleuniger mit HBM3 bestückt. Dazu gehören NVIDIAs H100, aber auch der Radeon Instinct MI300A und MI300X von AMD. Lieferanten des schnellen Speichers sind Samsung und Sk hynix – beides in Südkorea ansässige Unternehmen. Laut BusinessKorea hat Sk hynix auf einem Investoren-Event seine Bestrebungen bestätigt, diesen Speicherbereich in diesem und dem kommenden Jahr weiter auszubauen. Zwar macht der HBM... [mehr]

Aktuell werden die ersten AI-Beschleuniger mit HBM3 bestückt. Dazu gehören NVIDIAs H100, aber auch der Radeon Instinct MI300A und MI300X von AMD. Lieferanten des schnellen Speichers sind Samsung und Sk hynix – beides in Südkorea ansässige Unternehmen. Laut BusinessKorea hat Sk hynix auf einem Investoren-Event seine Bestrebungen bestätigt, diesen Speicherbereich in diesem und dem kommenden Jahr weiter auszubauen. Zwar macht der HBM... [mehr] -

SK hynix liefert ersten HBM3 an NVIDIA

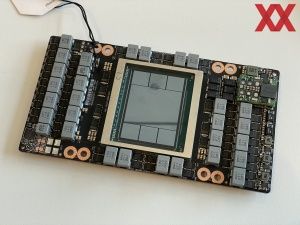

Bereits bekannt ist, dass NVIDIA für seinen H100-Beschleuniger auf Basis der Hopper-Architektur HBM3-Speicher verwenden will. Nun hat SK hynix bestätigt, dass der Speicher vom südkoreanischen Hersteller stammen wird und dass man gemeinsam mit NVIDIA die Validierung abgeschlossen habe. Ab dem dritten Quartal 2022 sollen die ersten H100-Beschleuniger ausgeliefert werden. Dies deckt sich mit den Ankündigungen von NVIDIA. "NVIDIA has recently... [mehr]

Bereits bekannt ist, dass NVIDIA für seinen H100-Beschleuniger auf Basis der Hopper-Architektur HBM3-Speicher verwenden will. Nun hat SK hynix bestätigt, dass der Speicher vom südkoreanischen Hersteller stammen wird und dass man gemeinsam mit NVIDIA die Validierung abgeschlossen habe. Ab dem dritten Quartal 2022 sollen die ersten H100-Beschleuniger ausgeliefert werden. Dies deckt sich mit den Ankündigungen von NVIDIA. "NVIDIA has recently... [mehr] -

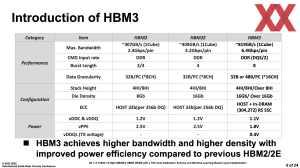

ISSCC 2022: Sk hynix spricht über die aktuelle Entwicklung beim HBM3

Erst kürzlich hat die JEDEC ein Update der Spezifikationen von HBM3 veröffentlicht. Auf Basis dieser Daten hat SK hynix einen Vortrag auf der ISSCC 2022 gehalten, dessen Essenz wir an dieser Stelle weitergeben wollen. Nach der ersten Generation machte HBM zur zweiten und vor allem als HBM2E bekannten Variante nur noch vergleichsweise kleine Schritte. Ja, die Chips wurden schneller, ein großer Sprung in der Erhöhung der Kapazität und... [mehr]

Erst kürzlich hat die JEDEC ein Update der Spezifikationen von HBM3 veröffentlicht. Auf Basis dieser Daten hat SK hynix einen Vortrag auf der ISSCC 2022 gehalten, dessen Essenz wir an dieser Stelle weitergeben wollen. Nach der ersten Generation machte HBM zur zweiten und vor allem als HBM2E bekannten Variante nur noch vergleichsweise kleine Schritte. Ja, die Chips wurden schneller, ein großer Sprung in der Erhöhung der Kapazität und... [mehr] -

HBM3-Update: 819 GB/s und bis zu 64 GB pro Chip

Die JEDEC Solid State Technology Association hat ein Update der Spezifikationen von HBM3 veröffentlicht. Darin werden die technischen Spezifikationen noch einmal zurechtgerückt. Einige der technischen Daten waren bereits bekannt, vor allem weil Hersteller wie SK hynix bereits im Vorfeld ihre konkreten Umsetzungen vorstellen. In der Entwicklung zu HBM3 kam es offenbar zu einigen Problemen, denn er kommt später als erwartet und war vor allem in... [mehr]

Die JEDEC Solid State Technology Association hat ein Update der Spezifikationen von HBM3 veröffentlicht. Darin werden die technischen Spezifikationen noch einmal zurechtgerückt. Einige der technischen Daten waren bereits bekannt, vor allem weil Hersteller wie SK hynix bereits im Vorfeld ihre konkreten Umsetzungen vorstellen. In der Entwicklung zu HBM3 kam es offenbar zu einigen Problemen, denn er kommt später als erwartet und war vor allem in... [mehr] -

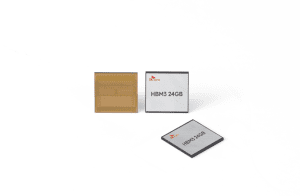

HBM3 von SK Hynix: 24 GB pro Chip und bis zu 6,4 GBit/s pro Pin

Lange ist es zu einer neuen Generation des HBM-Speichers still gewesen. Bei den Grafikkarten für Endkunden und auch im Workstation-Bereich haben sich AMD und Intel wieder auf den Einsatz von GDDR beschränkt, bei Beschleunigern im Datacenter kommt HBM aber weiterhin zum Einsatz – aktuell als HBM2E. Die JEDEC hat die finalen Spezifikationen zu HBM3 nicht final freigegeben, dennoch prescht SK Hynix jetzt nach vorne und stellt die... [mehr]

Lange ist es zu einer neuen Generation des HBM-Speichers still gewesen. Bei den Grafikkarten für Endkunden und auch im Workstation-Bereich haben sich AMD und Intel wieder auf den Einsatz von GDDR beschränkt, bei Beschleunigern im Datacenter kommt HBM aber weiterhin zum Einsatz – aktuell als HBM2E. Die JEDEC hat die finalen Spezifikationen zu HBM3 nicht final freigegeben, dennoch prescht SK Hynix jetzt nach vorne und stellt die... [mehr] -

Langsamer als erwartet: SK Hynix nennt Daten zu HBM3

Neben einigen wenigen Ausnahmen hat es der schnelle High Bandwidth Memory bisher noch nicht in die breite Masse geschafft. Auf HBM folgte mit HBM2 die zweite Generation und inzwischen sind wir bei HBM2E angekommen, der als schnellster Stapelspeicher zum Einsatz kommt. Das Einsatzgebiet beschränkt sich vor allem auf AI/ML-Beschleuniger, die auf eine möglichst hohe Speicherbandbreite angewiesen sind. Seit einigen Jahren wird der Start von HBM3... [mehr]

Neben einigen wenigen Ausnahmen hat es der schnelle High Bandwidth Memory bisher noch nicht in die breite Masse geschafft. Auf HBM folgte mit HBM2 die zweite Generation und inzwischen sind wir bei HBM2E angekommen, der als schnellster Stapelspeicher zum Einsatz kommt. Das Einsatzgebiet beschränkt sich vor allem auf AI/ML-Beschleuniger, die auf eine möglichst hohe Speicherbandbreite angewiesen sind. Seit einigen Jahren wird der Start von HBM3... [mehr] -

RISC-V-SoC mit HBM3-Subsystem kann in 5 nm gefertigt werden

Nachdem OpenFive in der vergangenen Woche eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte, folgte jetzt die Ankündigung, dass man nun High-Performance-SoCs bei TSMC in 5 nm fertigen könne. Ein Referenzdesign habe den Tape Out erfolgreich geschafft und mache damit den Weg frei, so dass Kunden ihrerseits Chips auf Basis der 5-nm-Fertigung entwickeln können. Nun ist eine Fertigung in 5 nm keine... [mehr]

Nachdem OpenFive in der vergangenen Woche eine neue technische Umsetzung eines Interconnect-PHY für zukünftige Chiplet-Designs vorstellte, folgte jetzt die Ankündigung, dass man nun High-Performance-SoCs bei TSMC in 5 nm fertigen könne. Ein Referenzdesign habe den Tape Out erfolgreich geschafft und mache damit den Weg frei, so dass Kunden ihrerseits Chips auf Basis der 5-nm-Fertigung entwickeln können. Nun ist eine Fertigung in 5 nm keine... [mehr] -

Rambus will mit DDR5 und HBM3 wieder zurück ins Geschäft

Rambus war einmal eines der innovativsten Unternehmen im IT-Segment und an der Schwelle hier eine große Hausnummer zu werden. Allerdings verspekulierte man sich um das Jahr 2000 mit der Entwicklung und Einführung des RDRAM. Als erster Speicher nutzte man die Technik der Datenübertragung an der steigenden und abfallenden Flanke. Somit waren über einen 64 Bit breiten Datenbus bei Taktraten von 133 MHz Bandbreite von bis zu 1.066 MB/s möglich... [mehr]

Rambus war einmal eines der innovativsten Unternehmen im IT-Segment und an der Schwelle hier eine große Hausnummer zu werden. Allerdings verspekulierte man sich um das Jahr 2000 mit der Entwicklung und Einführung des RDRAM. Als erster Speicher nutzte man die Technik der Datenübertragung an der steigenden und abfallenden Flanke. Somit waren über einen 64 Bit breiten Datenbus bei Taktraten von 133 MHz Bandbreite von bis zu 1.066 MB/s möglich... [mehr] -

Hot Chips 28: Über GDDR6, DDR5, HBM3, LPDDR5 und mehr

Auf das Intel Developer Forum in der vergangenen Woche folgte gestern der Start der Hot Chips 28, der Konferenz rund um neue Speicherstandards und Technologien in diesem Bereich. GDDR6, DDR5, HBM3 und LPDDR5 sind neue Speicherstandards, die uns in den kommenden Jahren erwarten werden. Auf einer solchen Konferenz wird dann auch deutlich, welches Unternehmen bestimmte Interessen verfolgt und wo es die eigenen Stärken sieht. Dies zeigt sich häufig... [mehr]

Auf das Intel Developer Forum in der vergangenen Woche folgte gestern der Start der Hot Chips 28, der Konferenz rund um neue Speicherstandards und Technologien in diesem Bereich. GDDR6, DDR5, HBM3 und LPDDR5 sind neue Speicherstandards, die uns in den kommenden Jahren erwarten werden. Auf einer solchen Konferenz wird dann auch deutlich, welches Unternehmen bestimmte Interessen verfolgt und wo es die eigenen Stärken sieht. Dies zeigt sich häufig... [mehr]