Werbung

Nachdem IBM heute den ersten im 2-nm-Prozess gefertigten Chip angekündigt hat, folgt eine weitere Ankündigung aus der Halbleiterfertigung. Samsung kündigt mit Interposer-Cube4 (I-Cube4) die nächste Generation der 2.5D-Integration für die Kombination verschiedener Chiplets auf einem Package an.

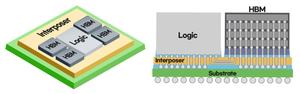

Im Vergleich zu I-Cube2 hat Samsung vor allem einige Änderungen in der Interposer-Technik vorgenommen. Die I-Cube-IP von Samsung sieht den Einsatz eines oder mehrerer Logic-Dies mit mehreren HBM-Chips vor. Als Beispiel führt Samsung Chips mit einem Logic-Die und vier HBM-Chips an. Was das Maximum für I-Cube4 darstellt, verrät Samsung nicht. TSMC plant ab 2023 CoWoS zwei große Logic-Dies mit bis zu 12 HBM-Chips auf einem Package unterbringen zu können.

Nun sind mehrere Chips auf einem Package noch keine Neuigkeit. Allerdings hat es Samsung geschafft, den dafür verwendeten Interposer nur 100 µm dick fertigen zu müssen. Dies soll das Thermomanagement, also die Kühlung, vereinfachen sowie eine stabile Stromversorgung ermöglichen. Auch in der Fertigung des eigentlichen Interposers und der späteren Aufbringung der Chips sind dünnere Interposer wünschenswert, da die Wahrscheinlichkeit, dass ein dickerer Interposer gebogen oder verzogen wird, mit dessen Dicke steigt. Ein Interposer sollte aber möglichst flach sein.

Zudem hat Samsung eine Methode entwickelt, die Ausbeute in der Fertigung der Interposer zu verbessern, indem ein Vorscreening-Test durchgeführt wird, der fehlerhafte Produkte während des Herstellungsprozesses herausfiltern kann. Dieser Ansatz reduziert außerdem die Anzahl der Prozessschritte, was zu einer Kostenreduzierung und kürzeren Durchlaufzeiten führt.

Die ersten Chips aus den Bereichen HPC, AI/ML, 5G, Cloud und Data Center mit dem I-Cube4-Packaging sollen bereits in Kürze durch Samsung gefertigt werden können. Aktuell arbeitet Samsung bereits an I-Cube6, was eine 2.5/3D-Packaging-Technologie werden soll.