Werbung

Bereits gestern berichteten wir über die kurz- und langfristigen Pläne TSMCs hinsichtlich der Fertigung. 2022 soll es bereits mit 3 nm losgehen, während die N6- und N4-Fertigung als kleinere Optimierungsschritte der Fertigung in 7 und 5 nm geplant sind. Neben einer immer kleineren Strukturgrößen in der Fertigung, spielt aber das Packaging in den kommenden Jahren eine ebenso wichtige Rolle.

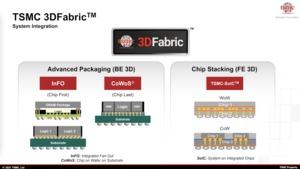

Bereits im vergangenen Jahr führte TSMC die verschiedenen Methoden für ein 3D-Packaging genauer aus. Diese fasst TSMC als 3D Fabric zusammen. Grundsätzlich teilen sie sich in InFO (Chip First) und CoWoS (Chip Last) auf. Drittes Standbein in diesem Bereich ist das Chip-Stacking TSMC-SoIC. Diese Methode kommt bei AMDs 3D V-Cache zum Einsatz. Hier wird ein aktuell 64 MB großer SRAM auf dem L3-Cache des Ryzen-CCDs gestapelt, so dass der 32 MB große L3-Cache um weitere 64 MB erweitert werden kann. TSVs führen direkt vom CCD zum SRAM. Micro Bumps kommen nicht zum Einsatz. Laut AMD soll die Fertigung der ersten Prozessoren mit 3D V-Cache gegen Ende des Jahres starten.

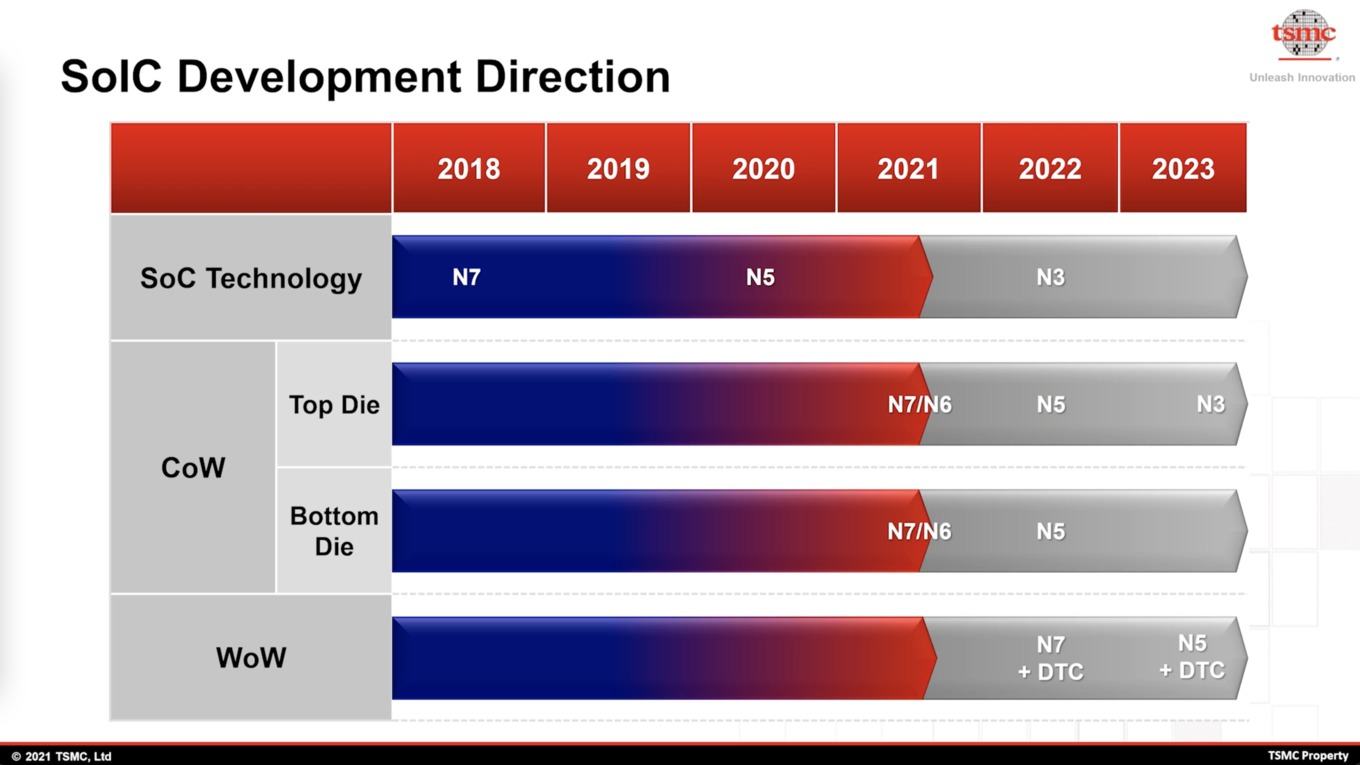

Dies passt auch gut zu TSMCs Plänen für SoIC. Im vierten Quartal 2021 will TSMC mit der Qualifizierung von ersten Chips beginnen, bei denen die einzelnen Chips jeweils in 7 nm (N7-on-N7) gefertigt werden. Genau dies passt zum Anforderungsprofil von AMD, denn die Zen-3-CCDs werden in 7 nm gefertigt – ebenso wie der darüber gestapelte SRAM. Für den SRAM kann TSMC eine darauf optimierte Version der N7-Fertigung verwenden und daher auch 64 MB auf 36 mm² packen, die dann auf dem 81 mm² großen CCD sitzen.

Im dritten Quartal 2022 soll es dann möglich sein, für beide Chips des Stapels die N5-Fertigung zu verwenden. AMD dürfte darauf dann mit den Zen-4-CCDs zurückgreifen.

Die große Lücke, die aktuell zwischen der Fertigungsgröße der eigentlichen Chips und der Möglichkeit diese zu stapeln vorhanden ist, will TSMC bis 2023 geschlossen haben. Lagen zwischen der Fertigung in 7 nm und dem N7-on-N7-Packaging noch drei bis vier Jahre und zwischen der Fertigung in 5 nm und dem N5-on-N5-Packaging ebenfalls noch drei Jahre, sollen es für die Fertigung in 3 nm sowie für N3-on-N3 nur noch knapp zwölf Monate sein.

Dies dürfte dazu führen, dass mehr und mehr Kunden daran interessiert sind, da früher die neusten Fertigungstechnologien für die Chips zum Einsatz kommen.

TSMC und Intel setzen Fokus auf das Packaging

Während die Fertigung der eigentlichen Transistoren den Trend der immer kleineren Fertigungsschritte macht, hier aber auch etwas das Tempo herausgenommen wird, fahren fast alle Auftragsfertiger und Chiphersteller über das Packaging in gewisser Weise zweigleisig. Das Packaging wird daher in den kommenden Jahren an Bedeutung gewinnen. TSMC bietet seine Dienste in den verschiedenen Variationen des 3D Fabric an, aber auch Intel will EMIB, Co-EMIB und Foveros nicht nur für die eigenen Chip verwenden, sondern bietet die Technologien im Rahmen des IDM-2.0-Programms auch externen Kunden an.

Auf Seiten der Produkte wird Intel seinem Konkurrenten AMD in der Chiplet-Strategie Ende 2021 mit Alder Lake folgen. Neben dem Endkundenbereich hat Intel diesen Weg zudem für das Datacenter bereits eingeschlagen. AMD ist dem Chipriesen in der Technologie aber bereits einige Schritte voraus – natürlich mit Hilfe von TSMC. Die Ryzen- und EPYC-Prozessoren setzen bereits seit drei Generationen auf den Chiplet-Ansatz. Mit dem 3D V-Cache geht man hier bereits in wenigen Monaten den nächsten Schritt.