Werbung

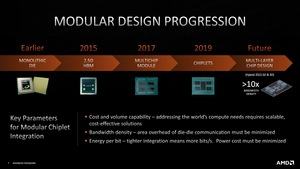

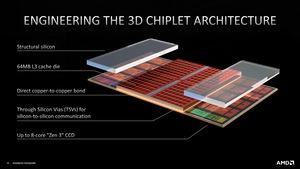

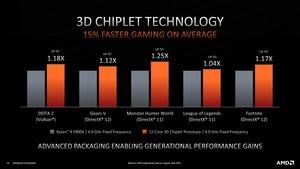

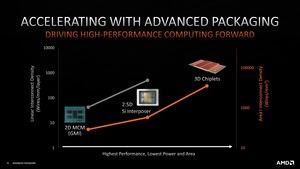

Zur Computex AnfangJuni nannte AMD die ersten Details zum 3D V-Cache, der den L3-Cache der Prozessoren um ein vielfaches vergrößern können soll. In einem ersten Schritt kann AMD damit den L3-Cache pro CCD um den Faktor drei erhöhen. Mit weiteren Stapeln wären aber noch deutlich größere Steigerungen möglich. Der 3D V-Cache ist AMDs Lösung für den Bedarf nach immer größerem und schnellem Speicher möglichst nahe an den CPU-Kernen.

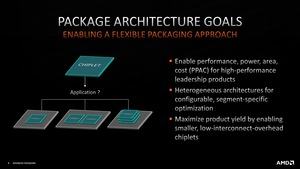

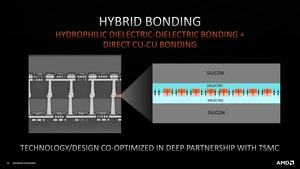

AMD fertigt seine Prozessoren nicht selbst und hat für den 3D V-Cache gemeinsam mit seinem Auftragsfertiger TSMC entwickelt. TSMC-SoIC heißt die Packaging-Technologie, wie sie TSMC seinen Kunden anbietet.

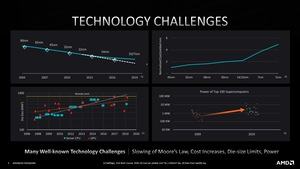

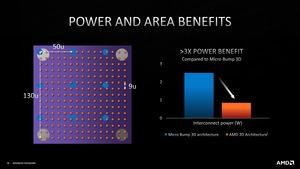

Auf der Hot Chips 33 hat AMD nun weitere Details zum 3D V-Cache verraten. Den Vortrag hielt Raja Swaminathan, Senior Fellow für das Packaging bei AMD. Unter anderem sprach er über die Abstände der TSVs (Through-Silicon Via). Eine erste Analyse von TechInsights kam auf einen Abstand von gerade einmal 17 µm. Zum Vergleich: Intels Packaging-Techniken EMIB (Embedded Multi-die Interconnect Bridge) der ersten und zweiten Generation kommen auf 55 bzw. 45 µm. Für Foveros der ersten Generation, hier können auch Chips aus unterschiedlichen Fertigungsgrößen miteinander verbunden werden, sind es 36 µm. Die Weiterentwicklungen Foveros Omni und Foveros Direct sollen dann einen Abstand von 25 bzw. 10 µm ermöglichen. Mit 17 µm läge AMD hier gemeinsam mit TSMC schon auf einem extrem hohen Niveau.

Laut der Präsentation erreicht AMD für den 3D V-Cache aber sogar einen Abstand zwischen den TSVs von gerade einmal 9 µm. Damit läge man hier schon auf Niveau von Foveros Direct – der nächsten Generation von Intels Packaging, auf das man besonders stolz ist. TSMC scheint dieser Technik aber in keinster Weise nachzustehen.

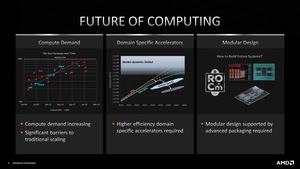

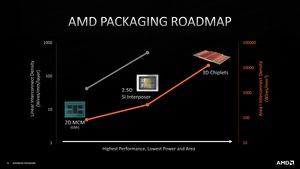

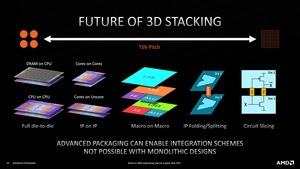

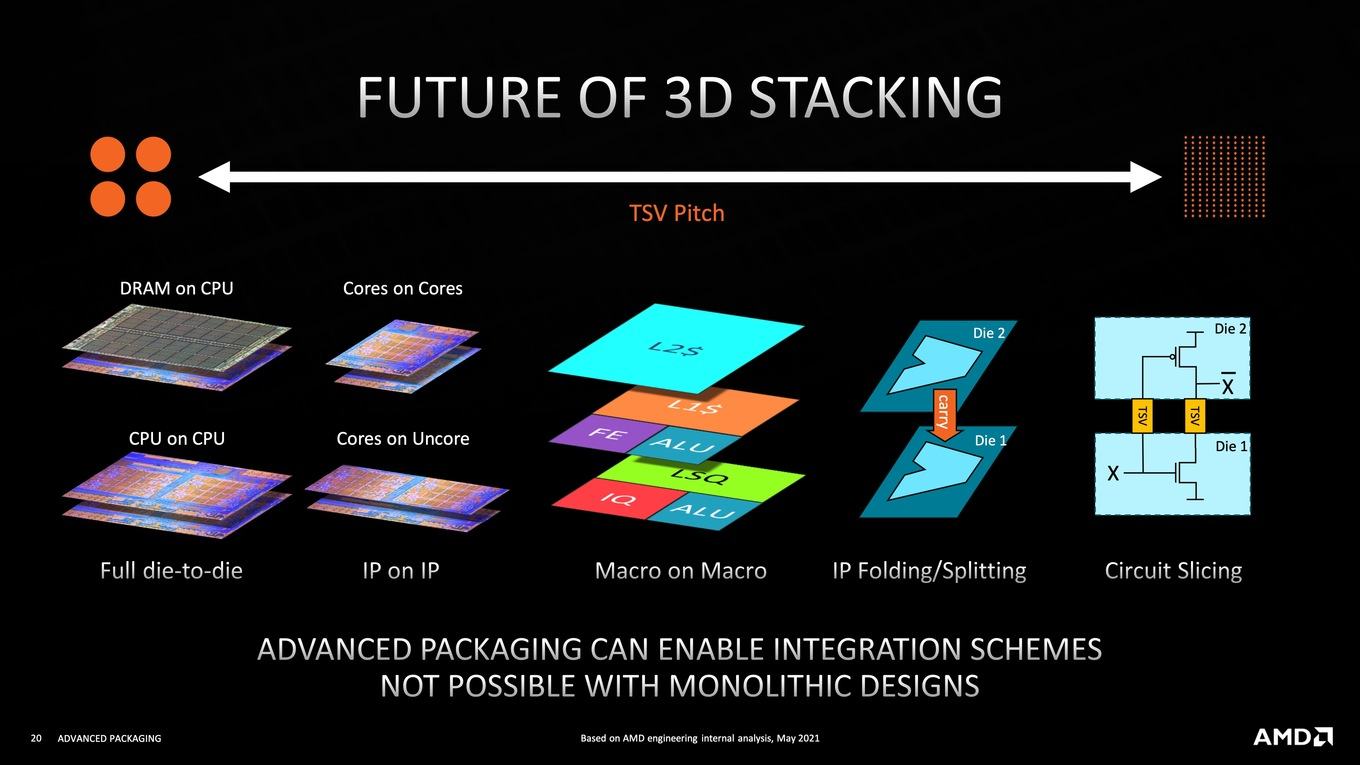

Der 3D V-Cache ist aber nur ein erster Schritt ins AMDs Plänen zum 3D Stacking. Die nächsten Schritte umfassen nicht mehr nur das Stapeln eines Cache-Level, sondern der DRAM soll direkt auf den CPU-Kernen gestapelt werden. Im gleiche Zuge wäre es dann möglich CPUs übereinander zu stapeln – Die on Die. In einem nächsten Schritt denkt man bei AMD darüber nach einzelne Kerne übereinander zu positionieren, ebenso wie Kerne über einem Uncore-Bereich eines Prozessors gestapelt werden könnten. Ähnliches machte bereits Intel mit Lakefield. Macro on Macro würde bedeutet, dass einzelne Kerne in einen 3D-Kern aufgeteilt werden. Die eigentlichen Recheneinheiten sitzen auf einer Ebene, die Caches können ebenfalls auf verschiedene Ebenen aufgeteilt werden. Ab hier wird es dann interessant, welchen Einfluss die Latenz auf die TSV-Verbindungen hat.

Ein weiterer Zukunft wäre es dann denkbar IP-Bereiche oder sogar einzelne Schaltungen zu stapeln. Dies läuft dann auf unzählige Ebenen hinaus, die gestapelt werden, damit dies ein der Praxis auch Vorteile hervorbringen kann. Aber alles ab Macro on Macro liegt noch in weiter Zukunft. Eine erste Herausforderung (nach der Fertigung der Chips und dem Packaging dieser) ist die Kühlung. DRAM über Kernen oder CPU on CPU sind eine Herausforderung für die Kühlung. An einer Lösung scheint TSMC aber ebenfalls bereits zu arbeiten.