Werbung

Der Start der ersten EPYC-Prozessoren mit 3D V-Cache rückt offenbar immer näher, denn nach dem Auftauchen der ersten Produktnamen gibt es nun weitere Details zu den ersten Modellen – vor allem zur Größe des zusätzlichen Caches.

Demnach plant AMD vier Modelle, die mit 16, 24, 32 und 64 Kernen ausgestattet sind und damit hinsichtlich der Anzahl der Kerne die aktuelle Produktpalette abdecken. Der L3-Cache wächst für diese Modelle allerdings von derzeit maximal vorhandenen 256 MB auf satte 768 MB an - eine Verdreifachung.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen

Diese 768 MB an L3-Cache entsprächen der Mindestkonfiguration des 3D V-Caches. AMD präsentierte die Chiplet-Speichererweiterung anhand eines SRAM-Dies, der auf dem CCD platziert wird. Pro CCD kann der L3-Cache von 32 MB ausgehend um weitere 64 MB ausgebaut werden. Für einen EPYC-Prozessor mit acht CCDs bedeutet dies 8 x 32 MB im CCD + 8x 64 MB zusätzlicher 3D V-Cache was in 768 MB insgesamt resultiert.

| Kerne | Basis/Boost-Takt | L3-Cache | TDP | |

| EPYC 7773X | 64 | 2,2 / 3,5 GHz | 768 MB | 280 W |

| EPYC 7763 | 64 | 2,45 / 3,5 GHz | 256 MB | 280 W |

| EPYC 7573X | 32 | 2,8 / 3,6 GHz | 768 MB | 280 W |

| EPYC 7543 | 32 | 2,8 / 3,7 GHz | 256 MB | 225 W |

| EPYC 7473X | 24 | 2,8 / 3,7 GHz | 768 MB | 240 W |

| EPYC 7443 | 24 | 2,85 / 4,0 GHz | 128 MB | 200 W |

| EPYC 7373X | 16 | 3,05 / 3,8 GHz | 768 MB | 240 W |

| EPYC 7343 | 16 | 3,5 / 4,0 GHz | 128 MB | 240 W |

In der Tabelle haben wir die neuen Milan-X-Modelle mit 3D V-Cache gegen die bestehende Milan-Serie gestellt – oder zumindest versucht recht ähnliche Modelle zu finden und zu vergleichen. Das neue Spitzenmodell EPYC 7773X käme demnach auf einen etwas geringeren Basis-Takt, beim Boost aber ebenfalls auf 3,5 GHz. Die TDP bleibt bei 280 W, denn die neuen Prozessoren sollen Sockel-kompatibel bleiben. Der geringere Basis-Takt bei gleicher TDP könnte durch den zusätzlichen Verbrauch des 3D V-Cache erklärt werden.

Der EPYC 7373X mit 32 Kernen ist im Vergleich zum EPYC 7543 nur im Boost etwas langsamer, liegt mit einer TDP von 280 W aber gut 55 W über dem Modell ohne den 3D V-Cache. Auch beim EPYC 7473X sehen wir im Vergleich zum 7443 einen fast identischen Basis-Takt, die TDP fällt aber um 40 W höher aus. Schlussendlich liegt der EPYC 7373X hinsichtlich der TDP gleichauf mit dem EPYC 7343, der Basis-Takt fällt aber um fast 500 MHz geringer aus.

Alles in allem lägen die Taktraten und der Verbrauch im Zusammenspiel aber im Rahmen dessen, was zu erwarten gewesen ist. Die Milan-X-Prozessoren sind eine Sonderserie, die vor allem für Anwendungen und Anwender interessant sind, die vom zusätzlichen 3D V-Cache Gebrauch machen können.

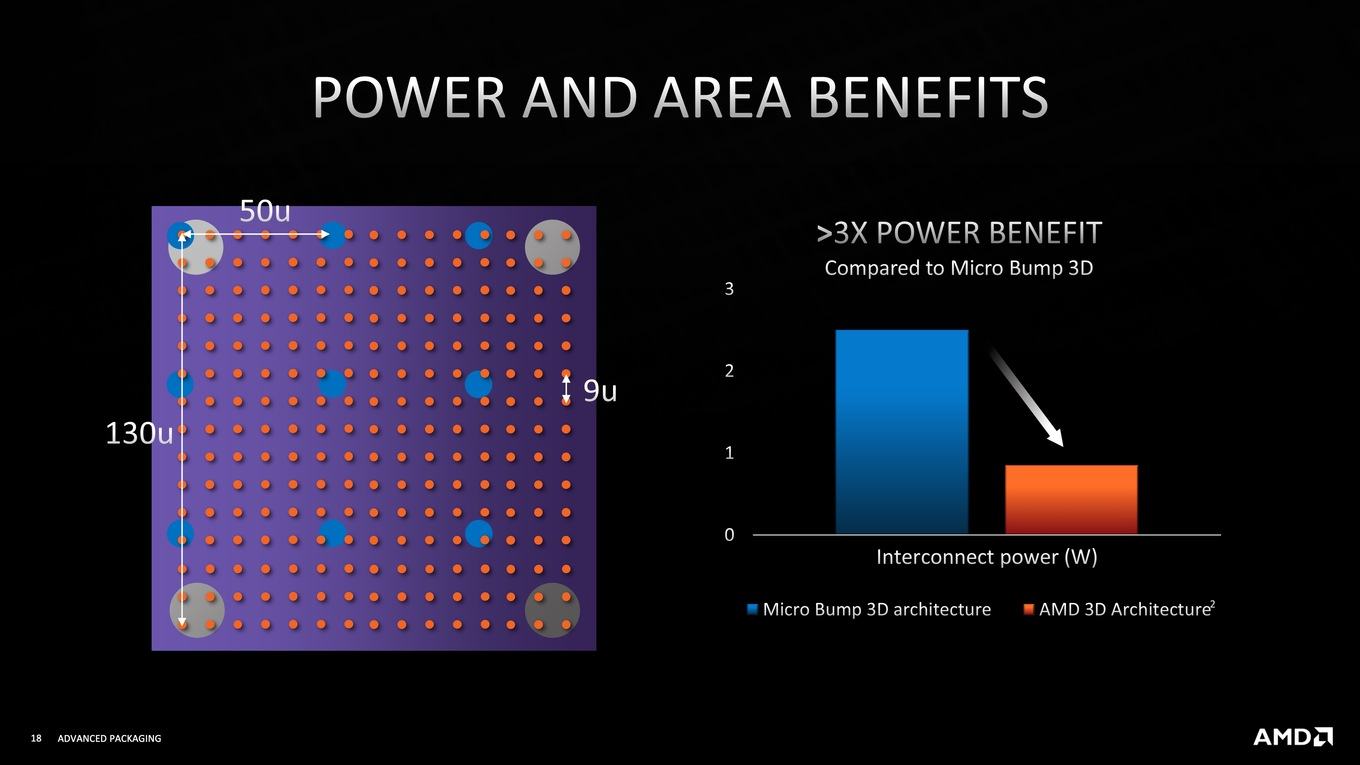

Auf der HotChips-Konferenz verriet AMD einige Details zur Fertigung des 3D V-Cache. Unter anderem liegen die Abstände der TSVs (Through-Silicon Via) für die physikalische Anbindung des SRAM-Dies bei gerade einmal 9 µm. Analysen des aktuellen CCDs, der ja schon für den Einsatz mit dem 3D V-Cache vorbereitet ist, kamen auf 17 µm. Beide Zahlen sind extrem beeindruckend, denn zum Vergleich: Intels Packaging-Techniken EMIB (Embedded Multi-die Interconnect Bridge) der ersten und zweiten Generation kommen auf 55 bzw. 45 µm.

Milan-X mit 768 MB sind aber nur der erste Schritt, denn hier verwendet AMD nur eine Lage des SRAM. Diesen kann der Hersteller aber auch mehrlagig auslegen, sodass sich die Kapazität immer wieder verdoppelt. Unser Server-System von AMD bzw. das BIOS, welches wir im Rahmen des Tests der 7003-Serie verwendet haben, zeigte sogar Einträge für vier Stacks. Mit zwei bzw. vier Stacks würde sich die Kapazität des 3D V-Cache also abermals verdoppeln bzw. vervierfachen. Wir sprächen dann insgesamt von 1.280 MB bzw. 2.304 MB L3-Cache.

Im Vergleich zu den von Intel vorgestellten Xeon-Prozessoren auf Basis von Sapphire Rapids, die teilweise mit HBM ausgestattet sein werden, ist eine Kapazität von 768 MB, 1 GB oder 2 GB nicht besonders hoch, dafür aber ist die Anbindung extrem schnell und sparsam. Mit wie viel Speicher Intel die Xeon-Prozessoren der nächsten Generation ausstatten wird, ist noch nicht bekannt.

Wann AMD die Milan-X-Modelle offiziell vorstellen wird, ist ebenfalls unklar. Die Supercomputing 21 vom 14. bis 19. November wären ein denkbarer Termin für eine Vorstellung.