Werbung

Im Sommer präsentierte Intel nicht nur seine IDM-2.0-Strategie und benannte seine Fertigungsgrößen um, sondern gab außerdem einen Ausblick auf das, was uns ab 2024/25 erwarten wird. Neue Entwicklungen im Bereich der Materialforschung bilden meist die Basis für all das, was dann im einzelnen Transistor, über gestapelte Transistoren, im Aufbau des CMOS-Designs bis hin zum Packaging zum Einsatz kommt.

Auf dem International Electron Devices Meeting (IEDM) sprach Intel nun über Forschung und Entwicklung, die aktuell betrieben wird. Zunächst aber noch einmal ein kleiner Rückblick auf das, was Intel bereits als Zukunft für sich gezeichnet hat. Als Intel 7 (bisher Enhanced 10 nm SuperFin) werden aktuell die Ice-Lake-SP-, Tiger-Lake- und Alder-Lake-Prozessoren für die Bereiche Server, Mobile und Desktop gefertigt. Die hier verwendeten FinFET-Transistoren sollen noch über Intel 4 (7 nm) und Intel 3 (5 nm) zum Einsatz kommen.

Dann wechselt Intel in die Ångström-Ära, wenngleich hier noch klassische FinFET-Transistoren zum Einsatz kommen. Ab Intel 20A – ganz sicher aber ab Intel 18A – also ab 2025, sollen dann Gate-All-Around-Transistoren (GAA) verwendet werden.

Im Rahmen der Vorstellung einiger Forschungsergebnisse auf dem IEDM 2021 ordnet Intel diese Entwicklungen drei Bereichen zu: "Essential Scaling Technologies" (Entwicklung neuartiger Transistoren, in der Lithografie und im Packaging), "Bringing New Capabilities to Silicon" (Weiterentwicklungen im Bereich der integrierten Strom- und Spannungsversorgung, neue Speichertechnologien und Materialforschung) sowie "New Concepts in Physics" (die Suche nach völlig neuen Konzepten im Computing).

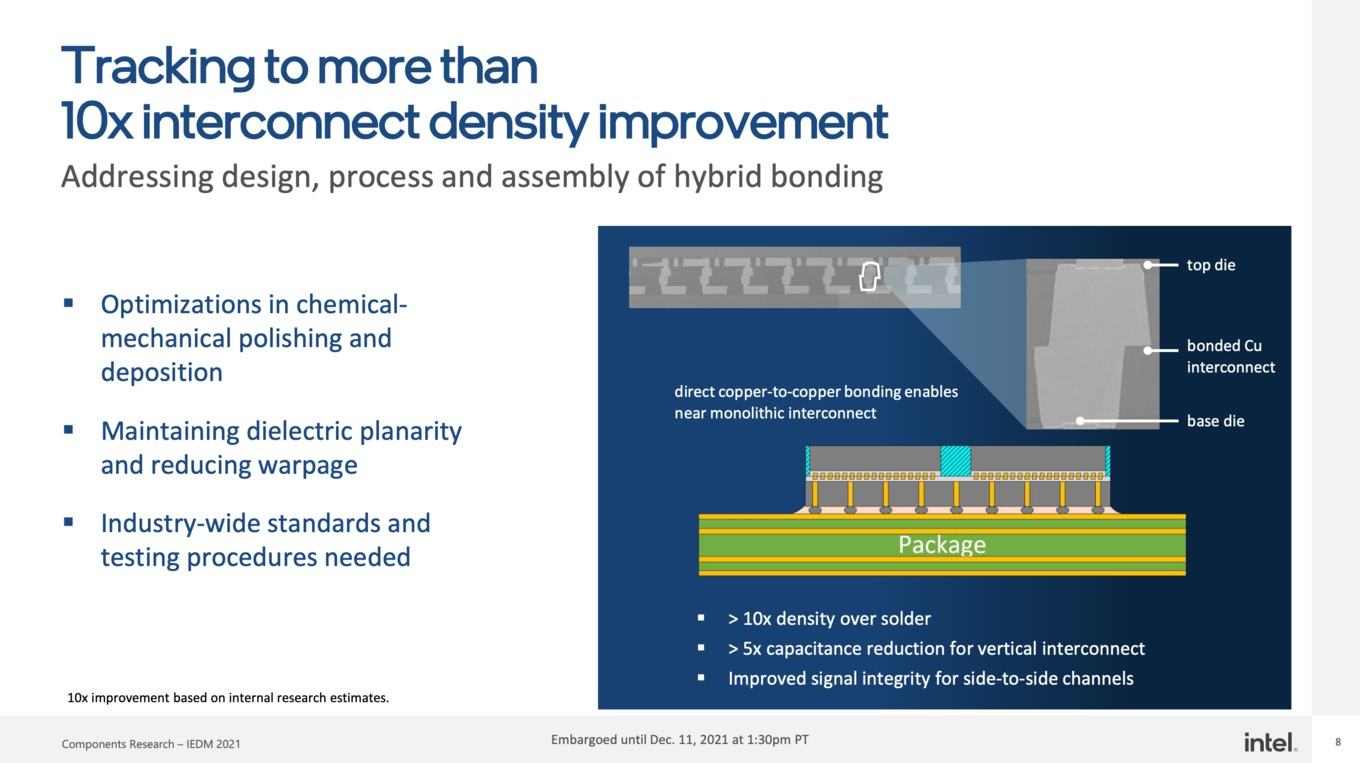

Aktuell bereits konkret in der Umsetzung ist das Packaging mittels Foveros Omni – die direkt Verbindung mehreren Tiles in einem 2.5D-Stacking). Als Foveros Direct soll in einem nächsten Schritt mehrere Chips (mindestens zwei) über direkte Kupferverbindungen miteinander kontaktiert werden. Der Abstand zwischen den Kontaktpunkten beträgt nur noch 10 µm und ermöglich somit 10.000 Kontakte auf einer Fläche von nur einem Quadratmillimeter. Foveros Direct erinnert stark an das Stapeln von SRAM, wie es AMD für den 3D V-Cache verwendet. Dahinter verbirgt sich das Chip-Stacking SoIC von TSMC

Die Schwierigkeit dabei ist zunächst einmal die korrekte Ausrichtung der Dies, so dass auch alle Kontakte korrekt ausgeführt sind. Zudem muss die Signalintegrität gewährleistet werden können, wenn viele derartige Verbindungen dicht zusammengepackt werden.

Der HPC-Beschleuniger Ponte Vecchio wird als erster Chip Foveros der ersten Generation und EMIB der zweiten Generation verwenden. Die Sapphire Rapids Xeon-Prozessoren verwenden EMIB der zweiten Generation. Für Chips, die in Intel 4 und Intel 3 gefertigt werden sollen, dürfte dann auch Foveros Omni und Foveros Direct zum Einsatz kommen.

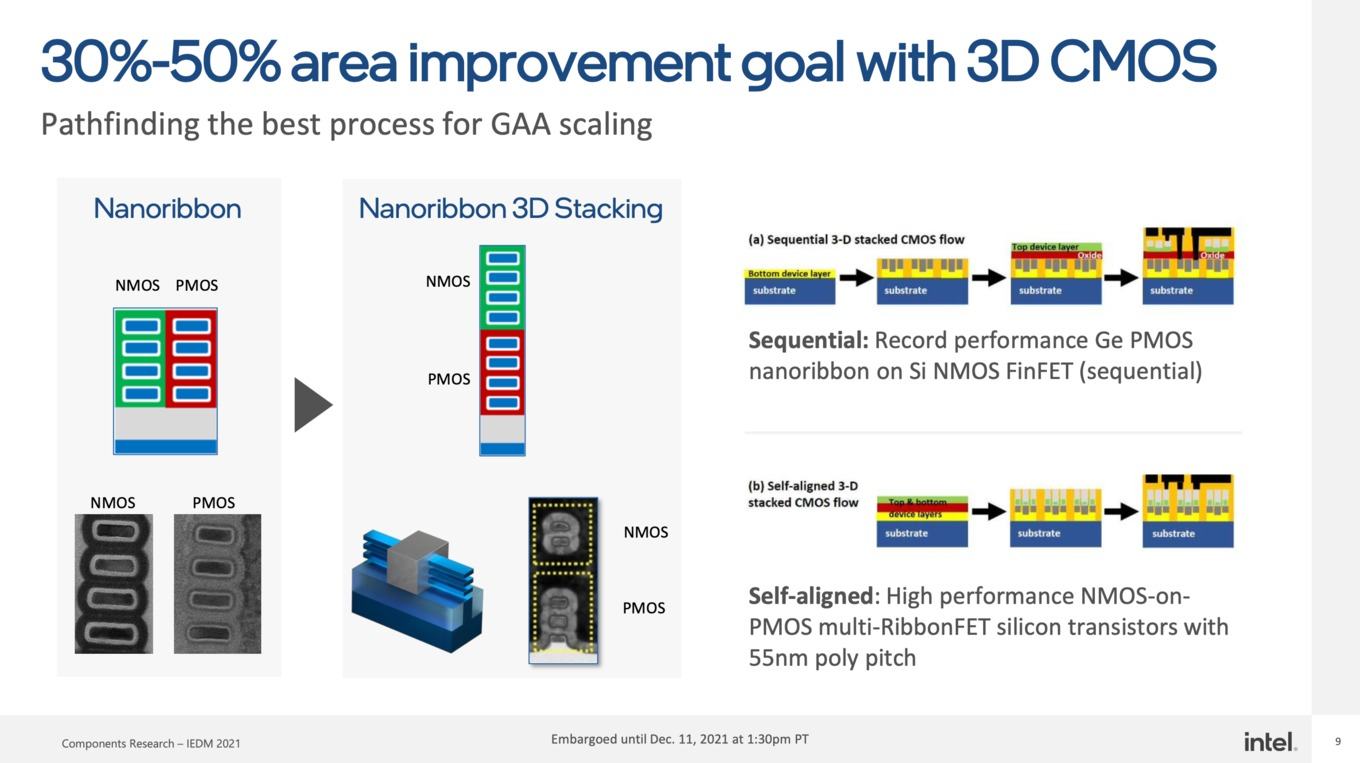

Die erste Generation der GAA-Transistoren wird aus NMOS- und PMOS-Halbleitern bestehen, deren Gates auf allen vier Seiten um ultradünne Kanäle gewickelt sind. Diese verbesserte Gate-Steuerung des Kanals überwindet die physikalischen Skalierungs- und Leistungsbeschränkungen von FinFETs und ermöglicht eine weitere Skalierung der Versorgungsspannung. Ein weiterer Vorteil der GAA-Transistoren ist, dass diese den gleichen Strom schalten können, wie dies sonst mehrere FinFETs tun und das auf einer kleineren Fläche. Über die breite der Gates, die in der Fertigung variable sind, können die GAA-Transistoren in den Eigenschaften angepasst werden.

In einem weiteren Schritt will Intel diese NMOS- und PMOS-Bauteile übereinander gestapelt. Alleine über diese Maßnahme soll die Fläche auf dem Chip um 30 bis 50 % besser genutzt werden. Intel arbeitet hier gerade an verschiedenen Methoden die NMOS- und PMOS-Halbleiter übereinander zu stapeln. Hier gibt es sequentielle Prozessschritte für Germanium-PMOS-GAA-Transistoren auf Silizium-NMOS-FinFETs oder selbstausrichtende NMOS- und PMOS-GAA-Transistoren mit einem Poly Pitch (Abstand zwischen den Gates) von 55 nm.

Bis wir GAA-Transistoren und vor allem 3D-GAA-Transistoren in den ersten Prozessoren sehen werden, werden noch einige Jahre vergehen.

Nicht alle Transistoren sind gleich und eignen sich für alle Anwendungsbereiche in der Halbleiertechnik. Selbst in einem Prozessor gibt es unterschiedliche Auslegungen – je nachdem in welchem Bereich des Chips die jeweiligen Transistoren zum Einsatz kommen.

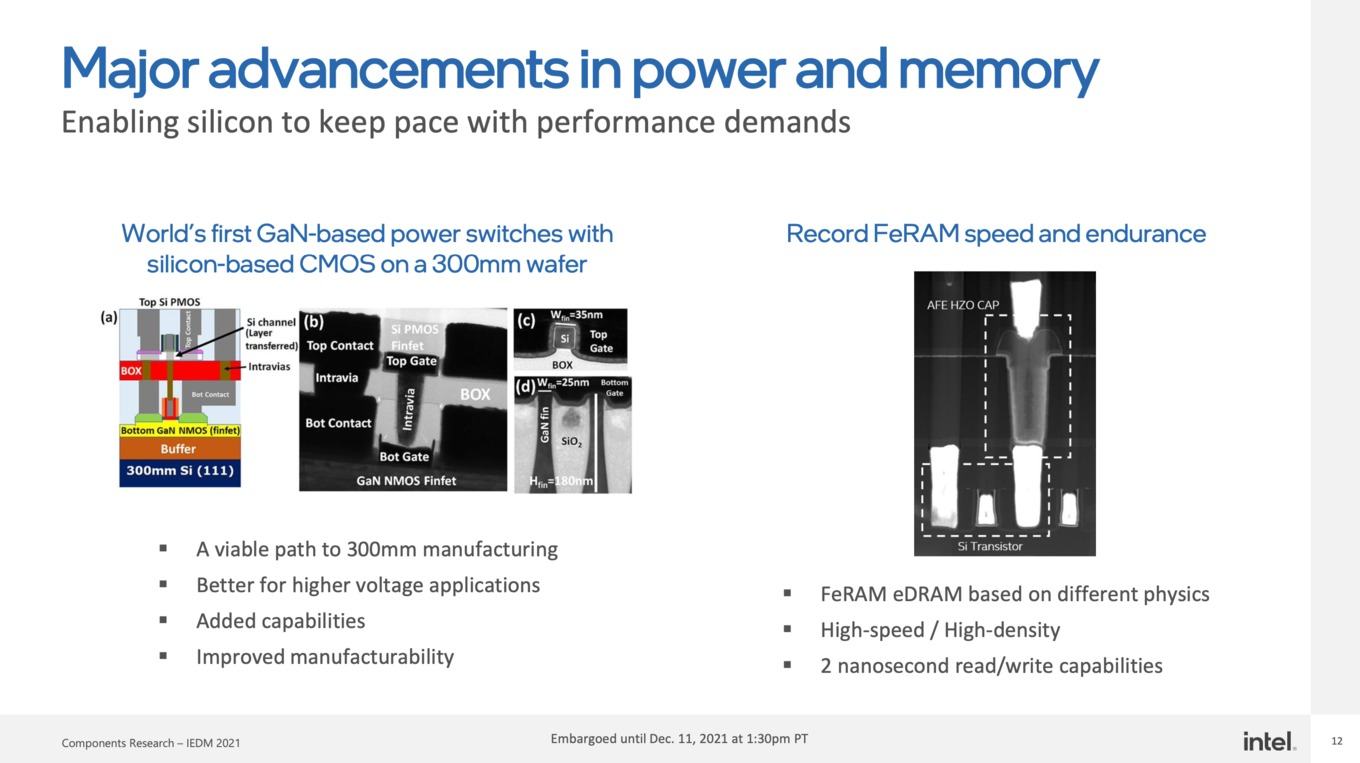

Auf dem IEDM 2021 zeigte Intel erstmals GaN Power Switches (Galliumnitrid), die auf PMOS-Transistor aus Silizium platziert wurden und dies gefertigt auf einem 300-mm-Wafer. Diese GaN Power Switches beeinflussen die Spannungsversorgung der Transistoren in der Art, dass diese für höhere Spannungen ausgelegt sind. RF-Anwendungen, direkt integriert im Chip, sind ein Anwendungsbereich für GaN Power Switches auf Si CMOS. Aktuell eigenen sich GaN Power Switches aber noch nicht im Low-Power-Bereich.

Daneben arbeitet Intel an der Integration von FeRAM (Ferroelectric Random Access Memory). FeRAM kann unabhängig von der Fertigungsgröße deutlich kompakter hergestellt werden, als dies für SRAM der Fall ist. Da die zukünftigen Prozessoren immer mehr SRAM enthalten werden und FeRAM zudem schneller ist, zeigt man sich bei Intel natürlich bestrebt, die Integration von FeRAM schnellstmöglich umsetzen zu können. Mit Latenzen im Bereich von 2 ns liegt man hier auf Niveau von L1-Cache, wie er aktuell in den CPU-Kernen zum Einsatz kommt.

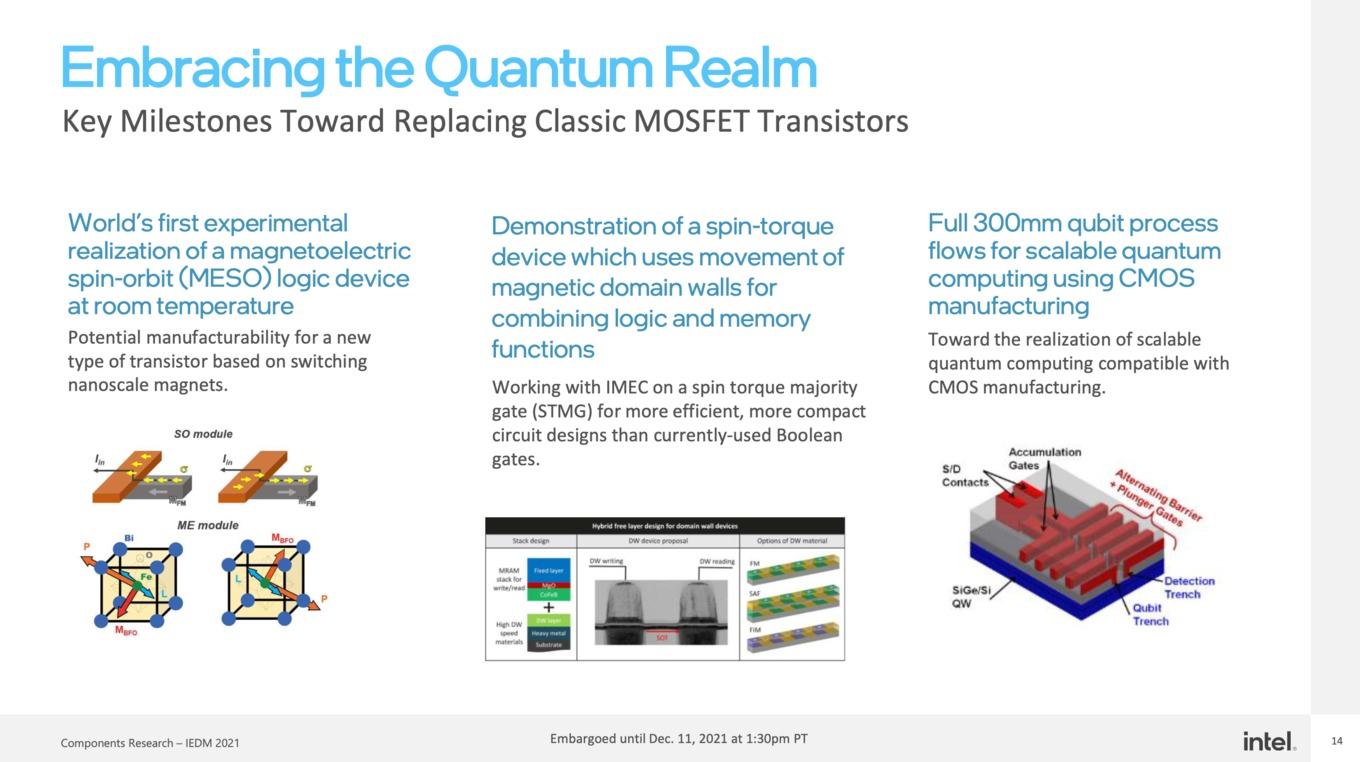

Intel forscht natürlich auch in Bereichen, die mit den uns bekannten Funktionen nur noch sehr wenig zu tun haben. Hier geht es um grundlegend neue Techniken, wie MESO-Logik, die magnetische Spins als Transistor-Typ vorsieht. Diese Spin-Drehmoment-Logik soll völlig neue Methoden zum Aufbau eines Transistors ermöglichen und bewegt sich im Bereich zwischen der aktuellen Halbleitertechnik und dem, was Quantencomputer umsetzen.

Nun muss die Umsetzung folgen

Intels Forschungs- und Entwicklungsabteilung treibt die technischen Limits vor sich her und das nicht erst seit der Präsentation der zahlreichen Arbeiten auf dem IEDM 2021, sondern schon seit Jahrzehnten. Am Ende muss eine solche Forschung jedoch fruchtbare Ergebnisse erzielen und auf eine ökonomisch sinnvolle Art und Weise umgesetzt werden.

Über Jahre hinweg hat sich Intel vor allem in der Fertigung schwer getan. Einige Entscheidungen im Hinblick auf die Fertigung in 10 nm waren offenkundig falsch und führten zu enormen Verzögerungen, die sich bis heute auswirken. Erst mit der aktuell optimierten Fertigung in 10 nm (Intel 7) konnte Intel den Zug wieder auf die Schienen stellen. Die Konkurrenz hat natürlich nicht auf Intel gewartet und so sind Samsung und TSMC zumindest gleichgezogen. AMD konnte in einigen Bereichen in Zusammenarbeit mit TSMC sogar schon deutlich an Intel vorbeiziehen – zumindest aus Sicht der technischen Umsetzung. AMDs 3D V-Cache liegt im Hinblick auf die Dichte der Verbindungen auf einem Niveau, welches Intel erst mit Foveros Direct erreichen will.

Mit der Umstellung der FinFETs, wie sie quasi überall aktuell Anwendung finden, auf GAA-Transistoren steht ein großer Umbruch bevor, der in den kommenden Jahren von immer kleineren Fertigungsgrößen begleitet wird. Die Pläne aller Halbleiterhersteller sehen dabei Strukturgrößen vor, die vor einigen Jahren noch als unmöglich galten. Auch deshalb steckt Intel viel Geld in die Forschung – ist damit allerdings nicht allein.