Werbung

Noch ist der bisher wohl einzig geplante Ryzen-Prozessor (Ryzen 7 5800X3D) der aktuellen Generation mit 3D V-Cache nicht auf dem Markt, da nennt AMD auf der ISSCC 2022 einige Details zur Umsetzung, die über das hinaus gehen, was wir bisher schon wissen.

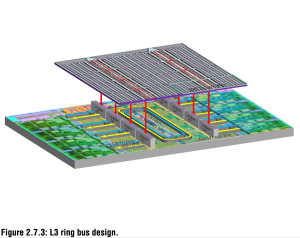

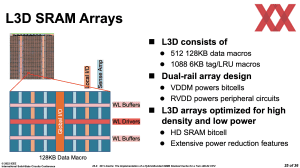

Ein kleiner Rückblick: In der Cache-Hierarchie die größte Änderung in der Zen-3-Architektur sind der gemeinsame L3-Cache mit einer Kapazität von 32 MB für bis zu acht Kerne. Der Core Compute Complex war zuvor in 2x 16 MB aufgeteilt. Damit einher ging auch eine neue Aufteilung in acht statt wie bisher vier Slices (Teilabschnitte) und der dazugehörige Interconnect wurde zu einem bidirektionalen Ringbus mit 32 Byte pro Takt pro Stop am Ringbus (an jedem Kern). Eine höhere Bandbreite bei zugleich niedrigeren Latenzen waren die Folge und tragen dazu bei, dass die Zen-3-Architektur ihre Leistungsziele erreichen konnte. Jedem Kern stehen nun theoretisch die vollen 32 MB an L3-Cache zur Verfügung. Aber auch in der Fertigung des L3-Caches gab es Änderungen. So verwendet AMD nun High Density (HD) Bitcells anstatt der bisher genutzten High Current (HC) Bitcells. Dadurch konnte eine Einsparung in der Fläche um 14 % erreicht werden und die Leakage des Cache Arrays wurde um 24 % reduziert.

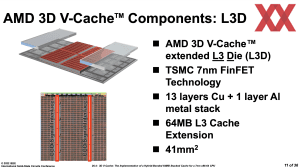

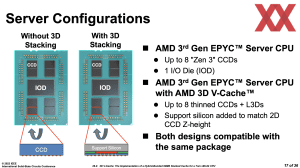

Aber AMD ließ sich auch eine Hintertür offen, die in der Praxis bisher noch keine Rolle spielt. So kann der L3-Cache mittels eines zusätzlichen SRAM-Chips von 32 auf 96 MB erweitert werden. Der nur 36 mm² große Cache-Chip wird auf den L3-Bereich des CCDs gelegt und per Kupfer-Bonding miteinander verbunden. Die reine Adhäsion zwischen den Schnittstellen der beiden Chips reicht schon aus. Ein Verlöten ist nicht notwendig.

Die Verbindung zwischen dem bestehenden Cache Array und dem zusätzlichen Cache wird über TSVs hergestellt. Dazu sieht AMD zwei Reihen an TSV-Verbindungen zwischen den Cache-Blöcken vor. Für jedes 3D-V-Cache-Slide mit 8 MB sieht AMD 1.024 Kontakte vor. Zwischen dem CCX und dem 3D V-Cache sind demnach 8.192 Verbindungen vorhanden.

Das TSV-Interface bietet eine Bandbreite von mehr als 2 TBit/s pro Slice. Der Ringbus des L3-Caches kommt ebenfalls auf mehr als 2 TB/s in beide Richtungen und ermöglicht somit das Bereitstellen der maximalen L3-Cache-Bandbreite für die Kerne – auch mit dem zusätzlichen 3D V-Cache.

Weitere Verbesserungen in der Fertigung

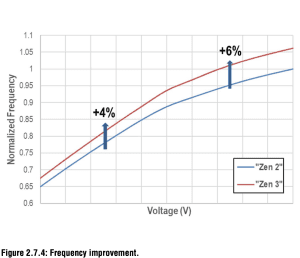

In der Fertigung wurde der Prozess in 7 nm bei TSMC dahingehend optimiert, dass in den 13 Schichten die unteren Layer auf eine hohe Dichte ausgelegt sind und die oberen Layer auf eine möglichst hohe Taktfrequenz. Ziel war eine Erhöhung des Taktes um 4 % bei Beibehaltung der Spannungen. Für die Spitzenleistung im Single-Threaded-Bereich wurden 6 % mehr Spannung ermöglicht.

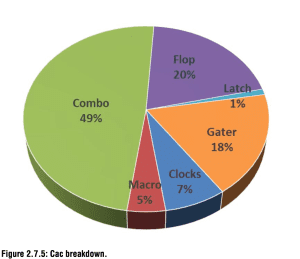

Für Zen 3 versuchte sich AMD aber auch an einer strukturierten Platzierung der Logikblöcke, einer Auswahl an HC- und HD-Zellen und am optimierten Wire-Engineering, um den großen Frequenzanstieg bei hohen Spannungen zu erreichen. Die einzelnen Tiles des Kerns wurden möglichst klein gehalten, um mehrere Design-Iterationen pro Woche zu ermöglichen. Um ein IPC-Plus von 19 % und ein Taktplus von 6 % zu erreichen, musste AMD die CCX Effective Switched Capacitance (Cac) um 15 % erhöhen.

Der Anteil der Cac, die von Taktgattern verbraucht wird, hat sich im Vergleich zur vorherigen Generation leicht erhöht. Hingegen ist der Anteil, der von Flops und kombinatorischer Logik verbraucht wird aufgrund der zusätzlichen Optimierungen der Taktgattereffizienz der Zen-3-Architektur leicht gesunken. Die leicht höhere Leakage wurde durch eine Erhöhung der Frequenz und durch weiteren Verbesserung der Leistungseffizienz aufgewogen.

Bei AMD ist man Stolz auf die Zen-3-Architektur – vor allem auch im Hinblick auf die mögliche Erweiterung der L3-Caches.

Update: Weitere Details

In einer Breakout-Session ist AMD noch etwas genauer auf die Umsetzung des 3D V-Caches eingegangen. Ein kurzer Hinweis: Wir verwenden in der Folge auch häufiger die Begriffe SRAM und L3D. Damit immer gemeint ist die Erweiterung des L3-Caches.

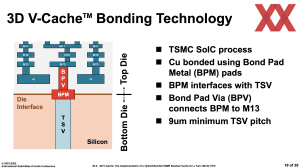

Zunächst einmal erläutert AMD noch einmal die Tatsache, dass das CCD abgeschliffen wurde, damit der SRAM darauf platziert werden kann. Das C4-Interface, also die Verbindungen sind allesamt in Richtung des Trägersubstrats ausgerichtet. Durch das Abschleifen werden die TSVs freigelegt. Auch der SRAM-Chip wird dann "Face-down" auf das CCD aufgelegt. Dort, wo sich kein SRAM befindet, dafür aber die Kerne freiliegen, werden Structural Dies platziert. Bisher kommunizierte AMD eine Größe von 36 mm² ( 6 x 6 mm). Nun ist die Rede von einer Größe von 41 mm² für den SRAM.

AMD verwendet für das Packaging bzw. die Platziert des 3D V-Cache die SoIC-Technik von TSMC. Auf den TSV werden Bond Pad Metal (BPM) Pads aufgebracht. Bond Pad Vias (BPV) verbinden diesen BPM dann mit der untersten der 13. Metallschichten. Auf den CCDs wird noch ein Support Silicon, also ein passives Siliziumelement aufgebracht, damit die CCDs die gleiche Höhe wie der IOD aufweisen.

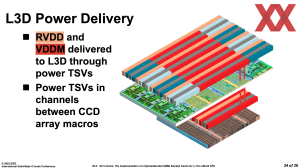

Die Versorgung des SRAM erfolgt ebenfalls über TSVs. Die für die Kerne vorhandene RVDD- und VDDM-Spannungsschienen werden durch die CCDs hindurch in den L3D (SRAM) geführt.

Um die Zugriffe auf den 3D V-Cache auf einem ähnlichen Niveau zu halten, wie dies für den im CCD vorhandenen L3-Cache der Fall ist, teilt AMD den SRAM in 512 Blöcke zu je 128 kB an Daten auf. Zudem gibt es 1.088 6 kB große Tag-Macros, um die Daten entsprechend schnell auffinden zu können. Die Bandbreite soll bei mehr als 2 TB/s liegen. Die Latenzen bei Zugriffen in den erweiterten L3-Cache sollen laut AMD nur vier zusätzliche Taktzyklen betragen.